74LS161计数器的逻辑功能与应用解析

需积分: 18 56 浏览量

更新于2024-07-24

收藏 343KB PPT 举报

"计算机方面知识"

本文将深入探讨计算机科学中的一个重要概念——中规模集成电路计数器,特别是74LS161同步四位二进制计数器。计数器是数字系统的基础组件,用于跟踪时间、序列和其他周期性事件。74LS161是一种常用的CMOS集成电路,广泛应用于各种数字电路设计中。

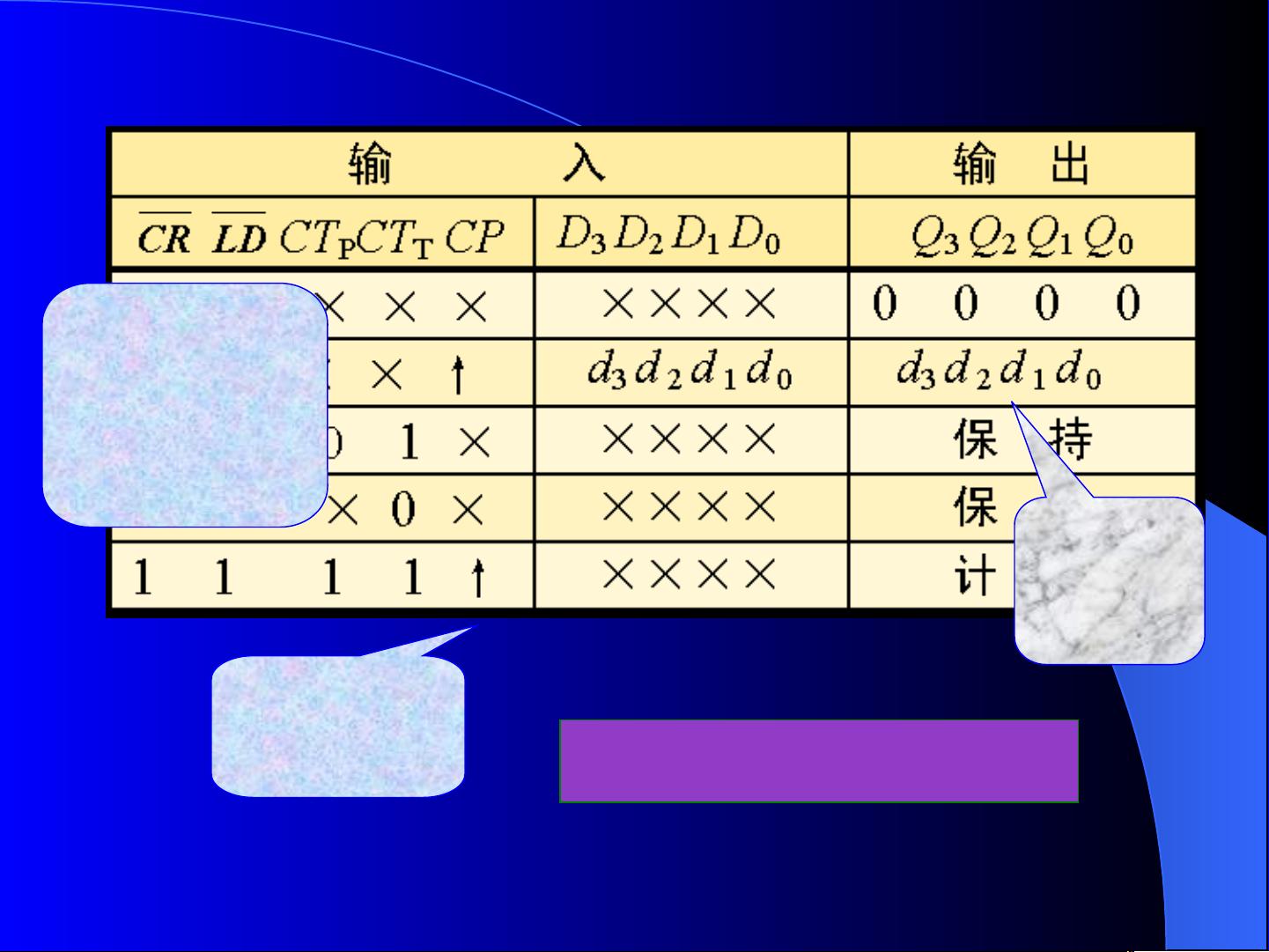

74LS161是一个同步四位二进制计数器,它能够从0计数到15(即2^4 - 1),然后回零,执行二进制加法计数。其逻辑功能包括异步清零和同步并行置数,这使得该计数器能够根据需要快速重置或设置初始计数值。

该计数器有四个主要的输出Q0, Q1, Q2, 和 Q3,它们分别代表二进制计数状态的最低位到最高位。此外,它还有一个进位输出CO,当计数器从15(1111)增加到0(0000)时,CO会变为高电平。74LS161还有两个重要的输入端:时钟脉冲输入CP和清零输入(Clear)。CP上升沿有效,意味着计数操作发生在CP信号的上升沿。异步清零输入则允许在任何时刻立即清零计数器,而同步并行置数功能则允许在CP上升沿时设置计数器的状态。

74LS161的功能表(表5-14)详列了在不同输入条件下的输出状态,而其时序图(图5-22)展示了随着时钟脉冲输入变化,计数器状态的动态演变。这些图形和表格提供了理解其工作原理的关键信息。

74LS161不仅限于二进制计数,还可以扩展用于实现更复杂的计数任务,例如构成16以内的任意进制计数器。这通常通过脉冲反馈法实现,即在特定计数状态时触发置数信号,使计数器返回到预设的起始状态。例如,设计一个十进制计数器,可以利用74LS161的置数功能和进位输出CO来捕获特定状态,如1111,然后将计数器重置为预设的十进制计数序列(0110到1111)。

为了实现不同进制计数,可以通过改变与非门的输入信号来调整74LS161的D输入(D3D2D1D0),这样可以构造出从特定数值开始的计数器,如图5-24所示的从0开始的十进制计数器。

总结来说,74LS161是一个多功能的计数器芯片,它的灵活性和实用性使其在计算机科学和电子工程领域具有广泛的应用。了解并掌握74LS161的工作原理和应用方法,对于学习计算机硬件和数字逻辑设计至关重要。

2021-10-02 上传

2021-10-14 上传

2021-10-10 上传

2024-11-27 上传

2024-11-27 上传

2024-11-27 上传

2024-11-27 上传

2024-11-27 上传

云莫

- 粉丝: 0

- 资源: 1

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查