ALTERA CYCLONE III FPGA接口电路设计详解

需积分: 50 15 浏览量

更新于2024-09-13

收藏 2.24MB PDF 举报

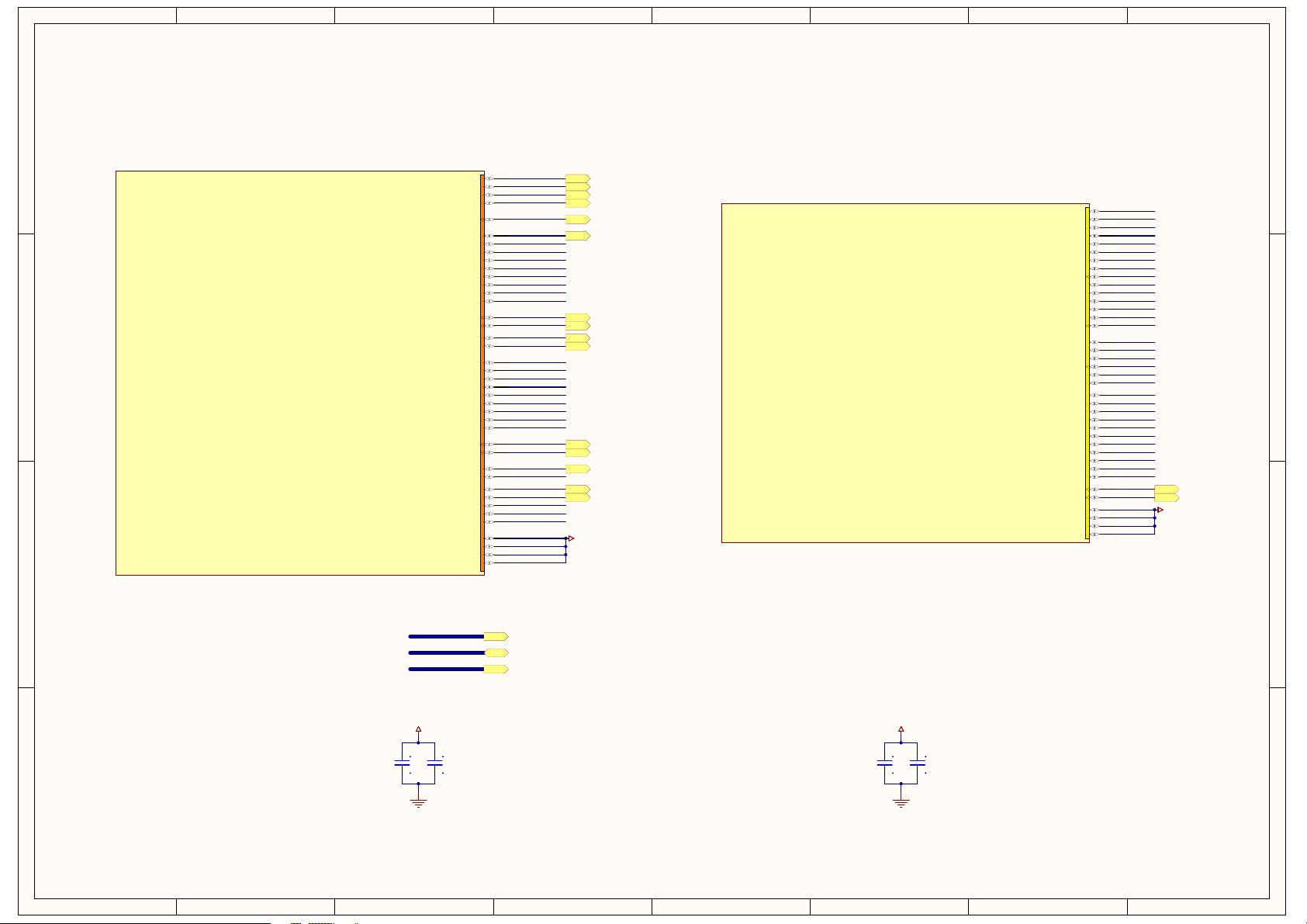

"ALTERA CYCLONE III FPGA的原理参考电路图,适用于EP3C40F484型号,提供了完整的接口连接示例,包括DDR、SRAM、FLASH和其他控制信号的布局。"

ALTERA的Cyclone III系列是Altera公司推出的一款FPGA(Field-Programmable Gate Array)产品,主要应用于各种数字逻辑设计,如嵌入式系统、通信设备、图像处理等。EP3C40F484是这一系列中的一个具体型号,具有40,160个逻辑单元(LEs)和484个I/O引脚。

该原理图详细展示了EP3C40F484 FPGA如何与外部器件进行连接,包括以下几个关键部分:

1. **DDR内存接口**:DDR(Double Data Rate)内存是高速同步动态随机访问内存,用于提高数据传输速率。图中列出了DDR的相关信号线,如DDR_CLK_p/n(时钟),DDR_CKE(时钟使能),DDR_BA(bank地址),DDR_WE_n(写使能),DDR_CAS_n/RAS_n(行/列地址选通),DDR_CS_n(片选),DDR_DQ(数据总线),DDR_DM(数据掩码),以及配置信号。

2. **SRAM接口**:静态随机存取存储器,用于快速存取数据。图中包含了SRAM的控制信号如WE_n(写使能),CE_n(片选),OE_n(输出使能),BE_n(字节使能),CLK(时钟)以及数据线DQ和地址线A。

3. **FLASH存储器接口**:FLASH存储器用于非易失性存储数据。图中包含了FLASH的相关信号,如CLK(时钟),ADV_n(先进先出信号),CE_n/OE_n/RESET_n/WE_n(片选/输出使能/复位/写使能),以及数据线DQ和地址线A。

4. **测试接口**:JTAG(Joint Test Action Group)接口用于设备调试,包括TMS(测试模式选择),TCK(测试时钟),TDI(测试数据输入),TDO(测试数据输出)和配置相关信号如nCONFIG,CIII_TDI/TDO,CONF_DONE,nSTATUS,nCE。

5. **其他接口**:包括HSMC(High Speed Memory Controller)时钟输入/输出,用于高速数据传输;LED输出,用于系统状态指示;50MHz时钟输入等。

这份原理图对设计者来说是一份宝贵的参考资料,它详尽地展示了EP3C40F484 FPGA如何与其他组件进行硬件级的交互,帮助工程师理解和实现复杂的系统设计,确保正确连接和高效运行。在实际应用中,理解这些接口及其信号至关重要,因为它们决定了系统性能和稳定性。

2022-09-19 上传

点击了解资源详情

点击了解资源详情

360 浏览量

2010-11-14 上传

215 浏览量

happies_701

- 粉丝: 0

- 资源: 8

最新资源

- 单片机智能手表仿真protues

- xUnitTestOnReplit:xUnit测试重复

- MarksToAndroid,安卓或Java.zip

- contrastive-analysis--list:实时改变数值,进行对比储存列表里面的数据

- 医疗图标 .fig .xd .sketch .svg素材下载

- AD7708_C51,c语言的源码可以跨平台吗,c语言

- vuebersicht:用电子,TypeScript和Vue构建的Uebersicht的重新构想

- 易语言弹力按钮

- 确定颜色的位置 找到红色的区域 火焰识别

- BKAirMonitoringSystem

- 关于我自己

- RESTMock,.zip

- 免费开源!!Java Core Sprout:基础、并发、算法

- ericgautier_2_07012021:P2

- 【毕业设计】FPGA硬件实现触摸、显示屏控制系统(电路图、源代码、毕业论文)-电路方案

- container-ps:显示所有码头工人图像的小应用程序