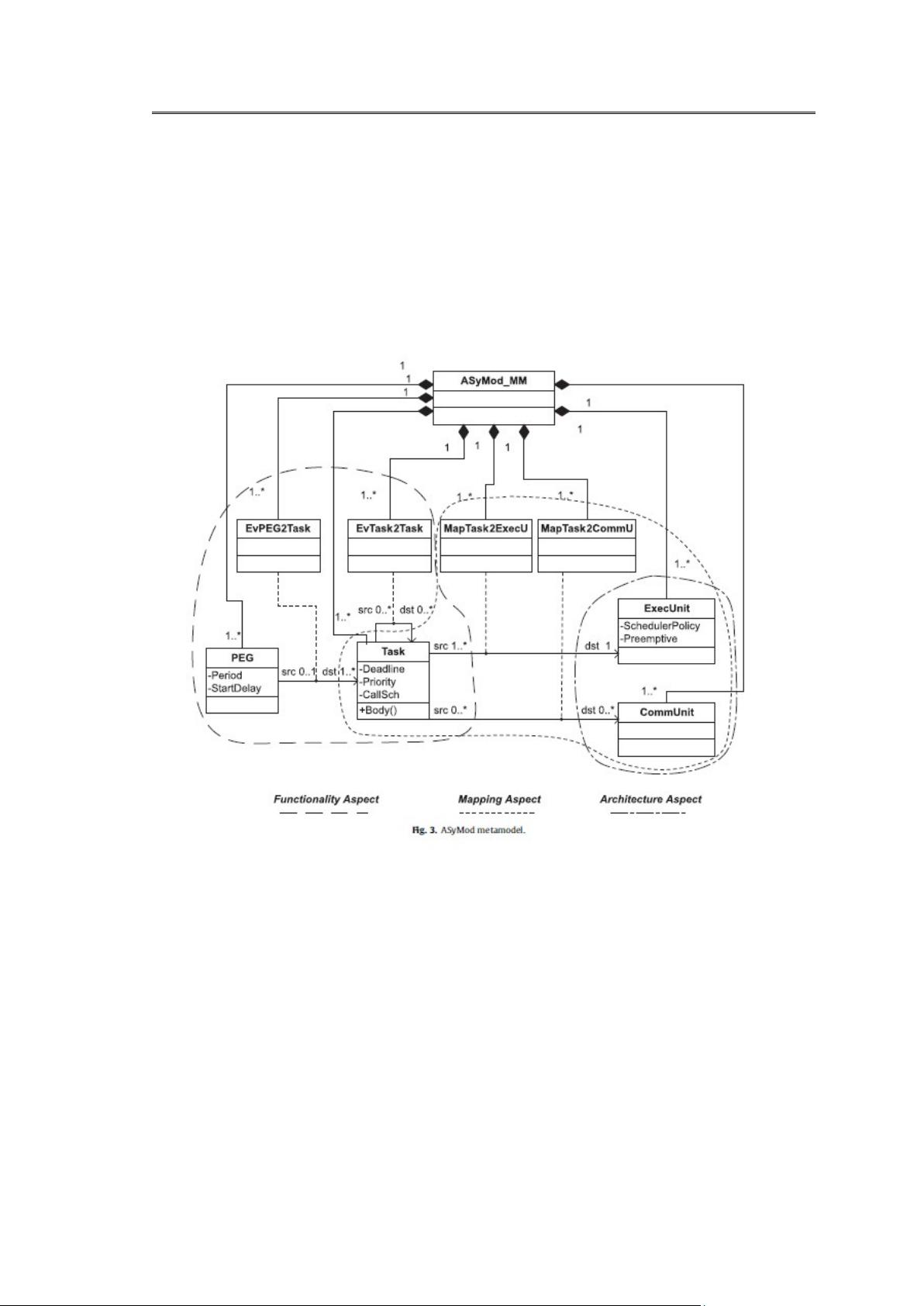

events and SD

An

is the initial delay of the first event. PEGs can also be used for

generating one-time events. In this case, a very long period ST

An

should be set

(beyond the total simulation time) and the delay SD

An

is used to define when an

event should be generated. The ASyMod tasks are event-triggered tasks. An

ASyMod task is composed of a description of the HW resource usage for a

particular piece of the code and RT execution constraints for the deadline and

priority. The task can be expressed with a triple tAn (D

An

, L

An

, B

An

), where

D

An

is the task deadline, L

An

is the task priority and the boolean B

An

defines

whether the scheduler should be called at the end of the task execution. This is

discussed in more detail in Subsection 3.1.1 with a guideline (v). The task

execution can begin if the task is triggered with an event and if the scheduler,

based on the scheduling policy and task RT execution constraints, allows its

execution. After the task execution is finished, the task generates an event. The

task can be triggered by a PEG or by an event generated at the end of the

execution of some other task. The connections in a set Xs

((T

A

× T

A

) ∪ (S ×

T

A

)) define the event flow. Events can be produced by PEGs and by tasks and

consumed only by tasks. Each connection is defined with the pair xs

n

(y

m

, t

An

),

where y

m

defines the event producer (task t

Am

or PEG xs

m

) and t

An

is the event

consumer task. If a task is triggered by another task, this can be recognized as a

sequence of tasks. The period of their execution depends on the PEG that

triggers the first task in this sequence. Depending on this PEG, the tasks in the

sequence can be onek-time or periodically triggered.

2.2.3. Architecture graph in ASyMod

In ASyMod the HW architecture is defined with a concept of abstract

execution units and abstract communication units and information about how

these components are connected together. The HW components that perform

some data computation (e.g., processors, multipliers, filters, etc.) are modelled

as execution units, while the components that perform data transfer and storage