使用SystemVerilog进行处理器验证的方法

需积分: 46 82 浏览量

更新于2024-08-11

收藏 413KB PDF 举报

"这篇文档是关于使用SystemVerilog进行CPU、core和processor验证的一个技术讨论,作者Arthur Freitas在2007年6月发表。文章重点介绍了利用Shadow modeling和覆盖驱动的验证策略来增强处理器的随机测试生成,以确保新世代处理器设计的正确性。"

在CPU验证过程中,尤其是对于复杂的处理器核心(core)和处理器(processor)验证,确保设计的正确性至关重要。SystemVerilog作为一种强大的硬件描述语言,提供了定义设计功能覆盖和应用Shadow modeling技术的方法,大大提升了验证流程的效率。

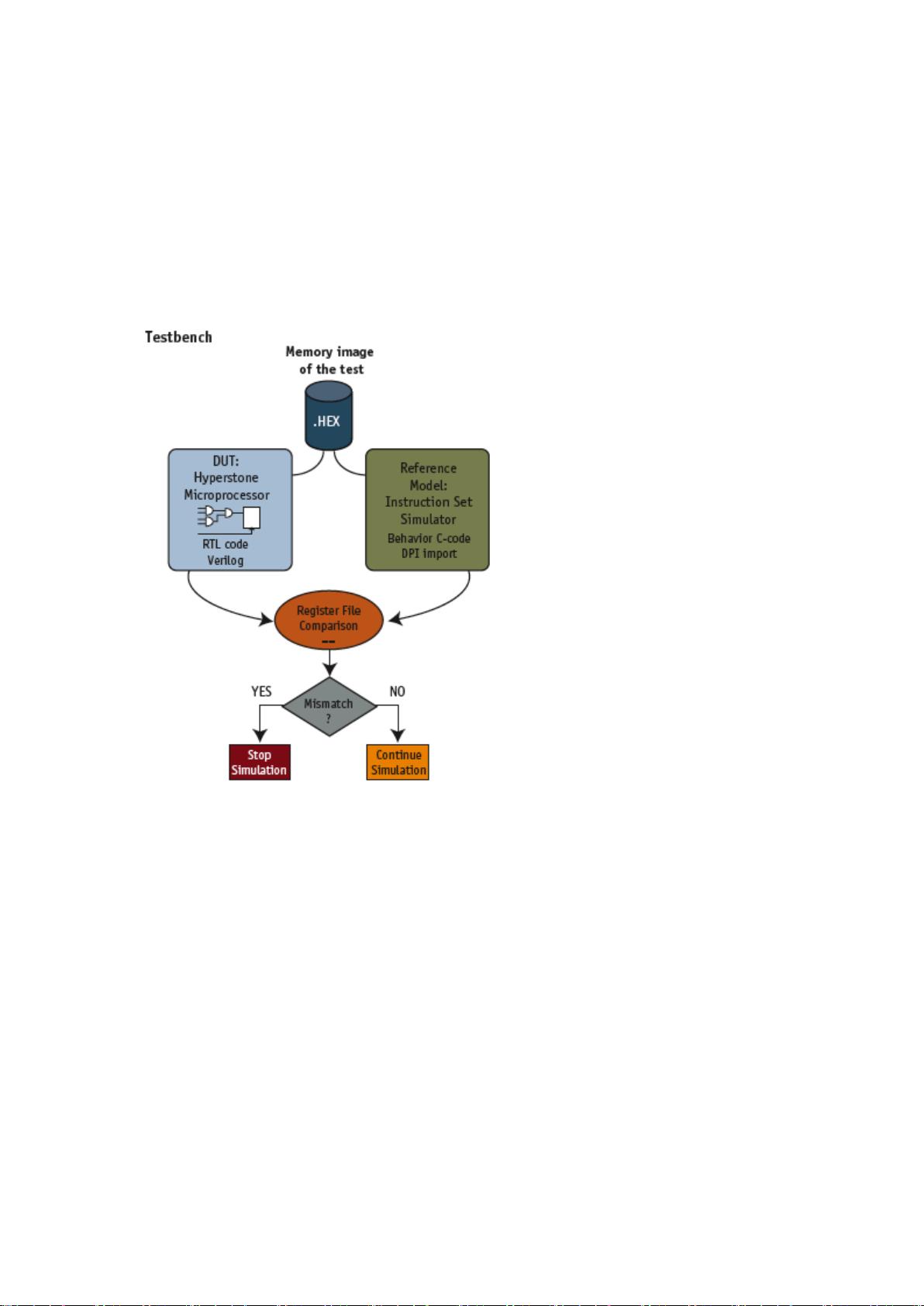

Shadow modeling是一种验证技术,它创建了一个与原始设计并行运行的参考模型,称为阴影模型。这个参考模型通常是一个指令集模拟器(Instruction Set Simulator, ISS),它详尽地描述了微处理器的功能。由于参考模型和RTL(寄存器传输级)由不同的工程师使用不同的编程语言实现,因此两者的错误模式不太可能完全相同,这就为验证设计的正确性提供了一种可靠的方法。

验证策略的核心是随机测试生成,这有助于暴露设计中的潜在问题。通过覆盖驱动的方法,可以确保测试用例能够全面覆盖设计的各种操作和状态,从而提高验证的覆盖率。SystemVerilog的覆盖模型允许工程师定义特定的行为和结构覆盖点,以便更深入地了解设计的行为。

此外,利用已有的ISS作为运行规范,可以避免从头开发验证环境,有效地复用了软件开发的投资。尽管ISS最初不是为了硬件验证而设计的,但它提供了丰富的微处理器行为信息,可以作为验证的基础,使得硬件验证过程更加高效和准确。

在实际应用中,该方法可能包括以下步骤:

1. 定义SystemVerilog的覆盖模型,以捕获处理器设计的关键行为。

2. 创建一个与RTL匹配的阴影模型,通常是基于ISS。

3. 使用随机测试向量刺激RTL和阴影模型,同时监控两者的行为是否一致。

4. 分析覆盖报告,确保设计的所有关键路径和功能点都得到了充分测试。

5. 对于未达到覆盖目标的部分,生成更多的测试用例,直到满足预设的覆盖标准。

这篇文档揭示了如何运用高级验证技术,如SystemVerilog和Shadow modeling,来增强处理器设计的验证流程,确保其在物理实现前的逻辑正确性。这种方法不仅可以提高验证的质量,还能减少因设计错误导致的时间和成本损失。

2014-01-10 上传

2009-10-14 上传

2023-08-17 上传

2023-05-25 上传

2023-06-13 上传

2023-05-25 上传

2023-05-27 上传

2023-06-11 上传

ZYPZHOU

- 粉丝: 1

- 资源: 3

最新资源

- Google Test 1.8.x版本压缩包快速下载指南

- Java实现二叉搜索树的插入与查找功能

- Python库丰富性与数据可视化工具Matplotlib

- MATLAB通信仿真设计源代码与应用解析

- 响应式环保设备网站模板源码下载

- 微信小程序答疑平台完整设计源码案例

- 全元素DFT计算所需赝势UPF文件集合

- Object-C实现的Flutter组件开发详解

- 响应式环境设备网站模板下载 - 恒温恒湿机营销平台

- MATLAB绘图示例与知识点深入探讨

- DzzOffice平台新插件:excalidraw白板功能介绍与使用指南

- Java基础实训教程:电子商城项目开发与实践

- 物业集团管理系统数据库设计项目完整复刻包

- 三五族半导体能带参数计算器:精准模拟与应用

- 毕业论文:基于SSM框架的毕业生跟踪调查反馈系统设计与实现

- 国产化数据库适配:人大金仓与达梦实践教程