5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

HAJ7

HAJ[35..3]

HAJ30

HAJ5

HAJ25

HAJ28

HAJ14

HAJ19

HAJ16

HAJ26

HAJ6

HAJ3

HAJ24

HAJ20

HAJ31

HAJ11

HAJ15

HAJ27

HAJ21

HAJ13

HAJ18

HAJ12

HAJ23

HAJ8

HAJ[35..3]

HAJ22

HAJ10

HAJ4

HAJ17

HAJ9

HAJ29

TP_CPU_J16

TP_CPU_H15

TP_CPU_J17

TP_CPU_H16

CPU_GTLREF1

TP_CPU_H4

TP_CPU_AD3

BPMB2J

BPMB3J

TESTHI_10

HREQJ0

HREQJ1

HREQJ2

HREQJ4

HREQJ3

HDJ[63..0]

CPU_GTLREF0

HDJ43

HDJ16

HDJ51

HDJ61

HDJ57

HDJ10

HDJ21

HDJ46

HDJ47

HDJ27

HDJ37

HDJ31

HDJ11

HDJ36

HDJ8

HDJ39

HDJ4

HDJ56

HDJ14

HDJ23

HDJ53

HDJ60

HDJ9

HDJ15

HDJ20

HDJ50

HDJ5

HDJ26

HDJ12

HDJ38

HDJ59

HDJ42

HDJ45

HDJ30

HDJ3

HDJ55

HDJ62

HDJ7

HDJ1

HDJ17

HDJ41

HDJ2

HDJ33

HDJ58

HDJ25

HDJ6

HDJ28

HDJ40

HDJ22

HDJ52

HDJ18

HDJ13

HDJ48

HDJ54

HDJ63

HDJ19

HDJ35

HDJ24

HDJ49

HDJ44

HDJ0

HDJ34

HDJ32

HDJ29

HAJ34

HAJ32

HAJ33

HAJ35

CPU_GTLREF0_DIVIDER

CPU_GTLREF3CPU_GTLREF3_DIVIDER

CPU_GTLREF1CPU_GTLREF1_DIVIDER

CPU_GTLREF0_DIVIDER

CPU_GTLREF2_DIVIDER

CPU_GTLREF0

CPU_GTLREF2

TP_CPU_N4

TP_CPU_P5

TP_CPU_AC4

TP_CPU_AE4

CPU_GTLREF3

TP_CPU_AB3

TP_CPU_U2

TP_CPU_U3

HBR0J

TP_CPU_H29

TP_CPU_E24

BPMB0J

BPMB1J

CPU_GTLREF2CPU_GTLREF2_DIVIDER

VTT_OUT_RIGHT VTT_OUT_LEFT

VTT_OUT_LEFT

12V_SYS

3D3V_SB

12V_SYS

VTT_OUT_RIGHT

3D3V_SYS

HAJ[35..3]12

HAJ[35..3]12

HADSJ 12

HBNRJ 12

HITJ 12

INITJ 24

HBPRIJ 12

HDBSYJ 12

HDRDYJ 12

HITMJ 12

HLOCKJ 12

HTRDYJ 12

HDEFERJ 12

HADSTBJ012

HADSTBJ112

HREQJ[4..0]12

HDJ[63..0] 12

HDBIJ012

HDSTBNJ012

HDSTBPJ012

HDSTBNJ112

HDSTBPJ112

HDBIJ112

HDSTBNJ3 12

HDSTBPJ3 12

HDBIJ3 12

HDSTBNJ2 12

HDSTBPJ2 12

HDBIJ2 12

TESTHI_10 10

BPMB2J 10

BPMB3J 10

HIERRJ 10

CPU_GTLREF_CTRL123

CPU_GTLREF_CTRL223

HRSJ0 12

HRSJ1 12

HRSJ2 12

HCPURSTJ 8,10,12

HBR0J 10,12

BPMB0J 10

BPMB1J 10

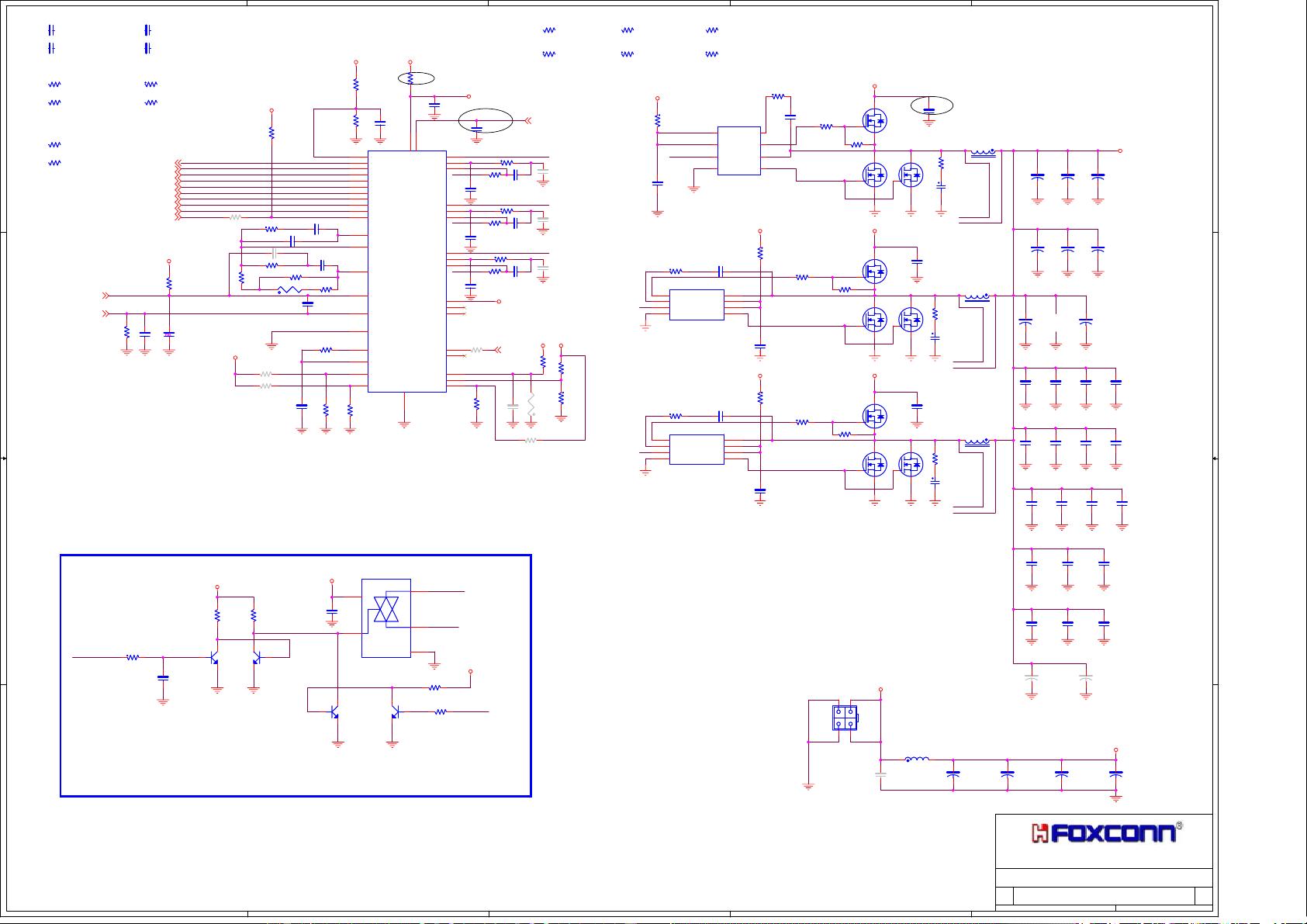

Title

Size Document Number Rev

Date: Sheet

of

FOXCONN PCEG

G43M01S1

AC

941Monday, August 11, 2008

LGA775 -1

Title

Size Document Number Rev

Date: Sheet

of

FOXCONN PCEG

G43M01S1

AC

941Monday, August 11, 2008

LGA775 -1

Title

Size Document Number Rev

Date: Sheet

of

FOXCONN PCEG

G43M01S1

AC

941Monday, August 11, 2008

LGA775 -1

GTLREF voltage should be 0.67*VTT

12 mils width, 15 mils spacing

divider should be within 1.5" of the GTLREF pin

0.22nF caps should be placed near CPU pin

place series resistor as close to divider

Reserved for CPU_GTLREF Adjusting(Double check)

Old:

GP20(CPU_GTLREF_CTRL2) is used

as funcitonal strap.

1. The status is Low during Reset.

2. The status is High after Reset.

New:

ICH_GPIO32: Default GPO, Core Power

ICH_GPIO60 is OD output

TP11TP11

TP9TP9

TP24TP24

TP6TP6

*

R340

0

*

R340

0

TP15TP15

Q44

2N7002

Q44

2N7002

G

DS

TP43TP43

TP5TP5

TP36TP36

Q47

MMBT3904-7-F

Q47

MMBT3904-7-F

B

E C

*

R342 10

Dummy

*

R342 10

Dummy

1 OF 7

U2A

Socket-IntelPrescottCPU

1 OF 7

U2A

Socket-IntelPrescottCPU

A03#

L5

A04#

P6

A05#

M5

A06#

L4

A07#

M4

A08#

R4

A09#

T5

A10#

U6

A11#

T4

A12#

U5

A13#

U4

A14#

V5

A15#

V4

A16#

W5

RSVD2

P5

RSVD1

N4

REQ0#

K4

REQ1#

J5

REQ2#

M6

REQ3#

K6

REQ4#

J6

ADSTB0#

R6

A17#

AB6

A18#

W6

A19#

Y6

A20#

Y4

A21#

AA4

A22#

AD6

A23#

AA5

A24#

AB5

A25#

AC5

A26#

AB4

A27#

AF5

A28#

AF4

A29#

AG6

A30#

AG4

A31#

AG5

A32#

AH4

A33#

AH5

A34#

AJ5

A35#

AJ6

RSVD3

AC4

RSVD4

AE4

ADSTB1#

AD5

ADS#

D2

BNR#

C2

HIT#

D4

FC35

H4

BPRI#

G8

DBSY#

B2

DRDY#

C1

HITM#

E4

IERR#

AB2

INIT#

P3

LOCK#

C3

TRDY#

E3

FC36

AD3

DEFER#

G7

FC37

AB3

FC29

U2

FC30

U3

BR0#

F3

BPMB3#

G3

BPMB2#

G4

TESTHI_10

H5

FC31

J16

FC32

H15

FC33

H16

FC34

J17

GTLREF0

H1

RESET#

G23

RS0#

B3

RS1#

F5

RS2#

A3

FC10

E24

GTLREF1

H2

FC15

H29

GTLREF2

F2

GTLREF3

G10

BPMB1#

C9

BPMB0#

G1

*

R375

100 Ohm

+/-1%

Dummy

*

R375

100 Ohm

+/-1%

Dummy

*

C371

1uF

10V, Y5V, +80%/-20%

*

C371

1uF

10V, Y5V, +80%/-20%

*

R440 1K

*

R440 1K

TP53TP53

TP32TP32

*

R387

100 Ohm

+/-1%

*

R387

100 Ohm

+/-1%

TP56TP56

*

C342

220pF

50V, NPO, +/-5%

Dummy

*

C342

220pF

50V, NPO, +/-5%

Dummy

*

R428 1K

*

R428 1K Q46

MMBT3904-7-F

Q46

MMBT3904-7-F

B

E C

TP14TP14

*

C361

1uF

10V, Y5V, +80%/-20%

Dummy

*

C361

1uF

10V, Y5V, +80%/-20%

Dummy

*

R431

1K

*

R431

1K

*

R413

0

Dummy

*

R413

0

Dummy

TP31TP31

*

C351

220pF

50V, NPO, +/-5%

Dummy

*

C351

220pF

50V, NPO, +/-5%

Dummy

R423

576

+/-1%

R423

576

+/-1%

R422

1.3KOhm

+/-1%

R422

1.3KOhm

+/-1%

*

R386 10

*

R386 10

*

R378 10

*

R378 10

*

R439

1K

*

R439

1K

*

R388

100 Ohm

+/-1%

Dummy

*

R388

100 Ohm

+/-1%

Dummy

TP26TP26

*

C372

1uF

10V, Y5V, +80%/-20%

Dummy

*

C372

1uF

10V, Y5V, +80%/-20%

Dummy

*

C352

220pF

50V, NPO, +/-5%

Dummy

*

C352

220pF

50V, NPO, +/-5%

Dummy

*

R376

57.6 Ohm

+/-1%

Dummy

*

R376

57.6 Ohm

+/-1%

Dummy

*

R380

100 Ohm

+/-1%

*

R380

100 Ohm

+/-1%

TP25TP25

*

C362

1uF

10V, Y5V, +80%/-20%

*

C362

1uF

10V, Y5V, +80%/-20%

*

R377

0

*

R377

0

*

R341 10

Dummy

*

R341 10

Dummy

*

C341

220pF

50V, NPO, +/-5%

Dummy

*

C341

220pF

50V, NPO, +/-5%

Dummy

R379

49.9

+/-1%

R379

49.9

+/-1%

*

R389

57.6 Ohm

+/-1%

*

R389

57.6 Ohm

+/-1%

*

R430

1K

*

R430

1K

*

R427

1K

*

R427

1K

2 OF 7

U2B

Socket-IntelPrescottCPU

2 OF 7

U2B

Socket-IntelPrescottCPU

D00#

B4

D01#

C5

D02#

A4

D03#

C6

D04#

A5

D05#

B6

D06#

B7

D07#

A7

D08#

A10

D09#

A11

D10#

B10

D11#

C11

D12#

D8

D13#

B12

D14#

C12

D15#

D11

DBI0#

A8

DSTBN0#

C8

DSTBP0#

B9

D16#

G9

D17#

F8

D18#

F9

D19#

E9

D20#

D7

D21#

E10

D22#

D10

D23#

F11

D24#

F12

D25#

D13

D26#

E13

D27#

G13

D28#

F14

D29#

G14

D30#

F15

D31#

G15

DBI1#

G11

DSTBN1#

G12

DSTBP1#

E12

D32#

G16

D33#

E15

D34#

E16

D35#

G18

D36#

G17

D37#

F17

D38#

F18

D39#

E18

D40#

E19

D41#

F20

D42#

E21

D43#

F21

D44#

G21

D45#

E22

D46#

D22

D47#

G22

DBI2#

D19

DSTBN2#

G20

DSTBP2#

G19

D48#

D20

D49#

D17

D50#

A14

D51#

C15

D52#

C14

D53#

B15

D54#

C18

D55#

B16

D56#

A17

D57#

B18

D58#

C21

D59#

B21

D60#

B19

D61#

A19

D62#

A22

D63#

B22

DBI3#

C20

DSTBN3#

A16

DSTBP3#

C17

*

R390

57.6 Ohm

+/-1%

Dummy

*

R390

57.6 Ohm

+/-1%

Dummy

*

R411

0

*

R411

0

Q45

2N7002

Q45

2N7002

G

DS