CMOS模拟集成电路版图设计入门教程

需积分: 44 118 浏览量

更新于2024-07-17

3

收藏 6.47MB PDF 举报

"CMOS模拟集成电路版图设计软件教程.pdf(pdf格式ppt)"

这份资源是一个关于CMOS模拟集成电路版图设计的软件教程,由薛晓博于2013年10月20日制作。教程主要涵盖了以下几个关键知识点:

1. **初识工艺流程与版图设计**

- 集成电路的制作过程涉及将设计的电路通过特定的工艺流程,如光刻、氧化、参杂注入和离子刻蚀等,在硅片上制造出三维的器件和导线。

- 这个过程可以比喻为堆叠积木,每一层都对应着器件或连线的一个层面,通过逐层制造来形成完整的集成电路。

2. **版图(Layout)概念**

- 版图是将三维的器件和导线投影到光刻掩模版上的二维绘图,它定义了器件的位置和连接方式。

- 光刻掩模版上的图形决定在光刻过程中哪些区域被保留,哪些被去除,进而影响硅片上的结构。

3. **N-well CMOS基本工艺流程**

- N-well CMOS工艺是集成电路制造中常见的一种工艺,教程通过剖面图和俯视图详细解释了其制造步骤,包括创建N型阱、氧化、扩散、光刻和刻蚀等,以实现P型和N型半导体区域的形成。

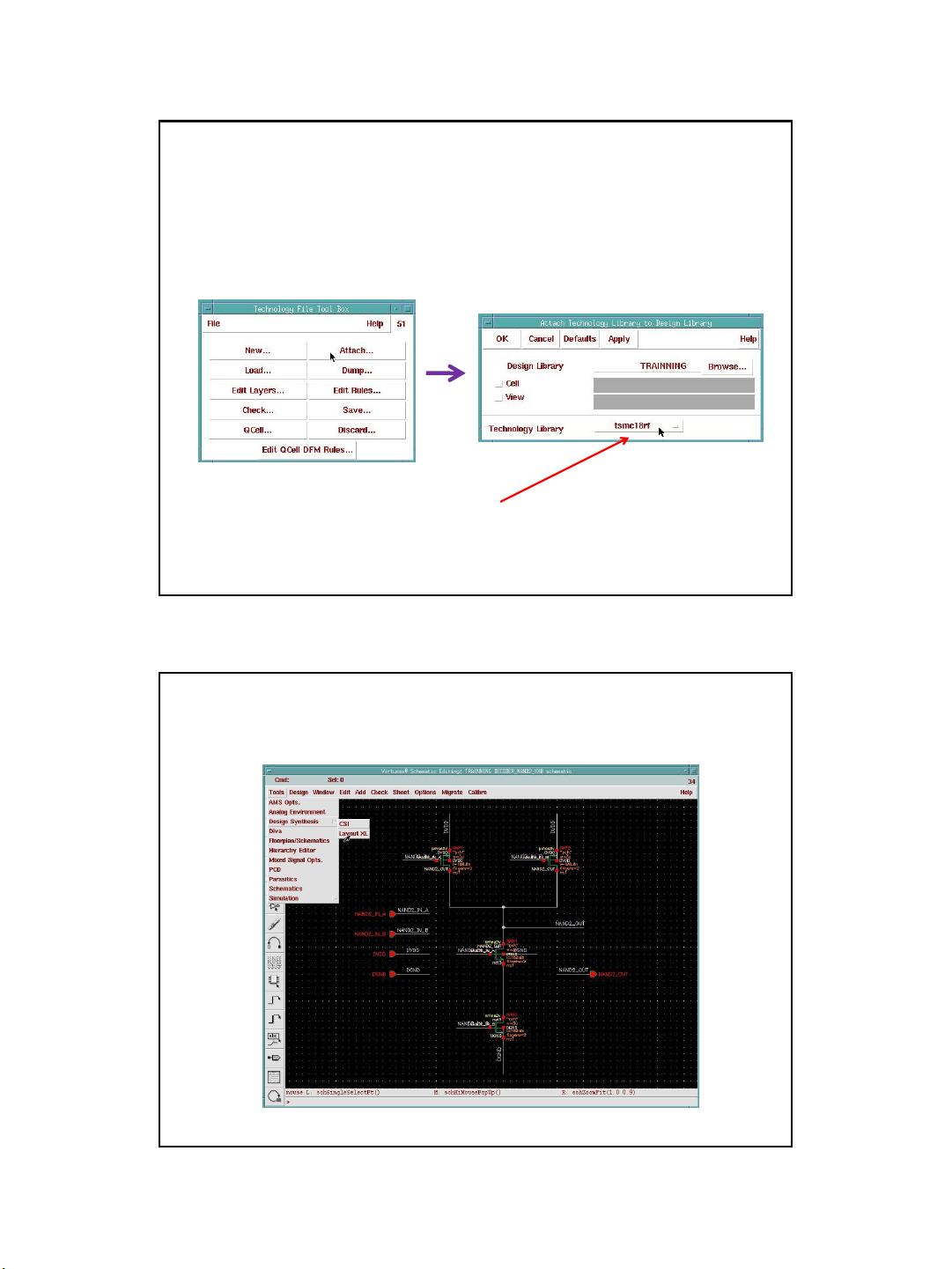

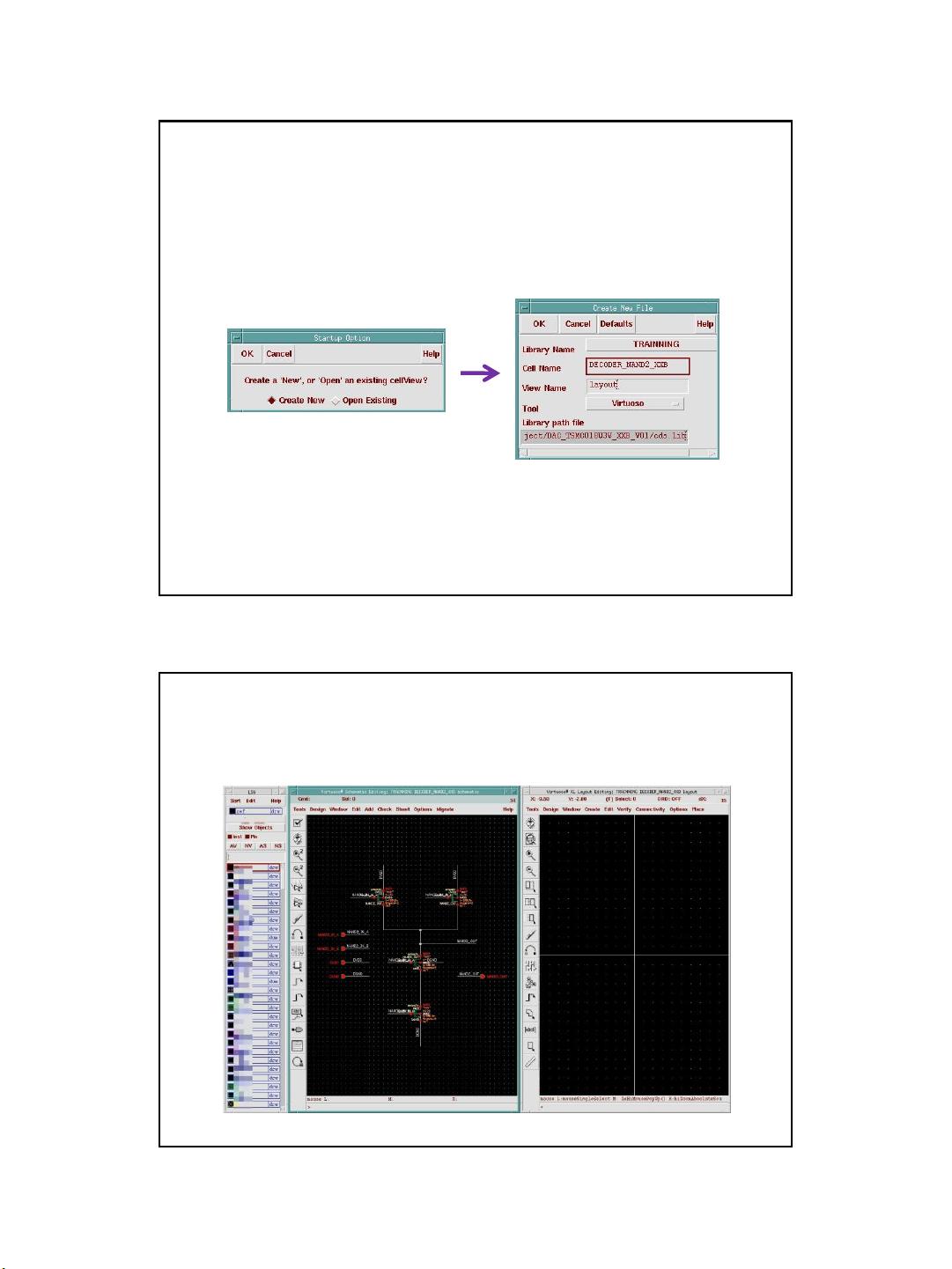

4. **Layout-XL基本使用方法**

- 虽然具体内容未详述,但可以推断教程中可能包含Layout-XL这款软件的基本操作指南,包括界面介绍、工具使用、图形编辑和布局规划等。

5. **快捷键与小技巧**

- 教程可能提供了一些提高版图设计效率的快捷键和实用技巧,帮助用户更快地掌握版图设计。

6. **DRC与LVS**

- DRC(Design Rule Check)是设计规则检查,确保版图设计符合制造工艺的限制和规则。

- LVS(Layout vs. Schematic)是对版图与电路原理图的一致性检查,确保设计的物理实现与电路功能相符。

7. **版图寄生参数提取与后仿真**

- 版图中的寄生参数,如电阻、电容和电感,对电路性能有重要影响,教程会讲解如何从版图中提取这些参数。

- 后仿真是在版图完成后,考虑了这些寄生参数对电路行为的影响进行的仿真,以验证电路的实际工作性能。

这个教程对于理解CMOS模拟集成电路的版图设计过程、学习版图设计软件的使用,以及熟悉集成电路制造工艺都是非常有价值的。通过学习,工程师可以更好地进行电路设计与优化,确保最终产品能够满足性能和制造的要求。

2012-03-20 上传

2019-04-01 上传

103 浏览量

2021-12-06 上传

2021-05-09 上传

2016-08-27 上传

2021-06-07 上传

2009-08-24 上传

qq_20491393

- 粉丝: 4

- 资源: 5

最新资源

- 正整数数组验证库:确保值符合正整数规则

- 系统移植工具集:镜像、工具链及其他必备软件包

- 掌握JavaScript加密技术:客户端加密核心要点

- AWS环境下Java应用的构建与优化指南

- Grav插件动态调整上传图像大小提高性能

- InversifyJS示例应用:演示OOP与依赖注入

- Laravel与Workerman构建PHP WebSocket即时通讯解决方案

- 前端开发利器:SPRjs快速粘合JavaScript文件脚本

- Windows平台RNNoise演示及编译方法说明

- GitHub Action实现站点自动化部署到网格环境

- Delphi实现磁盘容量检测与柱状图展示

- 亲测可用的简易微信抽奖小程序源码分享

- 如何利用JD抢单助手提升秒杀成功率

- 快速部署WordPress:使用Docker和generator-docker-wordpress

- 探索多功能计算器:日志记录与数据转换能力

- WearableSensing: 使用Java连接Zephyr Bioharness数据到服务器