2554 IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 25, NO. 10, OCTOBER 2010

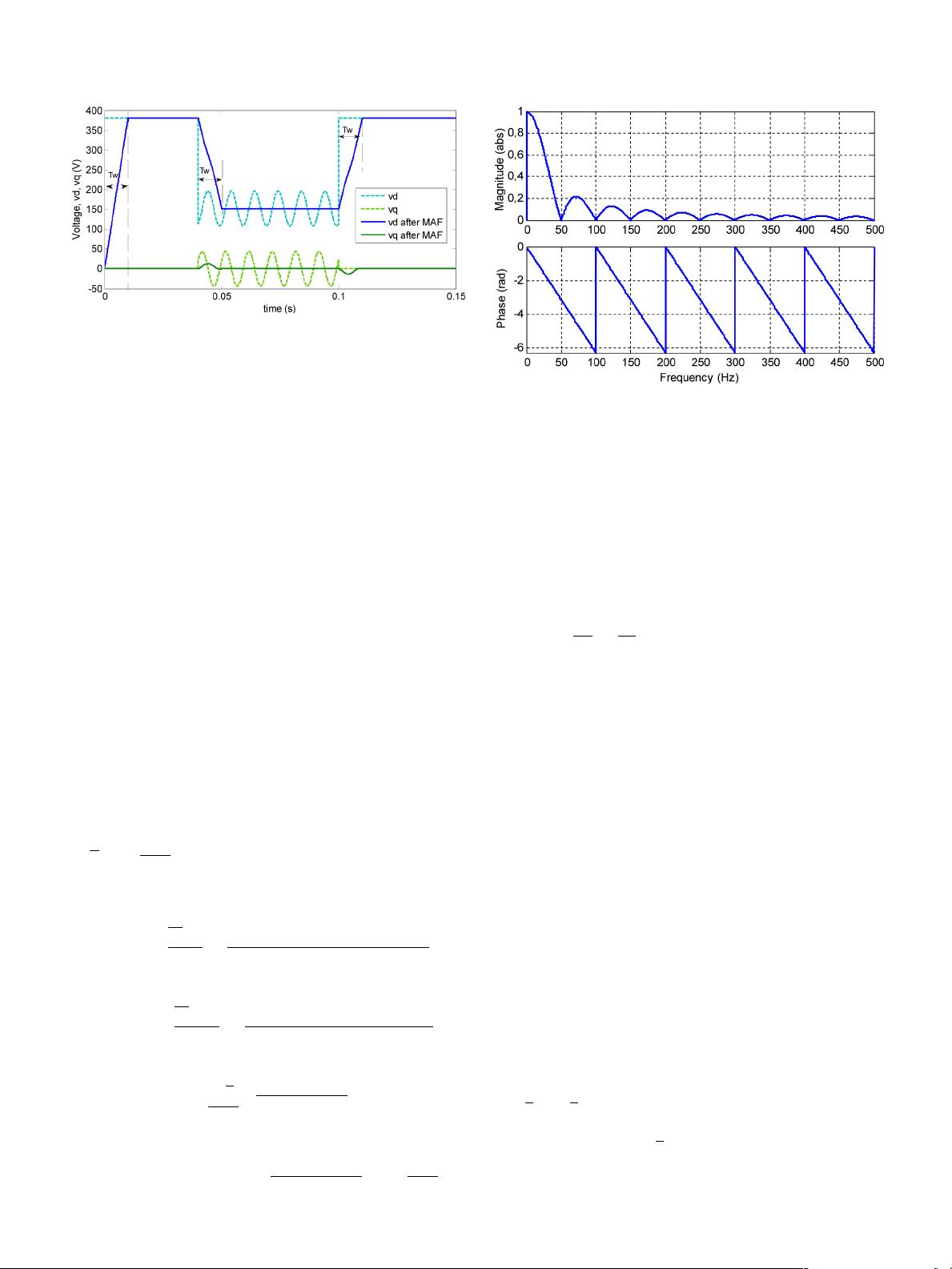

Fig. 1. Performance example of the MAF.

the larger T

w

is, the slower the detection dynamic. If the input

signal contains sinusoidal components, whose frequency is an

integer multiple of the equivalent frequency of the MAF (f

w

=

1/T

w

), the output signal will be free of oscillations containing

only the mean value of the input signal. The MAF will need

a period of time T

w

to gather the data and obtain the correct

output, hence, this is the delay produced by the MAF.

In Fig. 1, grid voltages suffer an asymmetric voltage dip

(20%, 40%, and 60%) that generates a negative sequence in the

dq components. The window width is 0.01 s, that is half the

input signal period and exactly the negative-sequence period.

The MAF can eliminate the input oscillation after gathering the

data. When the input signal changes suddenly, the output of

the MAF has an error during T

w

until the window contains an

integer number of oscillations and the MAF obtains again the

mean value.

Selection of the window width is an important issue. Depend-

ing on this, the MAF is able to perform as an ideal low-pass filter

for some input frequency components.

For a better understanding of the MAF, the transfer function

has been obtained and analyzed. Given an input signal

x(t)=A sin(ωt + θ

0

) (4)

with ω =2π/T . The output of the MAF will be

x(t)=

A

ωT

w

{cos[ω(t − T

w

)+θ

0

] − cos(ωt + θ

0

)}. (5)

Applying the Laplace transform to (4) and (5), the transfer

function for θ

0

=0becomes

G

MAF

(s)=

X(s)

X(s)

=

ω sin(ωT

w

) − s[1 −cos(ωT

w

)]

ω

2

T

w

. (6)

Substituting s = jω

G

MAF

(jω)=

X(jω)

X(jω)

=

sin(ωT

w

) − j[1 − cos(ωT

w

)]

ωT

w

. (7)

The magnitude and phase expressions are as following:

|G

MAF

(jω)| =

√

2

ωT

w

1 − cos(ωT

w

) (8)

and

ϕ[G

MAF

(jω)] = −arctan

1 − cos(ωT

w

)

sin(ωT

w

)

= −

ωT

w

2

. (9)

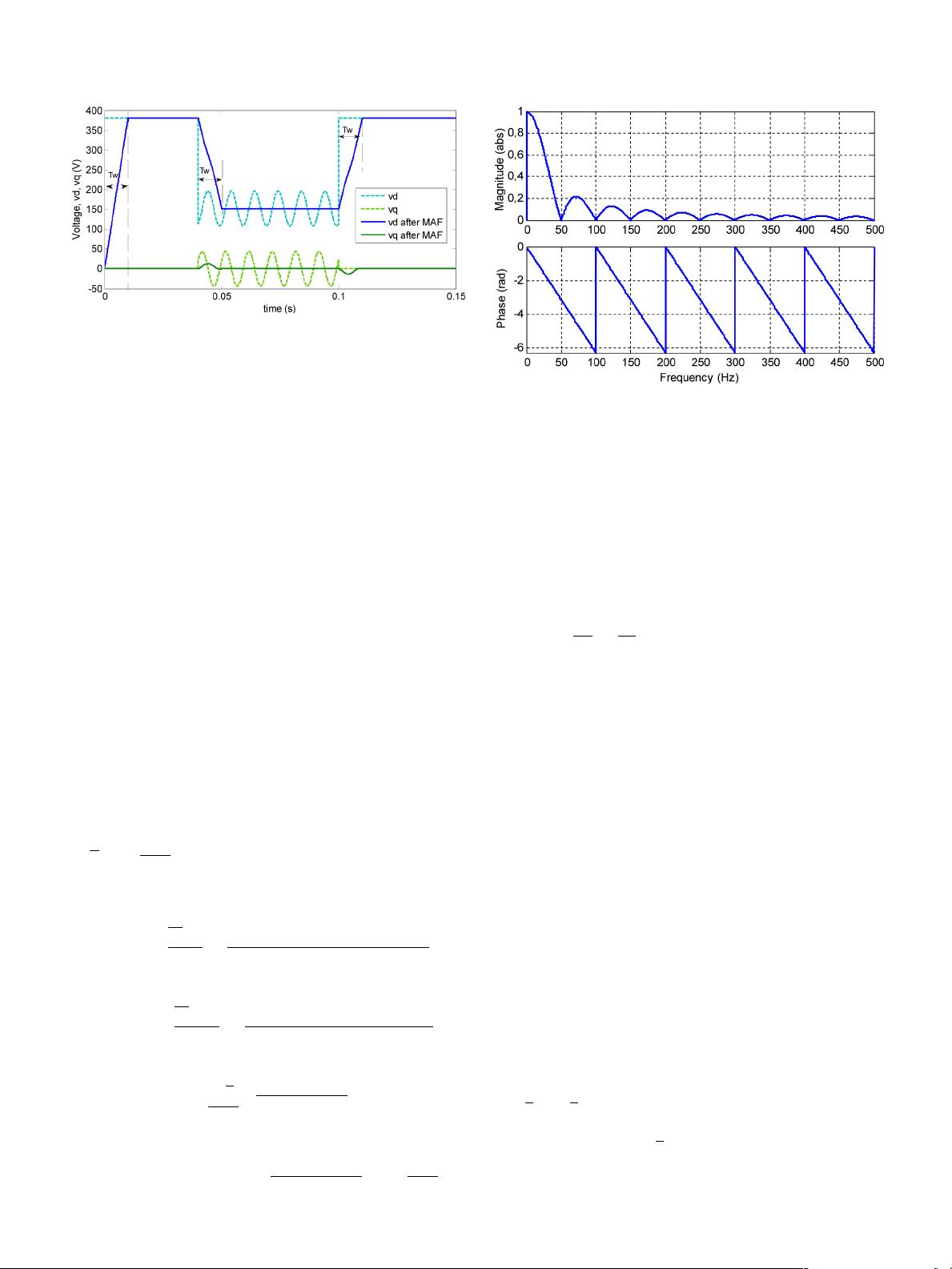

Fig. 2. Frequency response of the MAF.

The MAF is a finite-impulse response (FIR) filter that, as shown

in (9), has linear-phase response, being the time of the delay

constant and known.

From (8), the output magnitude of the MAF is zero whenever

[1 − cos(ωT

w

)] = 0, i.e.,

ωT

w

= k2π for k =1, 2, 3,... (10)

or

T

w

T

=

f

f

w

= k for k =1, 2, 3,.... (11)

Fig. 2 shows the frequency response of the MAF. In this rep-

resentation, the window width of the MAF is T

ω

= T , being T

the input signal period. Observe that the frequency components

that comply with (11) are canceled completely; therefore, all

of the input signal are harmonics. The frequency components

close to the filter-node frequencies will not be canceled, but

very attenuated. Additionally, according to (9), the MAF shows

linear phase.

When using the MAF to filter dq components, if T

w

= T/2,

the dq even-order oscillations from odd-order harmonics and

the negative sequence would be completely removed. If even-

order harmonics with significant amplitudes are expected, the

window width of the MAF should be increased to T

w

= T .

IV. FSPLL

Fig. 3 shows the structure of the proposed positive-sequence

detector. First, the grid voltage vector is transformed using a

synchronous reference frame rotating at fundamental frequency

(ω

f

) and with an arbitrary angular position (θ

f

). The compo-

nents v

d

and v

q

may contain oscillations due to harmonics and

a negative voltage sequence. Both components are thus filtered

through the MAF; therefore, if an appropriate window width is

used,

v

d

and v

q

will be constant and containing only the positive

sequence of the grid voltages.

As shown in Fig. 4, the

v

q

component is not necessarily zero

because the angle used in the Park transformation is arbitrary.

Thus, the voltage vector is not on the d-axis, but on another