SERCON100M/S/SL Datasheet - Revision 1.3

需积分: 9 51 浏览量

更新于2024-07-16

收藏 268KB PDF 举报

"该文件是关于SERCON100M/S/SL的datasheet,版本1.3,主要涵盖了SERCON100系列产品的修订历史、功能增强以及FPGA设备的相关信息。"

SERCON100M/S/SL是基于FPGA(Field-Programmable Gate Array)的设备,用于实现串行通信接口。这份 datasheet 提供了产品的重要细节,包括修订历史、新增功能以及与FPGA相关的硬件配置。

修订历史部分显示,该文档经历了多个版本的更新:

- V1.0(2005年4月6日):首次发行。

- V1.1(2005年4月18日):改进了LED引脚描述,添加了对低活动信号LED1到LED2的详细说明,以及对Int_Mot引脚的更详细描述。

- V1.2(2005年5月30日):将LED1_1和LED1_2信号更名为/LINKPort1和/LINKPort2。

- V1.3(2005年6月9日):增加了新的SERCON100SL引脚布局,移除了配置引脚Int_Mot和RDY及RDYMode引脚。

在功能增强方面, datasheet 强调了新引入的低活性信号/PHY_Reset,这是一个位于E1引脚的新功能,用于在使用SERCON100M的PHYCLK输出作为时钟源时,定义重置以太网PHY的行为。

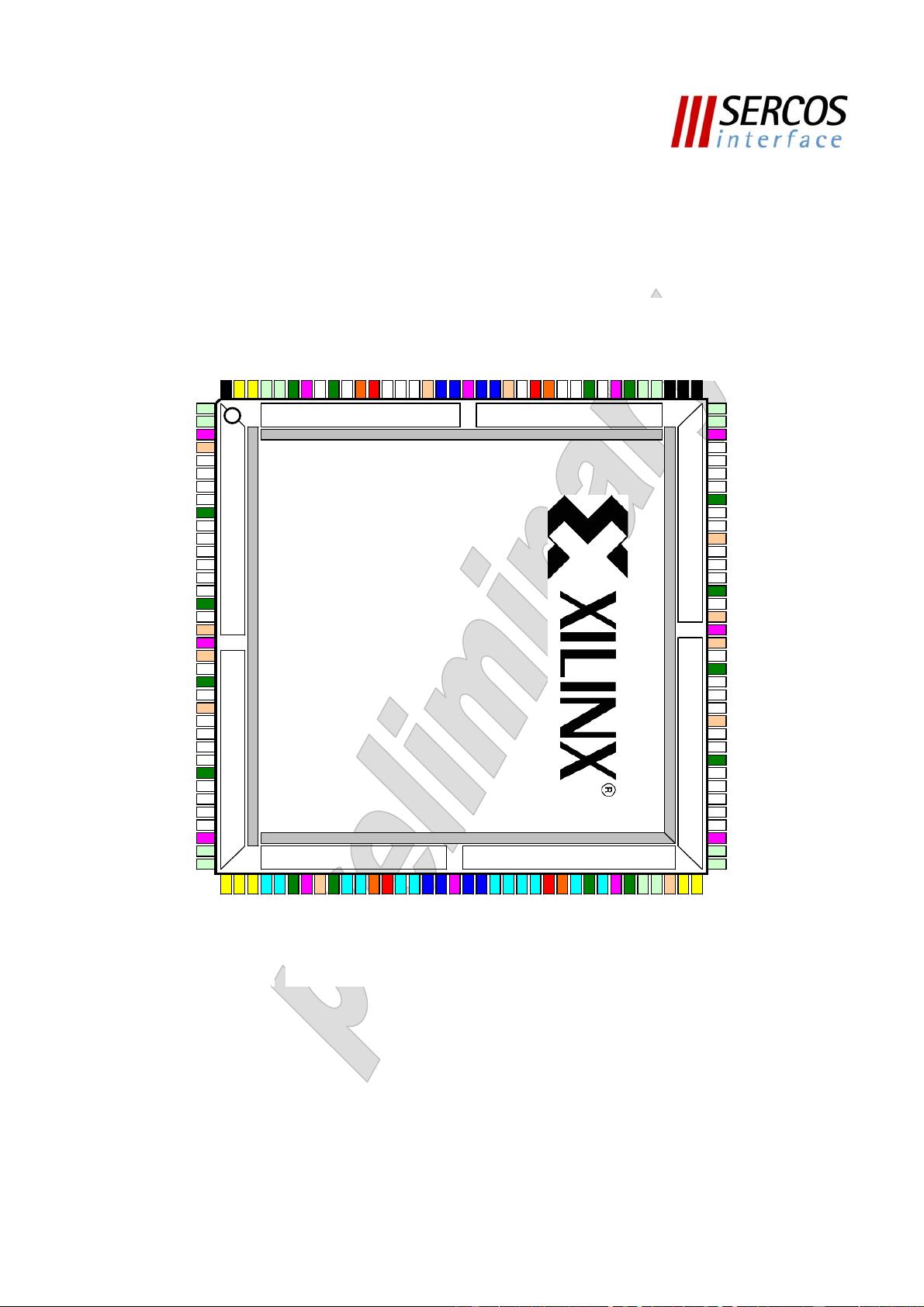

关于FPGA设备, datasheet 列出了两种型号:

- XILINX XC3S400:采用FT256(256球栅格)封装,具有16/32位数据总线,16位地址总线,32KB的RAM,并且支持主模式。

- XILINX XC3S200:使用TQ144封装,16位数据总线,12位地址总线,24KB的RAM,同样支持主模式,但不支持从模式。

速度等级为-4,表示这些FPGA设备可以工作在较高的速度等级。用户可以通过打开补充数据表获取更详细的信息,这些数据表可能包含了关于功耗、时序约束等更多硬件设计的关键参数。

这份datasheet是针对SERCON100M/S/SL的详细技术参考,对于理解其硬件接口、功能特性以及如何利用FPGA实现高性能串行通信非常有帮助。设计工程师、硬件开发者或系统集成者在使用这些设备时,应仔细阅读此文档以确保正确和有效地利用其功能。

2019-10-11 上传

2019-06-10 上传

124 浏览量

2019-06-10 上传

2019-09-25 上传

2024-06-27 上传

2023-05-09 上传

283 浏览量

weixin_38743602

- 粉丝: 396

- 资源: 2万+

最新资源

- Msp430x1xx family User's Guide.pdf

- Thinking.In.Java.3rd.Edition.Chinese.eBook-YSSY.pdf

- jsp随堂考试系统毕业论文

- 《arm嵌入式系统基础教程》

- Java经典代码.pdf

- JAVA编码规范.doc

- iPhone SDK Application Development, 1st Edition

- ShellExecute使用详解

- JavaEE+5.0规范(简体中文版)

- J2EE全实例教程(代码详细)

- 高质量C++编程指南

- java基础教程(适合初学者)

- C#编程规范(超详细)

- myeclise7.1注册类

- 南开一百题最终word版

- DOS系统操作命令集