"DC 学生指南"

在DC(Design Compiler)中,综合是一个关键步骤,它结合了翻译、优化和映射,以将高级设计语言(如Verilog或VHDL)转换为门级电路,同时考虑时序和其他性能指标。这个过程包括几个关键阶段,确保设计满足速度、面积和功耗的要求。

1. **综合流程**

- **工艺库和器件**:在开始综合之前,必须设置工艺库和器件。工艺库包含了电路元件(cell),这些元件的特性由供应商提供的定时数据定义。`target_library`变量指示DC使用哪个库来构建电路。`link_library`变量则用于解析引用的设计,它会首先检查内存,然后搜索指定的库文件。

2. **DC配置**:

- **.synopsys_dc.setup文件**:这是DC工具的初始化文件,用于设定各种环境变量和库路径。例如,可以设置`target_library`和`link_library`变量来指定工艺库和解析设计的位置。

3. **设计对象**:

- **Verilog角度**:在DC中,设计可以表示为Verilog模块,其中包含端口、网络和引脚。CLK可能表示时钟信号、端口、网络或引脚,具体取决于上下文。DC工具会根据对象的类型和连接情况来放置负载。

- **get命令**:这是一个强大的工具,用于检索设计中的特定对象。例如,`get_nets CLK`将返回所有名为CLK的网络,而`set_load`则可以设置特定网络的负载。

4. **列表操作**:

- **list对象**:在DC中,列表是一种特殊的数据结构,用于存储多个对象的名字。例如,`all_inputs`、`all_outputs`和`get_designs`命令分别返回输入端口、输出端口和所有设计的列表。

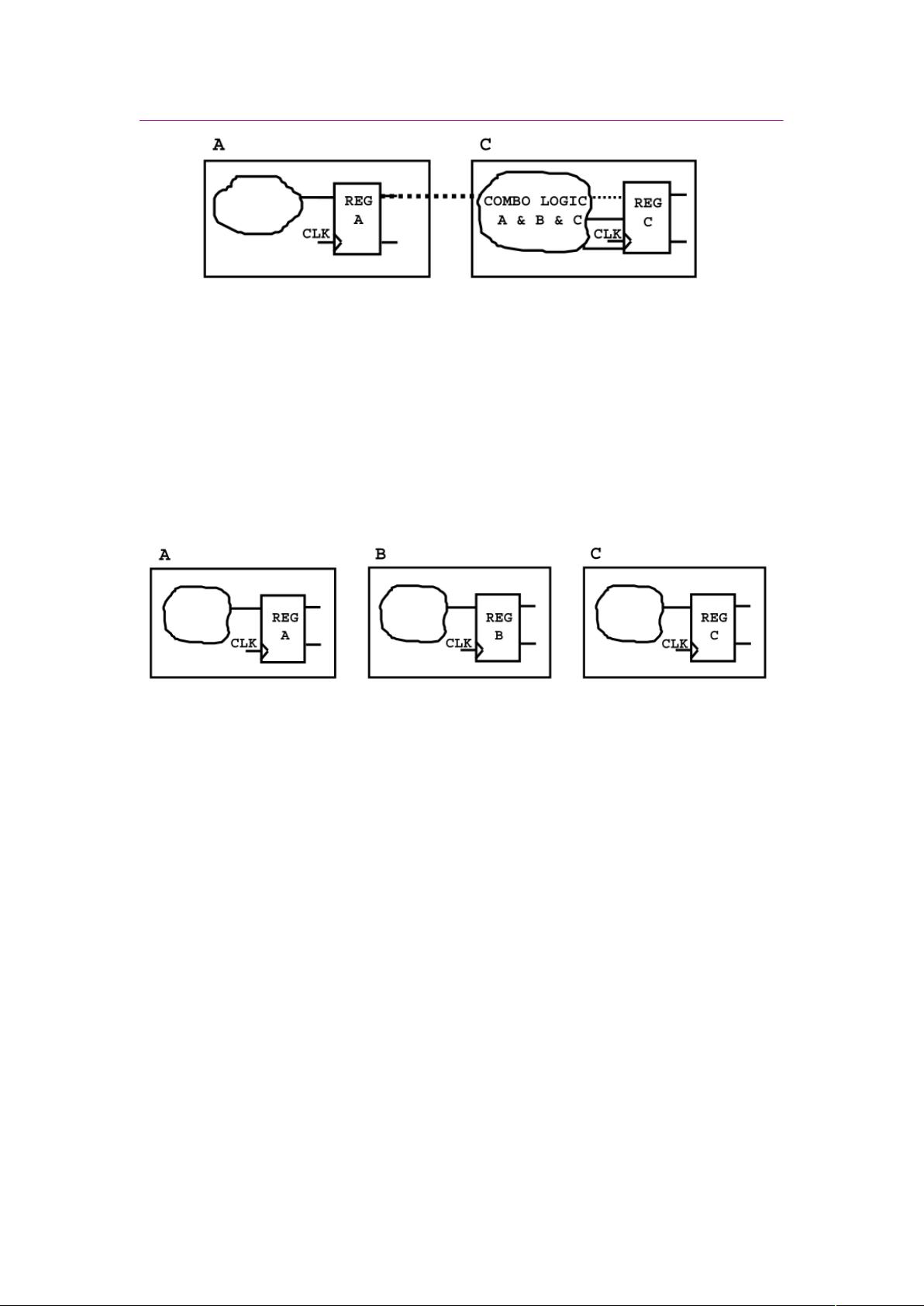

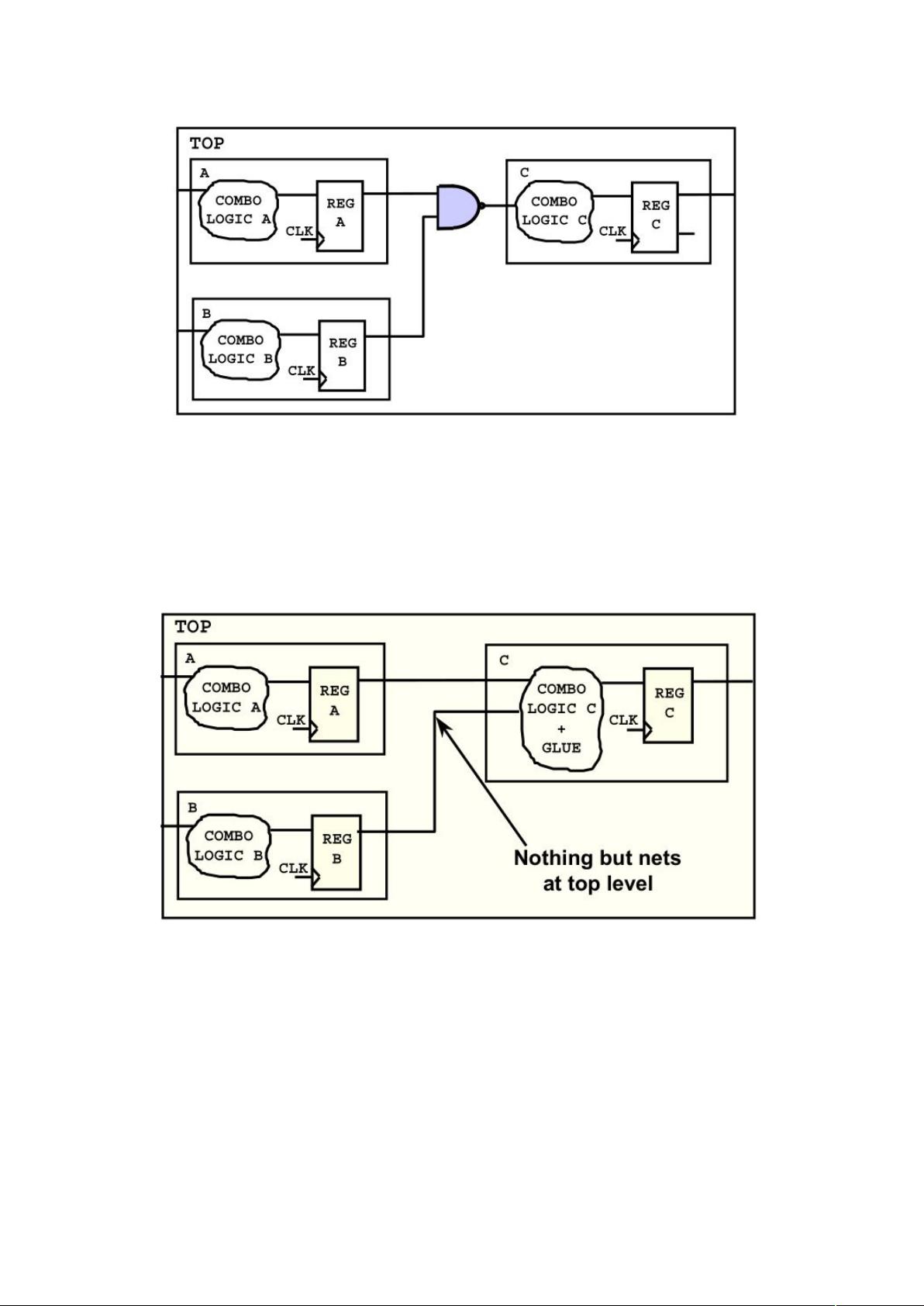

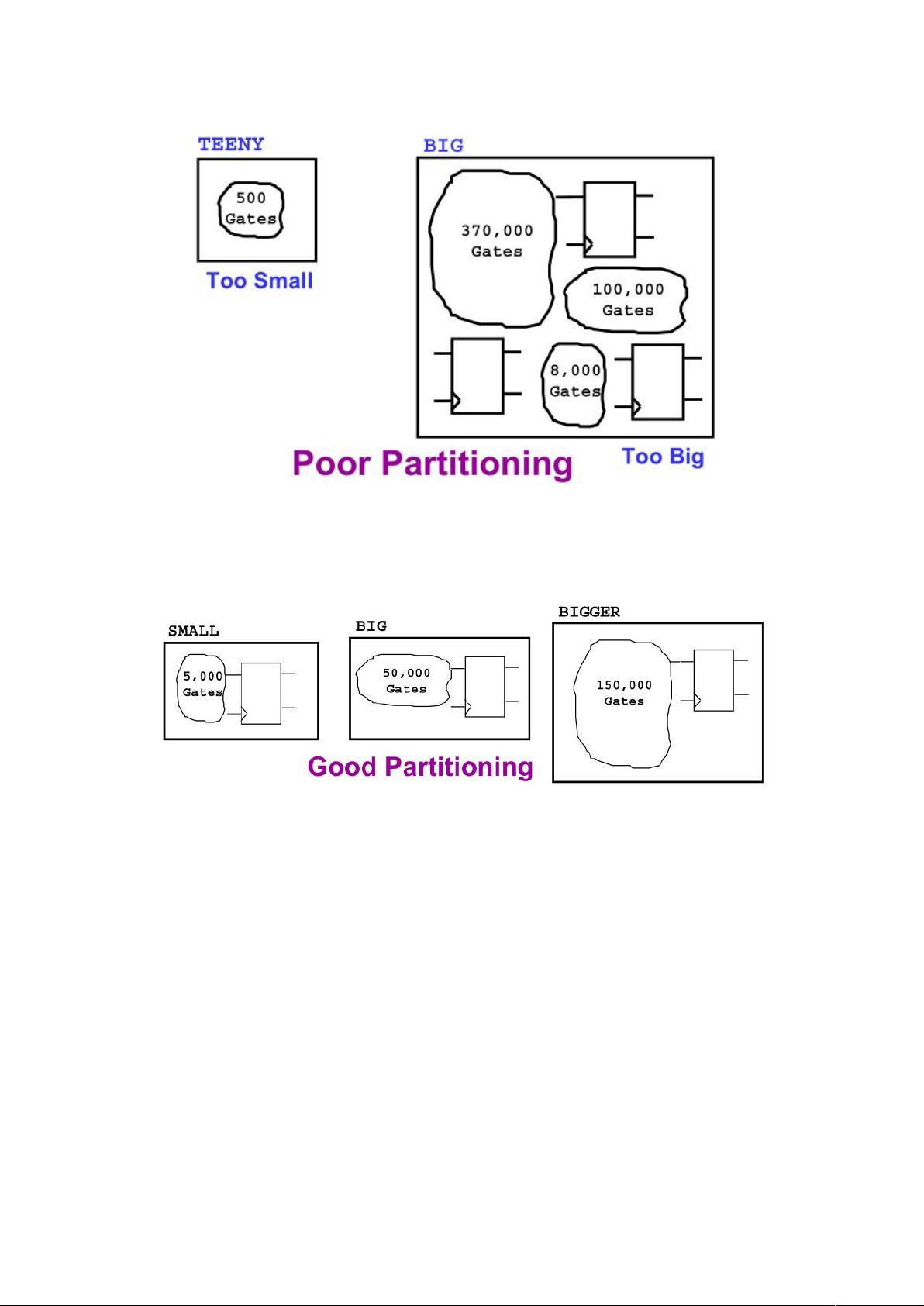

5. **模块化综合**(Partitioning for Synthesis):

- **分区**:在大型设计中,模块化综合是必不可少的,它允许将大设计分解为更小、更易于管理的部分。这有助于优化特定模块,减少设计时间和复杂性。

6. **时序分析(Timing Analysis)**:

- **Setup Libraries and Objects**:DC使用静态时序分析(Static Timing Analysis, STA)来计算设计中的线路时序。在映射阶段,DC会基于库中的定时数据计算电路的时序。

7. **变量设置**:

- **search_path**变量:除了`target_library`和`link_library`之外,`search_path`用于定义DC搜索库文件的额外路径,这样可以方便地引用不在标准位置的库。

8. **命令和控制**:

- **link命令**:用于解析和链接外部设计,例如`lappend`命令可以添加路径到库搜索列表,使DC能找到`DECODE.db`这样的设计。

在进行DC综合时,理解这些基本概念和工作流程至关重要,因为它们直接影响到设计的性能和可实现性。通过精细的库配置、有效的设计分区以及对时序的深入分析,可以实现高效的综合过程,从而创建满足规格的高质量数字集成电路。