Verilog HDL基础教程:从入门到精通

需积分: 10 190 浏览量

更新于2024-07-20

收藏 278KB PDF 举报

"这是一份详细的Verilog HDL入门教程,涵盖了从基本语法到建模方式的各种概念,包括标识符、关键词、数据类型、运算符、建模方式(行为、数据流、结构化)以及模块定义等核心内容。"

Verilog HDL是一种广泛使用的硬件描述语言,用于数字系统的建模和设计。这篇教程旨在帮助初学者理解和掌握Verilog的基本用法。

首先,教程介绍了Verilog的基本语法,包括标识符的定义(4.1标识符),它是编程中的基础元素,如变量名或模块名。接着是关键词(4.1.2关键词),它们在Verilog语句中具有特殊含义,比如`module`、`endmodule`等。此外,教程还提到了书写规范(4.1.3书写规范建议),这对于编写清晰易读的代码至关重要。

在数据类型部分(4.5数据类型),教程详细讲解了线网类型(4.5.1线网类型)和寄存器类型(4.5.2寄存器类型),这是Verilog中两种主要的数据载体。接着,教程介绍了不同类型的值集合,包括数字值集合(4.4数字值集合)、常量(4.4.2常量)以及值集合(4.4.1值集合),这些都是构建逻辑表达式的基础。

运算符和表达式是编程中的关键元素,教程涵盖了算术运算符(4.6.1算术运算符)、关系运算符(4.6.2关系运算符)、逻辑运算符(4.6.3逻辑运算符)、按位逻辑运算符(4.6.4按位逻辑运算符)、条件运算符(4.6.5条件运算符)和连接运算符(4.6.6连接运算符)。这些内容让读者能够编写复杂的逻辑条件和计算。

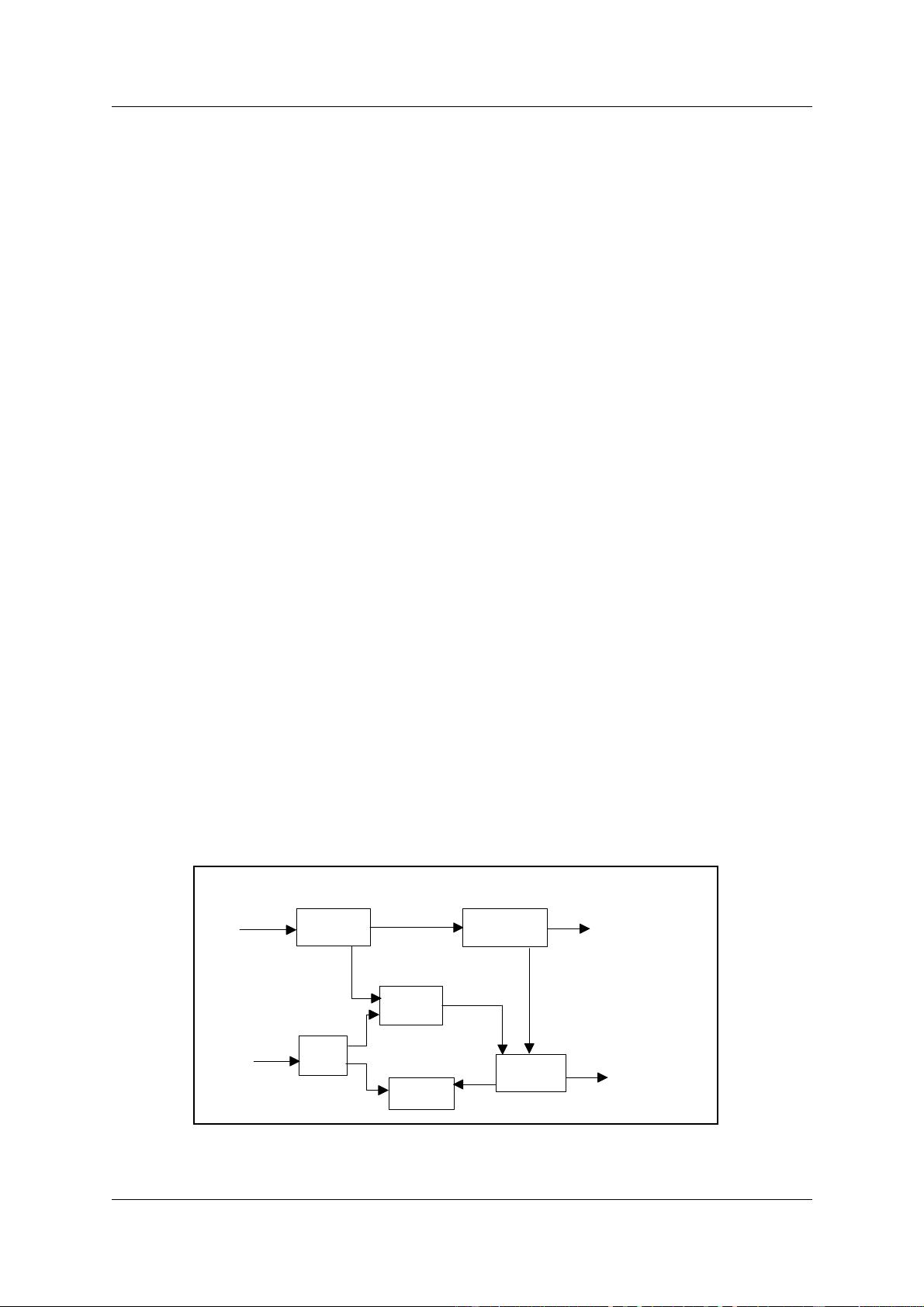

在建模方式上,教程涵盖了Verilog的三种主要建模方法:结构化描述(3.3.1结构化描述方式),数据流描述(3.3.2数据流描述方式)和行为描述(3.3.3行为描述方式)。结构化建模主要用于描述硬件结构,数据流建模则关注信号的流动,而行为建模则允许以软件编程的方式描述硬件行为。

模块是Verilog的核心构造单元,教程详细讲解了模块的定义结构(3.1.1简单事例,3.1.2模块的结构,3.1.3模块语法),模块端口(5.2模块端口),以及如何通过实例化语句(5.3实例化语句)来复用模块。此外,还有数据流建模的具体实例(6.3数据流建模具体实例)和行为建模(7行为建模,包括7.1简介、7.2顺序语句块、7.3过程赋值语句、7.4行为建模具体实例),这些都提供了实际应用的例子。

最后,教程还涉及了其他方面(8其他方面)和一些习题(9习题),帮助读者巩固所学知识,并通过实际操作加深理解。

这个Verilog HDL入门教程全面地介绍了Verilog的基础概念和语法,为学习者提供了一个坚实的起点,以便他们能够进一步深入学习和实践数字系统的设计。

点击了解资源详情

点击了解资源详情

103 浏览量

103 浏览量

271 浏览量

178 浏览量

点击了解资源详情

260 浏览量

snowfoxhxm

- 粉丝: 5

最新资源

- iOS绘制圆图百分比简易Demo展示

- React模因生成器:创建并下载个性化模因

- 拍照录音摄像:掌握核心技术的源代码实现

- Spring RMI Java学习:深入ServerClient架构应用

- 解决Code 2020挑战:我的Python方案分享

- 自动生成iOS Model文件的jsonTransForm工具

- iOS多点触控技术源码解析与应用

- Maven 3.3.9安装指南与配置要求

- NFL球迷必备:FOOTBALL JERSEY CENTRAL-crx插件

- SQLite浏览器:优化数据库编程与错误降低

- GeneticSculptor: 利用遗传算法和体素创造艺术作品

- ModernDeck Enterprise:企业环境下的专业Twitter客户端部署与配置

- 深入解析Tomcat架构及其优化策略

- C#开发的模拟洗衣机滚筒自定义控件

- CRT软件驱动的安装与应用

- 兼容性指南:确保mod_wsgi与Python 2.7和Apache VC9匹配