FPGA实现的m序列发生器及其VHDL设计

版权申诉

99 浏览量

更新于2024-07-04

收藏 548KB DOC 举报

"基于FPGA的m序列发生器利用移位寄存器理论,通过VHDL语言在Altera的QuartusⅡ软件平台上进行设计和仿真,以实现m序列的高效、灵活生成,适用于多种应用场景,如雷达、通信等。文章探讨了三种m序列的实现方法,包括门电路、DSP编程和VHDL+CPLD,重点介绍了基于FPGA的实现方式的优势,如硬件电路的灵活性和可编程性。"

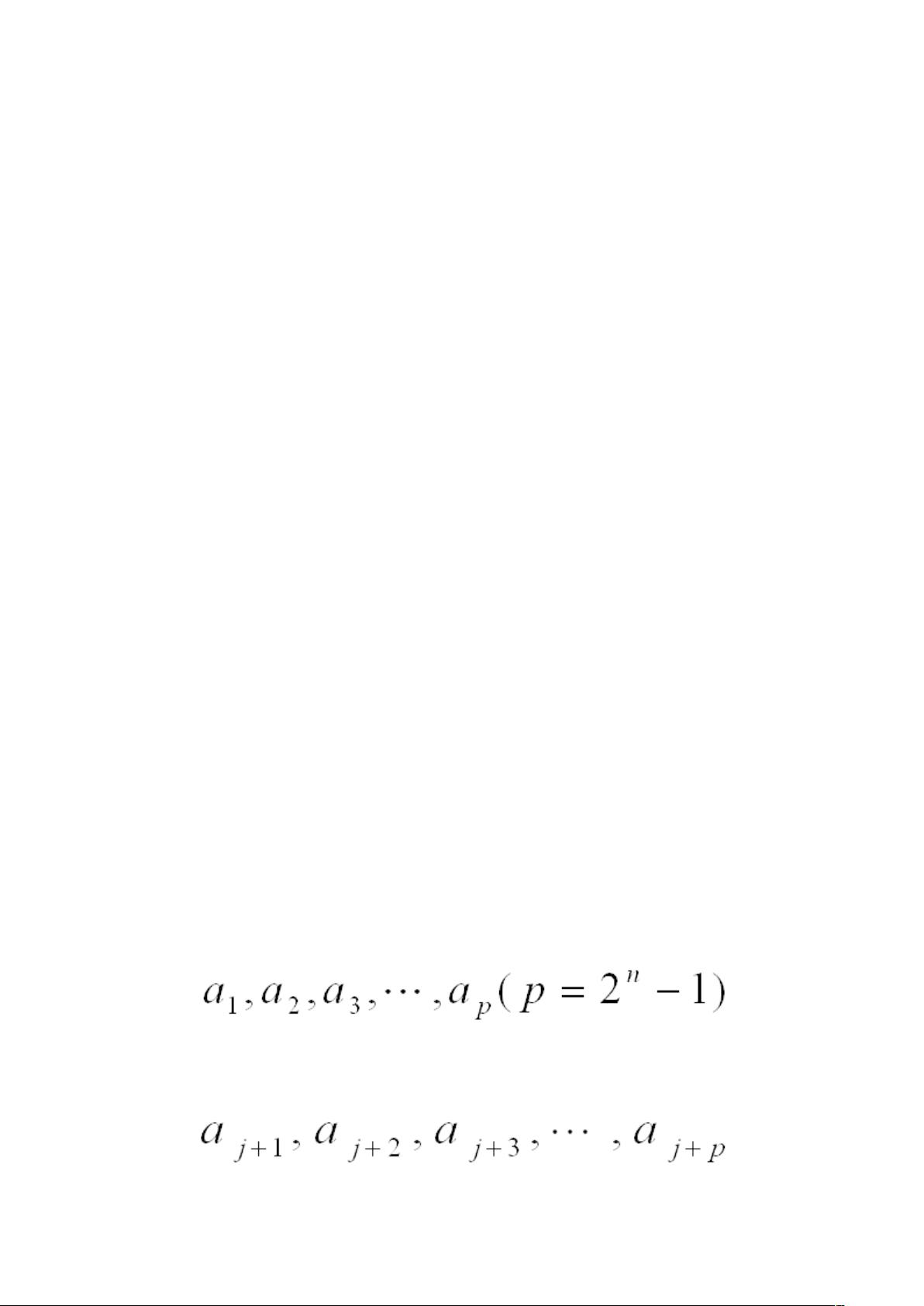

基于FPGA的m序列发生器设计主要依赖于移位寄存器理论,这是一种利用线性反馈机制产生伪随机序列的方法。m序列,即最长线性反馈移位寄存器序列,它的生成基于一个特定的本原多项式,通过移位寄存器的反馈逻辑实现。这种序列因其简单的结构和广泛的适用性而在通信、密码学等多个领域中得到广泛应用。

在FPGA实现中,设计师首先需要确定序列的本原多项式,这决定了移位寄存器的级数和反馈路径。然后,利用VHDL语言编写元件例化语句,将移位寄存器的逻辑结构映射到FPGA的硬件结构上。VHDL是一种硬件描述语言,它允许设计师以行为或结构方式描述电路,非常适合于复杂数字系统的实现。

使用FPGA作为实现平台有诸多优点。相比门电路实现,FPGA可以提供更高的集成度,减少物理空间的需求,并且更易于调整和重配置。与DSP编程相比,FPGA的实现方式更加通用,不局限于专业用户,同时也提供了更快的运行速度。此外,通过微处理器对FPGA进行初始化,可以灵活地改变m序列的周期和初始相位,以满足不同应用需求。

文章中提到的m序列发生器分为简单型和模块型两种结构,这两种结构在实现时可能会有所不同,但核心都是通过移位寄存器的线性反馈来产生周期性的序列。扰码过程则是为了将短周期序列转换为长周期序列,以提高通信的安全性和抗干扰性。

基于FPGA的m序列发生器设计结合了硬件的高效性和软件的灵活性,是实现伪随机序列生成的理想选择。通过这种方法,不仅可以快速生成所需的m序列,还能适应不断变化的系统需求,是现代电子和通信系统中的一个重要组成部分。

1147 浏览量

118 浏览量

441 浏览量

139 浏览量

2022-06-25 上传

2021-10-04 上传

239 浏览量

zzzzl333

- 粉丝: 831

最新资源

- 网页自动刷新工具 v1.1 - 自定义时间间隔与关机

- pt-1.4协程源码深度解析

- EP4CE6E22C8芯片三相正弦波发生器设计与实现

- 高效处理超大XML文件的查看工具介绍

- 64K极限挑战:国际程序设计大赛优秀3D作品展

- ENVI软件全面应用教程指南

- 学生档案管理系统设计与开发

- 网络伪书:社区驱动的在线音乐制图平台

- Lettuce 5.0.3中文API文档完整包下载指南

- 雅虎通Yahoo! Messenger v0.8.115即时聊天功能详解

- 将Android手机转变为IP监控摄像机

- PLSQL入门教程:变量声明与程序交互

- 掌握.NET三层架构:实例学习与源码解析

- WPF中Devexpress GridControl分组功能实例分析

- H3Viewer: VS2010专用高效帮助文档查看工具

- STM32CubeMX LED与按键初始化及外部中断处理教程