WANG et al.: 5.35-mW 10-MHz SINGLE-OPAMP THIRD-ORDER CT MODULATOR 2785

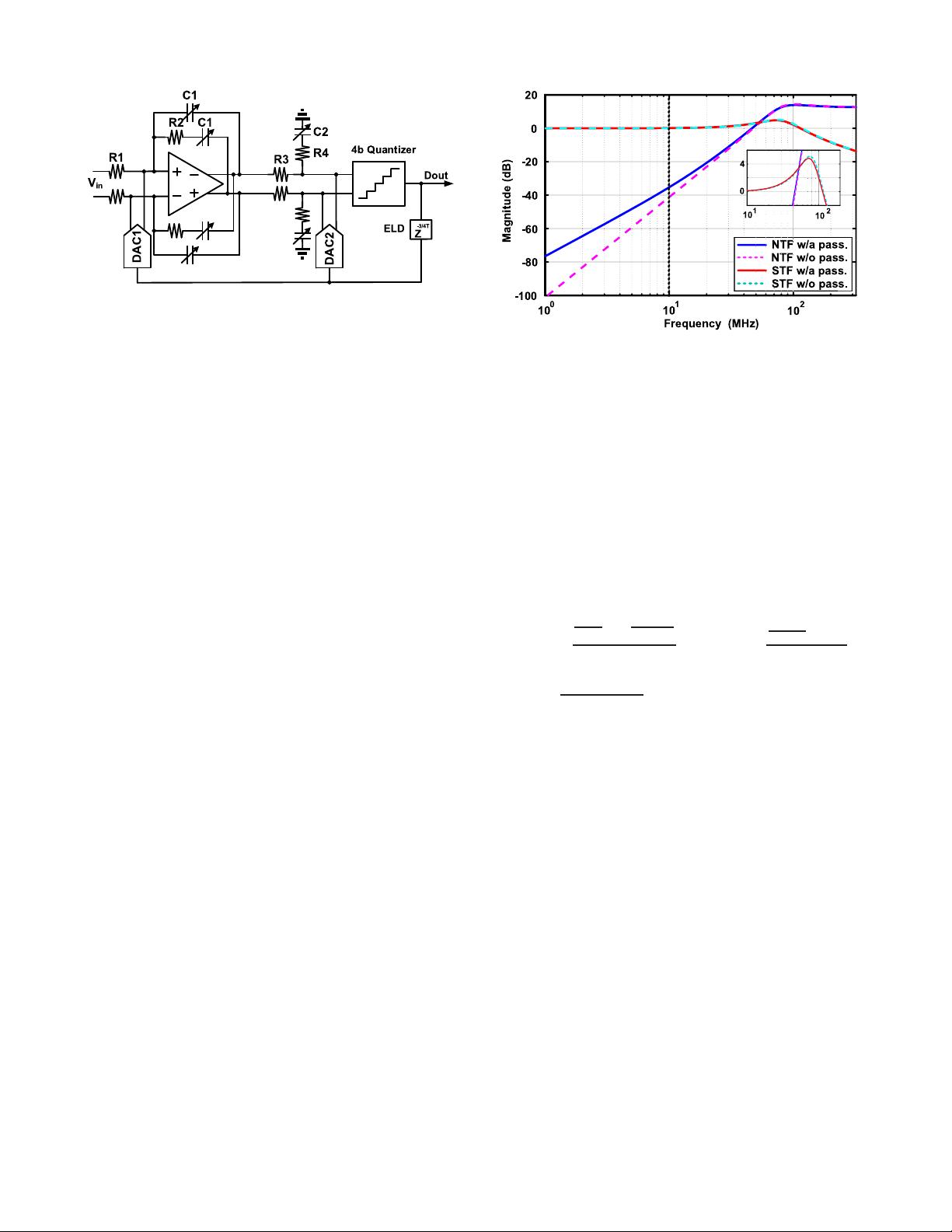

Fig. 4. Block diagram of the proposed 3rd-order ADC.

Besides SAB, the passive filter can also enhance the LF

order with a small power overhead [18], [19]. As Fig. 3(b)

shows, higher order can be obtained with passive components,

including resistors and a capacitor; however, such passive inte-

grator exhibits a drawback because its TF is non-ideal which

affects the inband quantization noise attenuation. We will

analyze its design impact in Section III-C.

B. Proposed Modulator

The SAB jointly with the passive integrator replace

the power-hungry 1st–3rd integrators from the architecture

in Fig. 2. We implement the first and second integrators,

as well as the first feedforward path, with an improved

version of the SAB integrator. Further, the passive integrator

substitutes the last integrator and the second feedforward path.

Such combination enables a 3rd-order LF implementation with

one opamp, thus significantly reducing the power consumed

by the integrators. The passive integrator also allows ELD

compensation without any active adder. Fig. 4 shows the

circuit schematic of the proposed modulator with the other

parts in the block format. We use non-return-to zero (NRZ)

current-steering DACs (DAC1/DAC2) to alleviate the impact

of the clock jitter and improve the power supply rejection ratio

(PSRR). The value of the input resistor (R1) is determined by

the noise requirement of the modulator, which simultaneously

decides the conducted current of the DAC1 and capacitor

loads (C1), implying that the value of R1 induces a tradeoff

between the noise budget and power of the DAC and opamp.

In the modulator, we choose R1 = 1k to balance such

tradeoff with the target SNR specifications for low power.

In [16], a feedback resistor is introduced to improve the SQNR

by optimizing the zero in the NTF, but its induced non-

shapeable thermal noise indeed yields a diminishing return on

the overall SNR. The proposed SAB integrator removes the

feedback resistor in the RC biquad which alleviates a non-

shapeable noise source thus improving the overall SNDR of

the modulator.

DAC1 and DAC2 are the main feedback and the ELD com-

pensation DAC, respectively. We adopt an SAR architecture

in the 4-bit QTZ due to its outstanding energy efficiency and

no offset issue with only one comparator, which is critical in

our design as the passive integrator attenuates the input swing

of the QTZ to about 0.5 V

pp

. The ELD is introduced by the

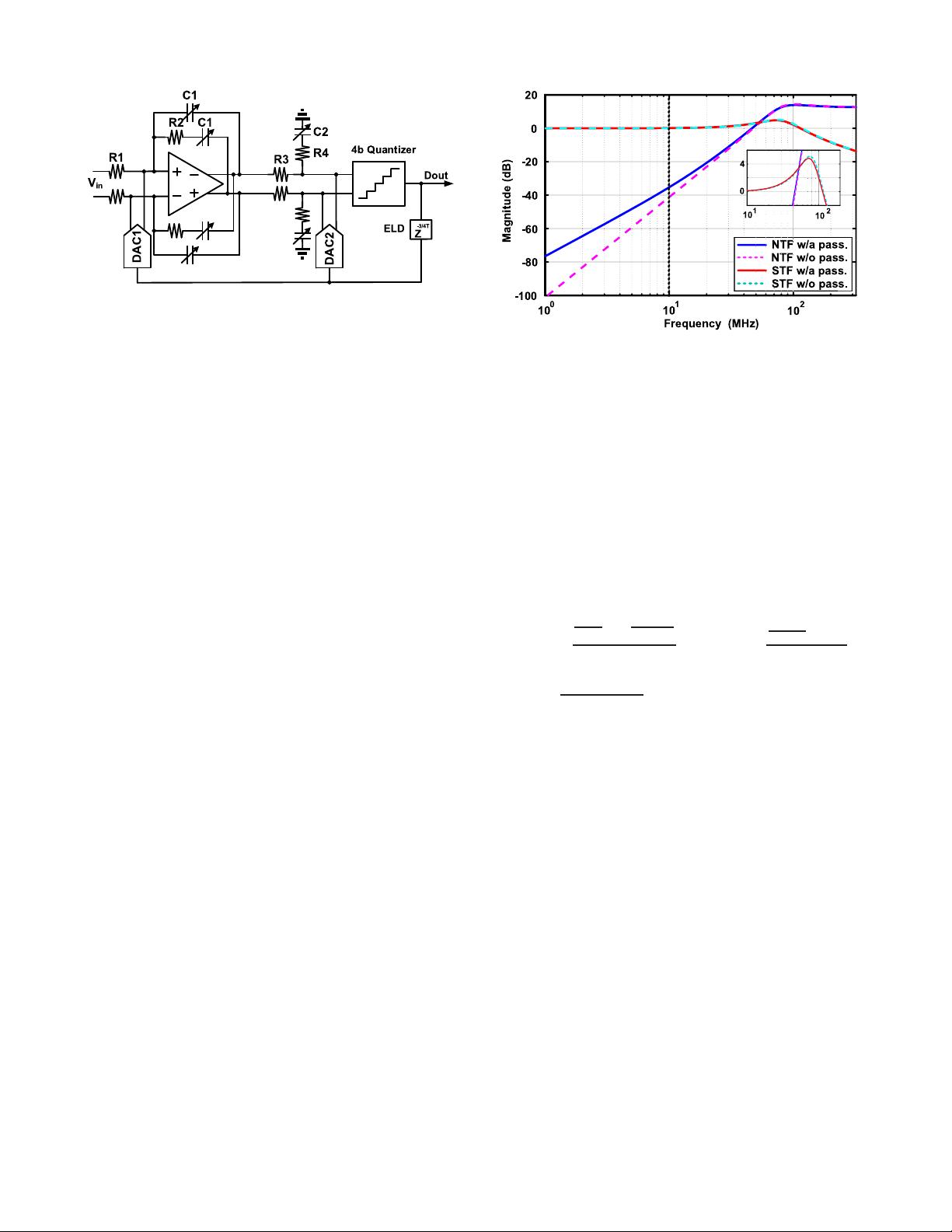

Fig. 5. STF and NTF magnitude response for 3rd-order LF, and 2nd-order

LF + passive integrator.

QTZ and feedback path, which is caused by the sampling of

the SAR QTZ and the latching operation of the main DAC.

The proposed modulator also shows a strong stability even

with a high out-of-band gain which benefits from the SAB

together with the passive integrator, as it is detailed next.

C. Passive Integrator and ELD Compensation

Even though the passive integrator can supply extra noise

shaping with little power overhead, it imposes that the TF of

the LF is non-ideal as shown by the follow TF of the proposed

modulator

H(s) =

⎛

⎝

1

R

1

C

1

s +

1

R

1

R

2

C

2

1

s

2

+ k

DAC2

⎞

⎠

×

R

4

R

3

+R

4

s + k

3

s + k

3

,

k

3

=

1

C

2

(R

3

+ R

4

)

(1)

where k

DAC2

is the feedback coefficient of DAC2. Based

on (1), Fig. 5 shows the STF and NTF of the modulator

with and without the passive integrator. The STF peak results

from the CIFF-FB architecture, which has the feedforward

path in the LF. When compared with the STF of the ideal

3rd-order modulator, the STF peak drops from 5.1 to 4.8 dB

because the non-ideal effect of the passive integrator. A zero

of the NTF is pushed away from DC to the left plane

on the S-domain with the location of the zero determined

by k3. It worsens the inband quantization noise attenuation

of the modulator. But the influence is not significant when the

bandwidth of the modulator is small. Fig. 6 shows the peak

SQNR of the 2nd-order LF, 3rd-order LF, and 2nd-order LF +

passive integrator modulator under various out-of-band gains.

If compared with the ideal 3rd-order LF, the SQNR of the

passive integrator drops from 107 to 101 dB. Such influence

is negligible since our target is around 82 dB. On the other

hand, the passive integrator combined with the 2nd-order LF

enables an improvement of ∼10 dB in the SQNR with a small

power overhead.

In the proposed modulator the passive integrator is also used

as a passive adder to achieve ELD compensation. The feedback

current of DAC2 is added at the output of the LF where its

swing is small because of the passive integrator’s attenuation.