Verilog HDL整合篇:循环、时序与优化

"《Verilog那些事儿-整合篇》深入探讨了Verilog HDL在设计中的整合技术,包括计数器/定时器的整合、循环结构的实现、理想时序与物理时序的融合、精密控时以及模块的优化与平衡。书中详细阐述了如何在Verilog中模拟for和while等循环,并强调理解理想时序和硬件时序之间的关系对于高效设计的重要性。此外,还介绍了主动式设计方法以实现精密控时,避免传统被动设计的繁琐。书中的亮点还包括对浮点数运算的讲解,弥补了Verilog中相关资料的不足,为后续的优化章节提供了素材。"

在Verilog HDL的整合篇中,作者首先指出,整合建模和时序设计是关键的技能。书中详细讨论了如何将计数器和定时器无缝地融入到设计流程中,同时提高模块的可读性和可扩展性。这对于大型系统级设计尤为重要,因为它涉及到模块间的协调和通信。

接着,作者提到在Verilog中实现for和while等循环的挑战。虽然可以模拟这些顺序语言的特性,但随着对Verilog不同执行模式的理解加深,直接使用基础构造实现循环更为有效。这一部分探讨了如何利用Verilog的控制流结构,如always块和if-else语句,来创建等效的循环逻辑。

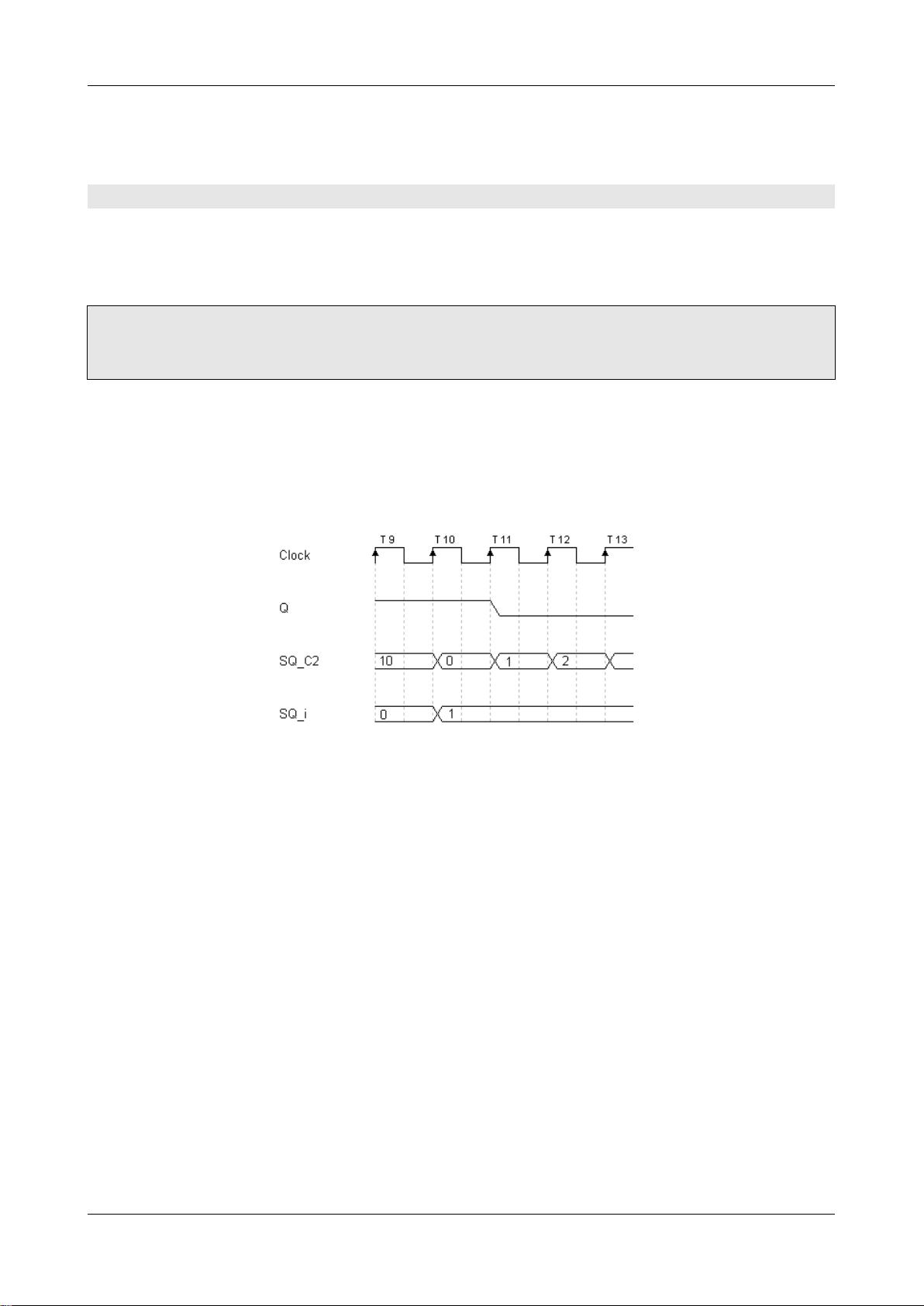

在理想时序与物理时序的整合部分,作者强调理解两者的区别和联系是至关重要的。理想时序代表Verilog代码的行为模型,而物理时序则对应实际硬件的执行。通过掌握两者的“黏糊点”,设计者能够编写出既符合行为描述又满足硬件约束的模块。这部分内容对于确保设计的正确性和可综合至关重要。

书中的“精密控时”章节介绍了两种设计方法:传统的被动设计和主动式设计。被动设计依赖于仿真来调整时序,耗时且效率低下。而主动式设计则提倡在编码阶段就考虑精确的时序控制,结合理想时序建模和仿顺序操作,能够更高效地实现复杂的时序需求。

最后,模块的优化和平衡是整合篇的另一个焦点。这一章节讨论了如何通过改进代码结构和算法来提高设计性能,同时保持面积和功耗的平衡。作者特别提到了对浮点数运算的处理,这是Verilog资料中相对稀缺的内容,他提供了浮点加、减、乘、除的实现原理,不仅丰富了Verilog设计的知识库,也为模块优化提供了实用案例。

《Verilog那些事儿-整合篇》深入剖析了Verilog HDL在设计整合中的多方面技巧,是学习和提高Verilog设计能力的宝贵资源。

115 浏览量

110 浏览量

2019-07-11 上传

2021-08-11 上传

2021-08-12 上传

215 浏览量

2024-06-05 上传

184 浏览量

138 浏览量

qqFWW

- 粉丝: 0

最新资源

- RabbitMQ订阅模式压力测试与性能分析

- 配套网页设计的图片资源压缩包

- SpringBoot集成Mybatis与Quartz的高级技术应用

- Matlab编辑器文件自动恢复功能实现

- Rust宏:const_random! 在编译时生成随机常量

- 使用pandas实现Excel数据操作与分析教程

- OpenCv2在C++中的应用与实践指南

- UCB算法与程序设计课程主要内容概述

- 易语言JSON模块修改版特性解析及使用

- Vivado环境下ZedBoard上实现PL流水灯教程

- TeXPower开源软件:动态LaTeX在线演示解决方案

- 全面解析开发套件:CLI与Angular SDK

- MySQL国家行政代码包,数据库开发者的福音

- 笔记本端一键开启WiFi热点共享技巧

- Matlab环境配置:启动脚本与日记功能

- 火星车导航优化与通信自检技术研究