没有合适的资源?快使用搜索试试~ 我知道了~

首页联想B520E LA-7811P电路图纸R01:保密工程图纸

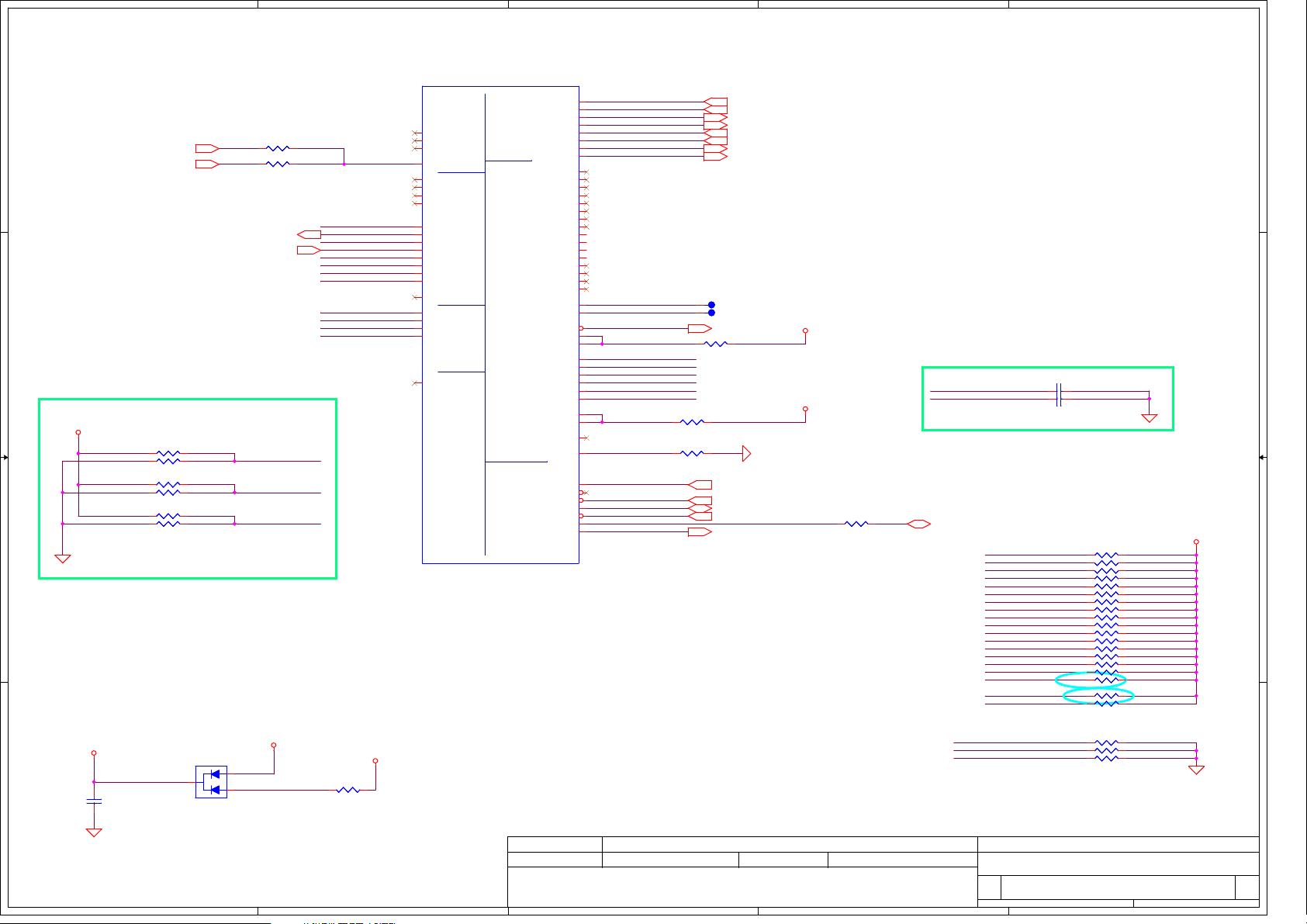

联想B520E LA-7811P电路图纸R01:保密工程图纸

需积分: 9 2 下载量 164 浏览量

更新于2024-07-17

收藏 1.68MB PDF 举报

联想B520E LA-7811P r01.pdf 是一份专属于Compaq Electronics, Inc. 的电路图纸文档,具体涉及到BLA-7811P型号的产品。这份图纸包含了LA-7811PR1A_0616B版本的内容,设计日期为2011年6月9日,解密日期为2010年7月20日至2011年7月20日之间。电路图详尽地展示了该产品内部组件的布局、连接和功能,包括部分标识如A、B、C、D和E,它们可能是电路板的不同区域或者关键部件。 标题"QLA01M/BLA-7811PSchematic1.A"表明这是一个系统或模块的电路图设计,可能是主板或特定子系统的图纸。"CoverPage"可能包含基本信息,如制造商(Compal Electronics, Inc.)、图纸大小、文档编号、修订版本以及安全分类和保密条款。图纸被列为公司专有财产,不得未经授权从研发部门的相关部门转移,也不得未经Compaq Electronics, Inc. 的书面许可对外公开或泄露给第三方。 电路图中的每一部分都可能对应着电路原理、元器件规格、信号路径、电源管理、接口连接等关键信息,对于电子工程师、硬件维修人员以及产品开发人员来说,这是理解B520E LA-7811P系统工作原理和技术细节的重要参考资料。通过分析这些图纸,技术人员可以进行故障诊断、升级改进或定制化开发,确保产品的性能和稳定性。 在阅读和使用这份图纸时,必须遵循严格的保密协议,确保公司的知识产权和商业秘密得到保护。理解并遵守这些规定是所有相关人员的责任,以维护良好的商业合作关系和行业道德。

资源详情

资源推荐

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_B_D0

DDR_B_D1

DDR_B_DM0

DDR_B_D2

DDR_B_D3

DDR_B_D8

DDR_B_D9

DDR_B_DQS#1

DDR_B_DQS1

DDR_B_D10

DDR_B_D11

DDR_B_D16

DDR_B_D17

DDR_B_DQS#2

DDR_B_DQS2

DDR_B_D18

DDR_B_D19

DDR_B_D24

DDR_B_D25

DDR_B_DM3

DDR_B_D26

DDR_B_D4

DDR_B_D5

DDR_B_DQS#0

DDR_B_DQS0

DDR_B_D22

DDR_B_D20

SM_DRAMRST#

DDR_B_DM1

DDR_B_D23

DDR_B_D21

DDR_B_DQS#3

DDR_B_D14

DDR_B_DM2

DDR_B_DQS3

DDR_B_D7

DDR_B_D6

DDR_B_D15

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D12

DDR_B_D31

DDR_B_D13

DDR_B_MA15

DDR_B_D61

DDR_B_DQS#7

DDR_B_DQS7

D_CK_SDATA

D_CK_SCLK

DDR_B_D62

DDR_B_D63

DDR_B_MA7

DDR_B_D52

DDR_B_ODT0

DDR_B_MA14

DDR_B_D37

DDR_B_D36

DDR_B_MA6

DDR_B_D44

DDR_B_D54

DDR_B_D53

DDR_B_D46

DDR_B_CKE1

DDR_B_MA4

DDR_B_D45

DDR_B_D38

DDR_B_BS1

DDR_B_D55

DDR_B_D47

DDR_B_ODT1

DDR_B_CLK1

DDR_B_RAS#

DDR_B_DM6

DDR_B_CLK1#

DDR_B_MA2

DDR_B_DQS#5

DDR_B_DM4

DDR_B_MA11

DDR_B_D60

DDR_B_D39

DDR_B_MA0

DDR_B_DQS5

DDR_B_CS0#

DDR_B_BS2

DDR_B_MA12

DDR_B_MA9

DDR_B_MA8

DDR_B_MA5

DDR_B_MA3

DDR_B_MA1

DDR_B_CLK0

DDR_B_CLK0#

DDR_B_MA10

DDR_B_BS0

DDR_B_WE#

DDR_B_CAS#

DDR_B_MA13

DDR_B_CS1#

DDR_B_D32

DDR_B_D33

DDR_B_DQS#4

DDR_B_DQS4

DDR_B_D34

DDR_B_D35

DDR_B_D40

DDR_B_D41

DDR_B_DM5

DDR_B_D42

DDR_B_D43

DDR_B_D48

DDR_B_D49

DDR_B_DQS#6

DDR_B_DQS6

DDR_B_D50

DDR_B_D51

DDR_B_D27

DDR_B_D56

DDR_B_D57

DDR_B_DM7

DDR_B_CKE0

DDR_B_D58

DDR_B_D59

DDR_B_DM1

DDR_B_DM5

DDR_B_DM2

DDR_B_DM6

DDR_B_DM3

DDR_B_DM0

DDR_B_DM7

DDR_B_DM4

+VREF_CB

+DIMM1_VREF

+DIMM1_VREF

+1.5V +1.5V

+V_DDR_REFB

+0.75VS

+1.5V

+3VS

+0.75VS

+3VS

+1.5V

+DIMM1_VREF

+1.5V

+1.5V

+0.75VS

DDR_B_CKE06

DDR_B_BS26

DDR_B_CLK0#6

DDR_B_CLK06

DDR_B_BS06

DDR_B_CAS#6

DDR_B_WE#6

DDR_B_CS1#6

DDR_B_DQS#[0..7] 6

DDR_B_DQS[0..7] 6

DDR_B_D[0..63] 6

DDR_B_MA[0..15] 6

D_CK_SDATA 10,13

D_CK_SCLK 10,13

DDR_B_CKE1 6

DDR_B_CLK1# 6

DDR_B_CLK1 6

DDR_B_BS1 6

DDR_B_RAS# 6

DDR_B_CS0# 6

DDR_B_ODT0 6

DDR_B_ODT1 6

SM_DRAMRST# 6,10

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

DDRIII CHANNELB

Custom

11 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

DDRIII CHANNELB

Custom

11 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

DDRIII CHANNELB

Custom

11 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Compal Electronics, Inc.

Layout Note: Place near JDIMMB

All VREF traces should

have 10 mil trace width

<Address: 01>

Layout Note:

Place near JDIMMB

Layout Note:Place C124 on Bottom Layer at DIMM

close to CPU

Layout Note:Place near JDIMM4.203/204

10/23 Change symbol of C129 from SGA20331E10 to SF000002M00

11/2 Change PN of C129 from SF000002M00 to SF000001K00

STANDARD:9.2mm

C125

0.1U_0402_16V4Z

C125

0.1U_0402_16V4Z

1

2

R45

1K_0402_1%

R45

1K_0402_1%

12

C121

1U_0402_6.3V6K

@

C121

1U_0402_6.3V6K

@

1

2

C134

2.2U_0603_6.3V6K

C134

2.2U_0603_6.3V6K

1

2

C135

0.1U_0402_16V4Z

C135

0.1U_0402_16V4Z

1

2

R41 0_0402_5%R41 0_0402_5%

1 2

C130

10U_0603_6.3V6M

C130

10U_0603_6.3V6M

1

2

R36

1K_0402_1%

R36

1K_0402_1%

12

R39 0_0402_5%R39 0_0402_5%

1 2

C140

4.7U_0603_6.3V6K

C140

4.7U_0603_6.3V6K

1

2

C127

10U_0603_6.3V6M

@

C127

10U_0603_6.3V6M

@

1

2

C295

0.1U_0402_16V4Z

C295

0.1U_0402_16V4Z

1

2

C128

10U_0603_6.3V6M

@

C128

10U_0603_6.3V6M

@

1

2

C143

2.2U_0603_6.3V6K

C143

2.2U_0603_6.3V6K

1

2

R42 0_0402_5%R42 0_0402_5%

1 2

R49

10K_0402_5%

R49

10K_0402_5%

12

C123

10U_0603_6.3V6M

C123

10U_0603_6.3V6M

1

2

R43 0_0402_5%R43 0_0402_5%

1 2

R34

0_0402_5%

R34

0_0402_5%

1 2

R47

10K_0402_5%

R47

10K_0402_5%

12

C120

1U_0402_6.3V6K

C120

1U_0402_6.3V6K

1

2

C122

1U_0402_6.3V6K

@

C122

1U_0402_6.3V6K

@

1

2

R38 0_0402_5%R38 0_0402_5%

1 2

R44 0_0402_5%R44 0_0402_5%

1 2

R40 0_0402_5%R40 0_0402_5%

1 2

R35

1K_0402_1%

R35

1K_0402_1%

12

C133

10U_0603_6.3V6M

@

C133

10U_0603_6.3V6M

@

1

2

C138

0.1U_0402_16V4Z

C138

0.1U_0402_16V4Z

1

2

JDIMM1

SUYIN_600023HB204G208ZL

CONN@

JDIMM1

SUYIN_600023HB204G208ZL

CONN@

VREF_DQ

1

VSS1

2

VSS2

3

DQ4

4

DQ0

5

DQ5

6

DQ1

7

VSS3

8

VSS4

9

DQS#0

10

DM0

11

DQS0

12

VSS5

13

VSS6

14

DQ2

15

DQ6

16

DQ3

17

DQ7

18

VSS7

19

VSS8

20

DQ8

21

DQ12

22

DQ9

23

DQ13

24

VSS9

25

VSS10

26

DQS#1

27

DM1

28

DQS1

29

RESET#

30

VSS11

31

VSS12

32

DQ10

33

DQ14

34

DQ11

35

DQ15

36

VSS13

37

VSS14

38

DQ16

39

DQ20

40

DQ17

41

DQ21

42

VSS15

43

VSS16

44

DQS#2

45

DM2

46

DQS2

47

VSS17

48

VSS18

49

DQ22

50

DQ18

51

DQ23

52

DQ19

53

VSS19

54

VSS20

55

DQ28

56

DQ24

57

DQ29

58

DQ25

59

VSS21

60

VSS22

61

DQS#3

62

DM3

63

DQS3

64

VSS23

65

VSS24

66

DQ26

67

DQ30

68

DQ27

69

DQ31

70

VSS25

71

VSS26

72

A12/BC#

83

A11

84

A9

85

A7

86

VDD5

87

VDD6

88

A8

89

A6

90

CKE0

73

CKE1

74

VDD1

75

VDD2

76

NC1

77

A15

78

BA2

79

A14

80

VDD3

81

VDD4

82

A5

91

A4

92

VDD7

93

VDD8

94

A3

95

A2

96

A1

97

A0

98

VDD9

99

VDD10

100

CK0

101

CK1

102

CK0#

103

CK1#

104

VDD11

105

VDD12

106

A10/AP

107

BA1

108

BA0

109

RAS#

110

VDD13

111

VDD14

112

WE#

113

S0#

114

CAS#

115

ODT0

116

VDD15

117

VDD16

118

A13

119

ODT1

120

S1#

121

NC2

122

VDD17

123

VDD18

124

NCTEST

125

VREF_CA

126

VSS27

127

VSS28

128

DQ32

129

DQ36

130

DQ33

131

DQ37

132

VSS29

133

VSS30

134

DQS#4

135

DM4

136

DQS4

137

VSS31

138

VSS32

139

DQ38

140

DQ34

141

DQ39

142

DQ35

143

VSS33

144

VSS34

145

DQ44

146

DQ40

147

DQ45

148

DQ41

149

VSS35

150

VSS36

151

DQS#5

152

DM5

153

DQS5

154

VSS37

155

VSS38

156

DQ42

157

DQ46

158

DQ43

159

DQ47

160

VSS39

161

VSS40

162

DQ48

163

DQ52

164

DQ49

165

DQ53

166

VSS41

167

VSS42

168

DQS#6

169

DM6

170

DQS6

171

VSS43

172

VSS44

173

DQ54

174

DQ50

175

DQ55

176

DQ51

177

VSS45

178

VSS46

179

DQ60

180

DQ56

181

DQ61

182

DQ57

183

VSS47

184

VSS48

185

DQS#7

186

DM7

187

DQS7

188

VSS49

189

VSS50

190

DQ58

191

DQ62

192

DQ59

193

DQ63

194

VSS51

195

VSS52

196

SA0

197

EVENT#

198

VDDSPD

199

SDA

200

SA1

201

SCL

202

VTT1

203

VTT2

204

G1

205

G2

206

R37 0_0402_5%R37 0_0402_5%

1 2

R46

1K_0402_1%

R46

1K_0402_1%

12

C142

0.1U_0402_16V4Z

C142

0.1U_0402_16V4Z

1

2

C126

1U_0402_6.3V6K

C126

1U_0402_6.3V6K

1

2

C131

10U_0603_6.3V6M

@

C131

10U_0603_6.3V6M

@

1

2

C124

0.1U_0402_16V4Z

C124

0.1U_0402_16V4Z

1

2

+

C129

560U_2.5V_M_R10

+

C129

560U_2.5V_M_R10

12

C132

10U_0603_6.3V6M

C132

10U_0603_6.3V6M

1

2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

EC_GA20

SATA3RBIAS

SERIRQ

PCH_GPIO19

PCH_SATALED#

PCH_GPIO19

EC_KBRST#

SATA_COMP

PROJECT_ID0

PCH_SATALED#

SATA3_COMP

SERIRQ

PROJECT_ID1

CLK_BUF_PCIE_SATA#

CLK_BUF_PCIE_SATA

EC_GA20

PCH_GPIO21

PCH_GPIO21

PCH_GPIO16

PCH_GPIO16

EC_KBRST#

H_PM_SYNC

PCH_GPIO49

PCH_GPIO49

H_THERMTRIP#

PCH_GPIO17

CAM_OFF

PCH_GPIO6

PCH_GPIO68

EC_SCI#

PCH_GPIO69

PCH_GPIO70

PCH_GPIO71

PCH_GPIO22

PROJECT_ID2

PCH_GPIO48

PCH_GPIO39

PCH_GPIO17

CAM_OFF

PCH_GPIO6

EC_SCI#

PCH_GPIO68

PCH_GPIO69

PCH_GPIO70

PCH_GPIO71

PCH_GPIO22

PCH_GPIO39

PCH_GPIO48

PCH_PECI_R

CLK_BUF_PCIE_SATA#

CLK_BUF_PCIE_SATA

PROJECT_ID1

PROJECT_ID0

PROJECT_ID2

PCH_GPIO19

SATA3_COMP

SERIRQ

+RTCBATT_R

SATA_PTX_DRX_N0

SATA_PTX_DRX_P0

SATA_DTX_C_PRX_P0

SATA_DTX_C_PRX_N0

SATA_PTX_DRX_N1

SATA_PTX_DRX_P1

SATA_DTX_C_PRX_P1

SATA_DTX_C_PRX_N1

+3VS

+1.05VS_PCH

+1.05VS_PCH

+3VS

+RTCBATT

+3VSB

+RTCVCC

PCH_SATALED# 46

SERIRQ 43

EC_GA20 43

H_PECI 5,43

EC_KBRST# 43

H_PM_SYNC 5

H_THERMTRIP# 5

EC_SCI#43

CAM_OFF34

EC_REVPW ROK43

PCH_PW ROK_R13

SATA_PTX_DRX_N0 35

SATA_PTX_DRX_P0 35

SATA_DTX_C_PRX_P0 35

SATA_DTX_C_PRX_N0 35

SATA_PTX_DRX_N1 35

SATA_PTX_DRX_P1 35

SATA_DTX_C_PRX_P1 35

SATA_DTX_C_PRX_N1 35

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

PCH (1/9) SATA,FAN

Custom

12 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

PCH (1/9) SATA,FAN

Custom

12 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

PCH (1/9) SATA,FAN

Custom

12 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Compal Electronics, Inc.

Layout Note:SATA_COMP WITH LENGTH NO MORE THAN 500 MILS TO

RESISTOR.

7/30 R510--- CRB:1K ohm;EDS:10K ohm

7/30 R512--- CRB:10K ohm PD to

GND;EDS:10K ohm PU to +3VS

PROJECT ID TABLE

Boot BIOS Strap Bit 0(GPIO19)

W=20mils

W=20mils

W=20mils

SATA for HDD

SATA for ODD

R68110K_0402_5%

CONFIG1@

R68110K_0402_5%

CONFIG1@

12

C963 1000P_0402_50V7K@C963 1000P_0402_50V7K@

1 2

R512 10K_0402_5%R512 10K_0402_5%

1 2

T54T54

R347 1K_0402_1%@R347 1K_0402_1%@

1 2

R509 10K_0402_5%R509 10K_0402_5%

1 2

R68010K_0402_5%

CONFIG2@

R68010K_0402_5%

CONFIG2@

12

R56 10K_0402_5%R56 10K_0402_5%

1 2

R362 10K_0402_5%R362 10K_0402_5%

1 2

R60 10K_0402_5%R60 10K_0402_5%

1 2

R59 10K_0402_5%R59 10K_0402_5%

1 2

R58 10K_0402_5%R58 10K_0402_5%

1 2

R499 10K_0402_5%R499 10K_0402_5%

1 2

R502 10K_0402_5%R502 10K_0402_5%

1 2

R51110K_0402_5% CONFIG3@R51110K_0402_5% CONFIG3@

12

R20910K_0402_5%

CONFIG6@

R20910K_0402_5%

CONFIG6@

12

R507 10K_0402_5%R507 10K_0402_5%

1 2

R53

750_0402_1%

R53

750_0402_1%

1 2

R508 10K_0402_5%R508 10K_0402_5%

1 2

T57T57

D3

DAN202UT106_SC70

D3

DAN202UT106_SC70

2

3

1

R52

49.9_0402_1%

R52

49.9_0402_1%

12

R6210K_0402_5%

CONFIG5@

R6210K_0402_5%

CONFIG5@

12

CPT_CRB

GPIO FAN CLINK

SATA2 SATA3

HOST

3 OF 10

U1C

BD82H67-SLJ49-B3_FCBGA942

CPT_CRB

GPIO FAN CLINK

SATA2 SATA3

HOST

3 OF 10

U1C

BD82H67-SLJ49-B3_FCBGA942

SCLOCK_GPIO22

BA53

SST

BC43

SLOAD_GPIO38

BE54

SDATAOUT0_GPIO39

BF55

SDATAOUT1_GPIO48

AW53

TACH0_GPIO17

BT17

TACH1_GPIO1

BR19

TACH2_GPIO6

BA22

TACH7_GPIO71

BP15

TACH6_GPIO70

BN17

NC

AY20

TACH3_GPIO7

BR16

TACH4_GPIO68

BU16

TACH5_GPIO69

BM18

PWM3

BN19

PWM2

BM20

PWM1

BT21

PWM0

BN21

APWROK

BC46

CL_RST1#

BF49

CL_DATA1

BF50

CL_CLK1

BA50

PMSYNCH

F55

PECI

H48

THRMTRIP#

E56

SERIRQ

AV52

RCIN#

BG56

INIT3_3V#

BN56

A20GATE

BB57

SATA3RBIAS

AC52

TP16

AE50

SATA3RCOMPO

AE52

SATA3COMPI

AE54

SATA5GP_GPIO49

BA56

SATA4GP_GPIO16

AU56

SATA3GP_GPIO37

BG53

SATA2GP_GPIO36

BB55

SATA1GP_GPIO19

AY52

SATA0GP_GPIO21

BC54

SATAICOMPO

AJ53

SATAICOMPI

AJ55

SATALED#

BF57

CLKIN_SATA_P

AG56

CLKIN_SATA_N

AF55

SATA5TXP

AV49

SATA5TXN

AV50

SATA5RXP

AT44

SATA5RXN

AT46

SATA4TXP

AT49

SATA4TXN

AT50

SATA4RXP

AN50

SATA4RXN

AN49

SATA3TXP

AM55

SATA3TXN

AN56

SATA3RXP

AN44

SATA3RXN

AN46

SATA2TXP

AL53

SATA2TXN

AL56

SATA2RXP

AL49

SATA2RXN

AL50

SATA1TXP

AG47

SATA1TXN

AG49

SATA1RXP

AA56

SATA1RXN

AA53

SATA0TXP

AE44

SATA0TXN

AE46

SATA0RXP

AB55

SATA0RXN

AC56

R6110K_0402_5%

CONFIG4@

R6110K_0402_5%

CONFIG4@

12

R892 0_0402_5%R892 0_0402_5%

1 2

R51 37.4_0402_1%R51 37.4_0402_1%

1 2

R55 10K_0402_5%R55 10K_0402_5%

1 2

C293

1U_0402_6.3V6K

C293

1U_0402_6.3V6K

1

2

R513 10K_0402_5%R513 10K_0402_5%

1 2

R503 10K_0402_5%@R503 10K_0402_5%@

1 2

R891 0_0402_5%@ R891 0_0402_5%@

1 2

R361 10K_0402_5%R361 10K_0402_5%

1 2

R57 10K_0402_5%R57 10K_0402_5%

1 2

R299

1K_0402_5%

R299

1K_0402_5%

1 2

R506 10K_0402_5%R506 10K_0402_5%

1 2

R54 10K_0402_5%R54 10K_0402_5%

1 2

C996 1000P_0402_50V7K@C996 1000P_0402_50V7K@

1 2

R1110_0402_5% @ R1110_0402_5% @

1 2

R504 10K_0402_5%R504 10K_0402_5%

1 2

R505 10K_0402_5%@R505 10K_0402_5%@

1 2

R510 10K_0402_5%R510 10K_0402_5%

1 2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

PM_SLP_S4#

PCH_RTCX1

LPC_AD3

LPC_AD0

LPC_AD1

LPC_AD2

PM_SLP_S5#

PCH_RTCX2

LPC_FRAME#

PM_SLP_S3#

PCH_RTCRST#

PCH_SRTCRST#

SM_INTRUDER#

PCH_INTVRMEN

HDA_BITCLK_PCH

HDA_RST#_PCH

HDA_SDOUT_PCH

HDA_BITCLK_PCH

HDA_RST#_PCH

HDA_SYNC_AUDIO_R

HDA_SDIN0

PCH_DSWVRMEN

EC_SW I#

EC_SW I#

PCH_GPIO74

PCH_GPIO74

EC_SMB_DA2_M

EC_SMB_CK2_M PCH_SML1CLK

PCH_SML1DAT

PCH_SML1CLK

PCH_SML1DAT

LAN_SMBCLK

LAN_SMBDATA

LAN_SMBCLK

LAN_SMBDATA

PCH_GPIO60

PCH_GPIO60

PCH_SMBCLK

PCH_SMBDATA

PCH_SPI_MOSIPCH_SPI_MOSI_1

PCH_SPI_MISOPCH_SPI_MISO_1

PCH_SPI_CLK

PCH_SPI_CS0#_R

PCH_SPI_CLK_1

PCH_SPI_CS0#

PCH_SPI_CS0#

PCH_SPI_MISO_1

SPI_W P1#

PCH_SPI_MOSI_1SPI_HOLD1#

PCH_SPI_CLK_1

PCH_GPIO0

PCH_GPIO0

PCH_GPIO34

PCH_GPIO34

PCH_GPIO35

PCH_GPIO35

EC_SMI#

EC_SMI#

PM_LANPHY_ENABLE

PM_LANPHY_ENABLE

SMIB

SMIB

PCH_GPIO28

PCH_GPIO28

PCH_GPIO57

PCH_GPIO57

PCH_GPIO27

PCH_GPIO27

PCH_JTAG_RST#

PCH_JTAG_TCK

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_RST#

PCH_JTAG_TDO

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TCK

LAN_CLKREQ#

WLAN_CLKREQ#

CLKREQ_USB30#

TV_CLKREQ#

LAN_CLKREQ#

WLAN_CLKREQ#

CLKREQ_USB30#

TV_CLKREQ#

PBTN_OUT#

XDP_DBRETSET#

XDP_DBRETSET#

SYS_PWROK_R

EC_PW ROK

SYS_PWROK

VGATE

VGATE

SYS_PWROKSYS_PWROK_R

PCH_SPKR

PCH_SPKR

H_CPUPWRGD

DRAMPW ROK

DRAMPW ROK

PCH_GPIO31

PCH_GPIO31

PCH_GPIO72

PCH_GPIO72

PCH_SUSCLK_R

PCH_PCIE_WAKE#_R

SUS_PW R_ACK_R

SUSWARN#_R

PCH_PCIE_WAKE#_R

SUS_PW R_ACK_R SUSWARN#_R

PCH_PLT_RST#

SUSWARN#_R

PCH_RSMRST#

PCH_GPIO11

PCH_GPIO11

PCH_DPWROK

PCH_DPWROKPCH_RSMRST#

PCH_RSMRST#

PCH_PW ROK_R

EC_PW ROK

HDA_SDOUT_PCH

SM_INTRUDER#

PCH_INTVRMEN

PCH_DSWVRMEN

PCH_RTCX2

PCH_RTCX1

PCH_GPIO28

PCH_PW ROK_REC_PW ROK

XDP_DBRETSET#

EC_SMI#

SYS_PWROK

SUSWARN#_R

PCH_GPIO33

PCH_GPIO33

PCH_GPIO33

PCH_GPIO13

PCH_GPIO13

SLP_LAN#

SLP_LAN#

LAN_CLKREQ#

PCH_JTAG_TDO

CLKRUN#

CLKRUN#

PCH_PLT_RST#

PLT_RST#

PCH_SMBCLK

PCH_SMBDATA

D_CK_SDATAPCH_SMBDATA

PCH_SRTCRST#PCH_SRTCRST#

PCH_RTCRST#

D_CK_SCLKPCH_SMBCLK

HDA_SYNC_AUDIO_R

+3VALW

+3VS

+3VS

+3VS

+3VALW

+3VS

+3VALW

+3VALW

+RTCVCC

+3VS

+3VALW

+3VS

+3VS

+RTCVCC

+RTCVCC

+3VS

+3VS

LPC_AD343

LPC_AD043

LPC_AD143

LPC_AD243

LPC_FRAME#43

PM_SLP_S3# 43

PM_SLP_S4# 43

PM_SLP_S5# 43

HDA_BITCLK_AUDIO39

HDA_RST#_AUDIO39

HDA_SDOUT_AUDIO39

HDA_SDIN039

EC_SMB_CK2_M43

EC_SMB_DA2_M43

PCH_SMBCLK42

PCH_SMBDATA42

LAN_CLKREQ# 38

WLAN_CLKREQ# 42

CLKREQ_USB30# 36

TV_CLKREQ# 42

PBTN_OUT# 43

XDP_DBRETSET# 5

VGATE 43,57

EC_PW ROK 43

PCH_SPKR 39

H_CPUPWRGD 5

DRAMPW ROK 5

PCH_SUSCLK 43

PCH_PCIE_WAKE# 36,38,42

SUS_PW R_ACK 43

SUSWARN# 43

PCH_PLT_RST# 5,38,43

EC_RSMRST# 43

PM_LANPHY_ENABLE

EC_SMI# 36,43

SMIB 36

PCH_PW ROK_R12

ME_FLASH43

SLP_LAN# 38

CLKRUN# 43

PLT_RST# 22,36,37,42

EC_SW I# 43

D_CK_SDATA 10,11

D_CK_SCLK 10,11

HDA_SYNC_AUDIO39

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

PCH (2/9) LPC, HDA, SMBUS

Custom

13 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

PCH (2/9) LPC, HDA, SMBUS

Custom

13 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Compal Electronics, Inc.

Title

Size Document Number Rev

Date: Sheet of

Security Classification

Compal Secret Data

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Issued Date

Deciphered Date

QLA01 M/B LA-7811P Schematic

1.A

PCH (2/9) LPC, HDA, SMBUS

Custom

13 63Thursday, June 16, 2011

2010/07/20 2011/07/20

Compal Electronics, Inc.

HDA for AUDIO

SA000041P00 4MB

SPI ROM Footprint 200mil

Stuff R303 if do not support DeepSX state

Stuff R391 if EC don't want to

involve in the handshake mechanism

for the DeepSX state entry and exit

PCH_SPKR:HIGH= Enable ( No Reboot);

LOW= Disable(Default)

HDA_SDO

ME debug mode,

this signal has a weak internal pull down

Low = Disable (default)

High = Enable (flash descriptor security overide)

*

HDA_SYNC

This signal has a weak internal pull down

H=>On Die PLL is supplied by 1.5V

L=>On Die PLL is supplied by 1.8V

Need to pull high for Huron River platform

On-Die PLL Voltage Regulator

H: Enable

L: Disable

*

*

*

8/13 Add C676 close to U1(EMI request)

8/19 Change footprint of U2 to

WIESO_G6179-100000_8P

8/20 Add

RC Delay 18~25mS

close to RAM door

RC Delay 18~25mS

close to RAM door

R79 0_0402_5%R79 0_0402_5%

1 2

R1031M_0402_5% R1031M_0402_5%

12

G

D

S

Q31

SSM3K7002FU_SC70-3

G

D

S

Q31

SSM3K7002FU_SC70-3

2

1 3

R80 0_0402_5%R80 0_0402_5%

1 2

R319 4.7K_0402_5%R319 4.7K_0402_5%

1 2

J2

10K_0603_5%

@

J2

10K_0603_5%

@

1 2

R348 0_0402_5%@R348 0_0402_5%@

1 2

R356

1M_0402_5%

@

R356

1M_0402_5%

@

12

R99 20K_0402_1%R99 20K_0402_1%

1 2

R719 10K_0402_5%R719 10K_0402_5%

12

R896 10K_0402_5%R896 10K_0402_5%

12

R655

4.7K_0402_5%

R655

4.7K_0402_5%

1 2

R89 0_0402_5%R89 0_0402_5%

1 2

C148

1U_0402_6.3V6K

C148

1U_0402_6.3V6K

1 2

U25

NC7SZ08P5X_NL_SC70-5

@

U25

NC7SZ08P5X_NL_SC70-5

@

B

2

A

1

Y

4

P

5

G

3

R90 20K_0402_1%R90 20K_0402_1%

1 2

R897 1K_0402_1%@R897 1K_0402_1%@

12

T51T51

R944

100K_0402_5%

R944

100K_0402_5%

12

C9881000P_0402_50V7K @ C9881000P_0402_50V7K @

12

R531 10K_0402_5%R531 10K_0402_5%

12

T2T2

R926 10K_0402_5%@R926 10K_0402_5%@

12

C676 0.1U_0402_16V4Z

@

<EMI>

C676 0.1U_0402_16V4Z

@

<EMI>

1 2

R448 10K_0402_5%R448 10K_0402_5%

12

R9462.2K_0402_5% R9462.2K_0402_5%

1 2

R66 10K_0402_5%@R66 10K_0402_5%@

12

R87

10M_0402_5%

R87

10M_0402_5%

12

R943 0_0402_5%R943 0_0402_5%

1 2

R340 1K_0402_1%@R340 1K_0402_1%@

12

R81 0_0402_5%R81 0_0402_5%

1 2

R101 10K_0402_5%R101 10K_0402_5%

1 2

C9871000P_0402_50V7K @ C9871000P_0402_50V7K @

12

R105390K_0402_5% R105390K_0402_5%

12

R98 100_0402_5%R98 100_0402_5%

1 2

R78 10K_0402_5%R78 10K_0402_5%

12

R364 0_0402_5%R364 0_0402_5%

1 2

R342 0_0402_5%@R342 0_0402_5%@

12

R65 2.2K_0402_5%R65 2.2K_0402_5%

12

R96 4.7K_0402_5%R96 4.7K_0402_5%

1 2

C146

18P_0402_50V8J

C146

18P_0402_50V8J

12

R77 2.2K_0402_5%R77 2.2K_0402_5%

12

R71 10K_0402_5%R71 10K_0402_5%

12

R94 4.7K_0402_5%R94 4.7K_0402_5%

1 2

R343

2.2K_0402_5%

R343

2.2K_0402_5%

12

R530 10K_0402_5%R530 10K_0402_5%

12

R70

33_0402_5%

R70

33_0402_5%

1 2

D38A

BAV99DW-7-F_SOT363~N

D38A

BAV99DW-7-F_SOT363~N

1

2

6

R303 0_0402_5%R303 0_0402_5%

1 2

R85 2.2K_0402_5%R85 2.2K_0402_5%

12

R529 10K_0402_5%R529 10K_0402_5%

12

R102 51_0402_5%R102 51_0402_5%

1 2

R83 0_0402_5%R83 0_0402_5%

1 2

R64 2.2K_0402_5%R64 2.2K_0402_5%

12

U20

NC7SZ08P5X_NL_SC70-5

U20

NC7SZ08P5X_NL_SC70-5

B

2

A

1

Y

4

P

5

G

3

R74 10K_0402_5%R74 10K_0402_5%

12

R583 1K_0402_5%@R583 1K_0402_5%@

12

R654

4.7K_0402_5%

R654

4.7K_0402_5%

1 2

JTAG(SUS)

PM_GPIO(DSW)

4 OF 10

U1D

BD82H67-SLJ49-B3_FCBGA942

JTAG(SUS)

PM_GPIO(DSW)

4 OF 10

U1D

BD82H67-SLJ49-B3_FCBGA942

SPI_CS0#

AT57

SPI_CLK

AR54

SUS_STAT#_GPIO61

BN54

GPIO57

BT53

PCIECLKRQ7#_GPIO46

BP55

SMBCLK

BT47

RTCRST#

BT41

RTCX1

BR39

SPI_CS1#

AR56

RTCX2

BN39

BMBUSY#_GPIO0

AW55

CLKRUN#_GPIO32

BC56

HDA_DOCK_EN#_GPIO33

BC25

STP_PCI#_GPIO34

BL56

GPIO35

BJ57

GPIO8

BP51

LAN_PHY_PWR_CTRL_GPIO12

BK50

HDA_DOCK_RST#_GPIO13

BA25

GPIO15

BM55

GPIO27

BJ43

SLP_SUS#

BD43

PWRBTN#

BT43

SYS_RESET#

BE52

SPKR

BE56

PROCPWRGD

D53

TP12

BC49

JTAG_TCK

BA43

JTAG_TDI

BC52

JTAG_TDO

BF47

JTAG_TMS

BC50

HDA_SDO

BT23

FWH3_LAD3

BG20

SUSACK#

BP45

SUSWARN#-SUS_PWR_DN_ACK-GPIO30

BU46

FWH2_LAD2

BJ20

FWH4_LFRAME#

BG17

HDA_SDIN0

BD22

HDA_SDIN1

BF22

HDA_SDIN2

BK22

HDA_SDIN3

BJ22

HDA_RST#

BC22

HDA_BCLK

BU22

LDRQ0#

BK17

SUSCLK_GPIO62

BA47

BATLOW#_GPIO72

AV46

DRAMPWROK

BG46

GPIO31

BG43

GPIO24_MEM_LED

BP53

GPIO28

BJ55

SLP_LAN#_GPIO29

BH49

PCIECLKRQ6#_GPIO45

AV44

SLP_S5#_GPIO63

BH50

PWROK

BJ38

SPI_MOSI

AU53

LDRQ1#_GPIO23

BA20

RSMRST#

BK38

INTVRMEN

BN41

SLP_S4#

BN52

SLP_S3#

BM53

SLP_A#

BC41

WAKE#

BC44

SYS_PWROK

BJ53

RI#

BJ48

PLTRST#

BK48

PCIECLKRQ5#_GPIO44

BL54

PCIECLKRQ2#_GPIO20

AV43

HDA_SYNC

BP23

INTRUDER#

BM38

SMBDATA

BR49

SML0CLK

BT51

SML1ALERT#_PCHHOT#_GPIO74

BR46

SML1DATA_GPIO75

BK46

SML1CLK_GPIO58

BJ46

SML0DATA

BM50

SML0ALERT#_GPIO60

BU49

SMBALERT#_GPIO11

BN49

DSWVRMEN

BR42

DPWROK

BT37

SRTCRST#

BN37

SPI_MISO

AT55

FWH1_LAD1

BJ17

FWH0_LAD0

BK15

R95 100_0402_5%R95 100_0402_5%

1 2

R716 10K_0402_5%R716 10K_0402_5%

12

C149

1U_0402_6.3V6K

C149

1U_0402_6.3V6K

1 2

R350 0_0402_5%@R350 0_0402_5%@

1 2

R676 200_0402_5%R676 200_0402_5%

12

R581 10K_0402_5%R581 10K_0402_5%

12

R73 33_0402_5%R73 33_0402_5%

1 2

R349 0_0402_5%R349 0_0402_5%

1 2

R207 1K_0402_1%@R207 1K_0402_1%@

12

R100 20K_0402_5%R100 20K_0402_5%

1 2

R86 1K_0402_1%@R86 1K_0402_1%@

12

R63 4.7K_0402_5%R63 4.7K_0402_5%

12

R82 10K_0402_5%R82 10K_0402_5%

12

R75 10K_0402_5%R75 10K_0402_5%

12

R532 10K_0402_5%R532 10K_0402_5%

12

R646 200_0402_5%@R646 200_0402_5%@

12

J1

10K_0603_5%

@

J1

10K_0603_5%

@

1 2

R717

10K_0402_5%

R717

10K_0402_5%

12

R895 1K_0402_1%@R895 1K_0402_1%@

12

R84 10K_0402_5%R84 10K_0402_5%

12

R88 0_0402_5%R88 0_0402_5%

1 2

G

D

S

Q32

SSM3K7002FU_SC70-3

G

D

S

Q32

SSM3K7002FU_SC70-3

2

1 3

R365 0_0402_5%@R365 0_0402_5%@

1 2

R97 200_0402_5%R97 200_0402_5%

1 2

R68 1K_0402_1%R68 1K_0402_1%

12

R69 33_0402_5%R69 33_0402_5%

1 2

X1

32.768KHZ_12.5PF_Q13MC14610002

X1

32.768KHZ_12.5PF_Q13MC14610002

OSC

4

OSC

1

NC

3

NC

2

R67 10K_0402_5%R67 10K_0402_5%

12

R391 0_0402_5%R391 0_0402_5%

1 2

D38B

BAV99DW-7-F_SOT363~N

D38B

BAV99DW-7-F_SOT363~N

4

5

3

R890

0_0402_5%

R890

0_0402_5%

1 2

R363 0_0402_5%R363 0_0402_5%

1 2

R718 10K_0402_5%R718 10K_0402_5%

12

C

B

E

Q18

MMBT3906_SOT23-3

C

B

E

Q18

MMBT3906_SOT23-3

1

2

3

C147

18P_0402_50V8J

C147

18P_0402_50V8J

12

R390 0_0402_5%R390 0_0402_5%

1 2

R9452.2K_0402_5% R9452.2K_0402_5%

1 2

T1T1

R91 200_0402_5%R91 200_0402_5%

1 2

R203 1K_0402_1%R203 1K_0402_1%

12

R93 200_0402_5%R93 200_0402_5%

1 2

R894 10K_0402_5%R894 10K_0402_5%

12

R338 1K_0402_1%@R338 1K_0402_1%@

12

R76 4.7K_0402_5%R76 4.7K_0402_5%

12

R92 100_0402_5%R92 100_0402_5%

1 2

R344 0_0402_5%R344 0_0402_5%

1 2

R106

1K_0402_5%

@

R106

1K_0402_5%

@

12

R675 10K_0402_5%R675 10K_0402_5%

12

U2

S IC FL 32M MX25L3206EM2I-12G SOP 8P

U2

S IC FL 32M MX25L3206EM2I-12G SOP 8P

CS#

1

SO

2

WP#

3

GND

4

SI

5

SCLK

6

HOLD#

7

VCC

8

R72 33_0402_5%R72 33_0402_5%

1 2

R324 10K_0402_5%R324 10K_0402_5%

12

R104390K_0402_5% R104390K_0402_5%

12

剩余62页未读,继续阅读

kj_4

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- zlib-1.2.12压缩包解析与技术要点

- 微信小程序滑动选项卡源码模版发布

- Unity虚拟人物唇同步插件Oculus Lipsync介绍

- Nginx 1.18.0版本WinSW自动安装与管理指南

- Java Swing和JDBC实现的ATM系统源码解析

- 掌握Spark Streaming与Maven集成的分布式大数据处理

- 深入学习推荐系统:教程、案例与项目实践

- Web开发者必备的取色工具软件介绍

- C语言实现李春葆数据结构实验程序

- 超市管理系统开发:asp+SQL Server 2005实战

- Redis伪集群搭建教程与实践

- 掌握网络活动细节:Wireshark v3.6.3网络嗅探工具详解

- 全面掌握美赛:建模、分析与编程实现教程

- Java图书馆系统完整项目源码及SQL文件解析

- PCtoLCD2002软件:高效图片和字符取模转换

- Java开发的体育赛事在线购票系统源码分析

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功