Tcl与Design Compiler:环境设计规则与面积约束解析

需积分: 13 157 浏览量

更新于2024-07-15

收藏 778KB PDF 举报

"Tcl与Design Compiler 七环境设计规则和面积约束"

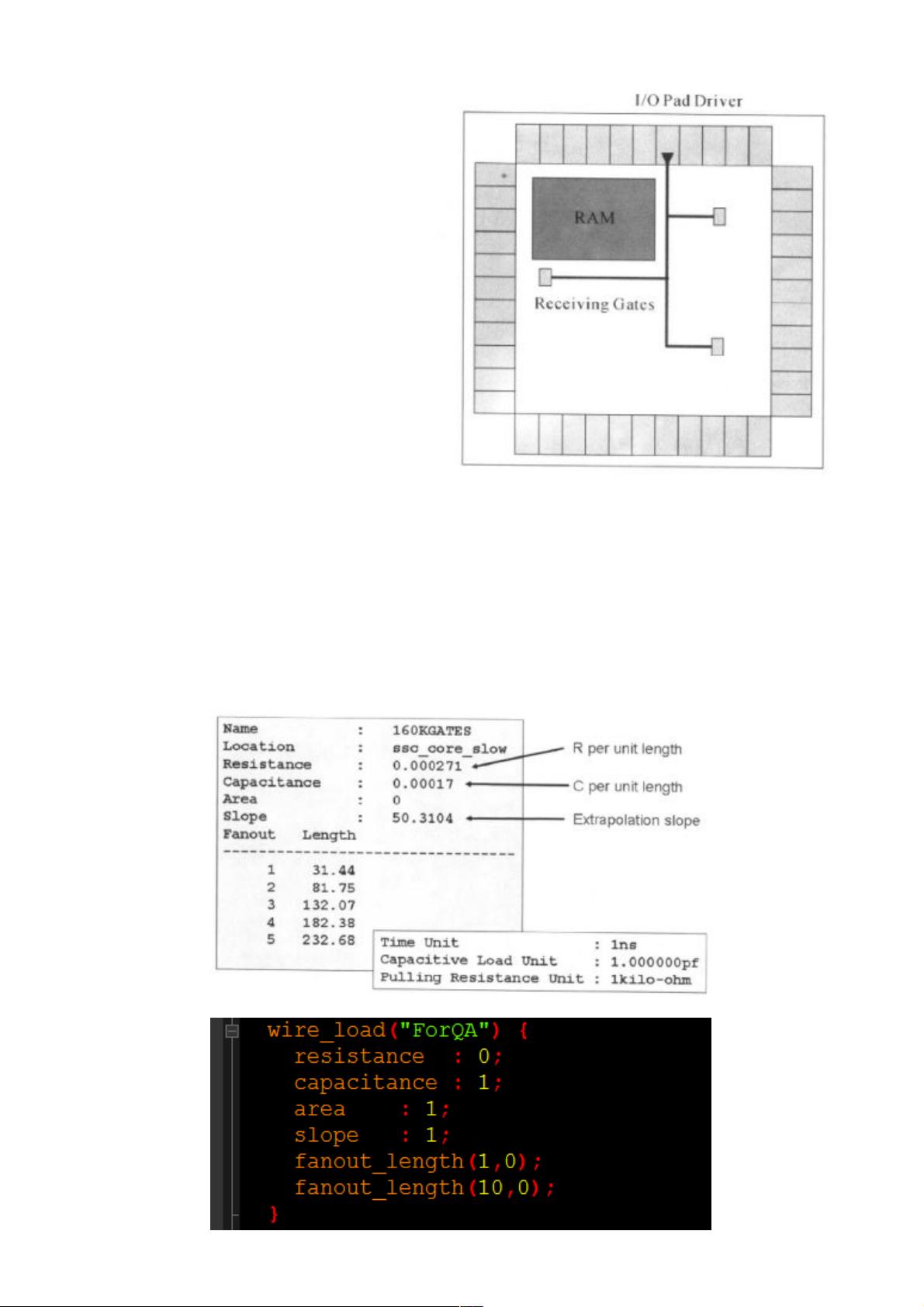

在集成电路设计中,Tcl语言常常被用来编写脚本,与Synopsys的Design Compiler (DC) 工具结合,实现自动化的设计流程控制。这篇文档主要讨论了如何使用Tcl在Design Compiler中设置环境、设计规则和面积约束,确保逻辑综合过程满足特定的要求。

首先,环境属性的约束至关重要,因为它们定义了设计将在哪种条件下运行。这些约束包括制造工艺、工作电压和温度(PVT条件),这些都是影响电路性能的关键因素。例如,`set_operating_conditions`命令用于设定这些条件,覆盖从最佳(fast)到最差(slow)的工况,以及非标准的温度和电压情况。这有助于确保设计在预期的恶劣环境下也能正常工作,并且能够准确计算出每个时序路径的延时。

接着,设计规则的约束涉及到电路的布局和布线规则,如最小线宽、最小间距、最大扇出等。这些规则由半导体制造工艺决定,必须在设计过程中严格遵循,以保证最终芯片的可制造性和可靠性。通过Tcl脚本,设计者可以将这些规则集成到DC中,使得工具在综合时自动检查和应用这些规则,避免违反规则导致的潜在问题。

然后,面积约束是另一个关键的考虑因素。在设计初期,为了满足成本和功耗目标,通常需要预估和控制芯片的面积。在Tcl中,可以使用特定的命令来设置门级或网表级别的面积目标,限制设计的规模。这可以通过设定最小和最大门数量、使用特定类型的逻辑门或者限制特定模块的大小来实现。面积约束不仅有助于优化设计的物理面积,还有助于平衡速度和功耗。

实战部分介绍了如何在DC的拓扑模式下应用这些约束。在实际设计流程中,设计者会根据项目的具体需求,编写Tcl脚本来配置环境、定义设计规则并设定面积限制。这些脚本可以自动化执行,提高设计效率,并确保每个步骤都符合预先设定的规范。

Tcl与Design Compiler的结合使用,使得设计者能精细地控制和优化数字集成电路设计的各个方面,包括工作环境、设计规则和面积。通过这种方式,可以确保设计满足功能、性能和成本目标,为半导体行业的创新和进步提供了强大的工具支持。

2019-11-26 上传

2020-12-28 上传

2020-12-28 上传

2020-12-28 上传

2020-12-28 上传

2020-12-28 上传

点击了解资源详情

2020-02-22 上传

2019-08-29 上传

壹零捌

- 粉丝: 225

- 资源: 101

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能