使用SystemVerilog的时钟域交叉设计与验证技术

需积分: 17 93 浏览量

更新于2024-07-18

收藏 552KB PDF 举报

"Cummings的《使用SystemVerilog的时钟域交叉(CDC)设计与验证技术》"

本文深入探讨了在多时钟系统中如何有效地进行时钟域穿越(Clock Domain Crossing, CDC)设计与验证。作者Clifford E. Cummings是Sunburst Design公司的创始人,他在文中详细阐述了最新的策略和最佳实践方法,以解决单个和多个信号在不同时钟域之间传递的问题。

1.0 引言

文章开头介绍了CDC设计的重要性,特别是在构建多时钟设计时,需要特别关注时钟域边界的设计。作者指出,正确处理这些边界对系统的稳定性和可靠性至关重要。

2.0 存储不稳定性(Metastability)

2.1 为何存储不稳定性是个问题?

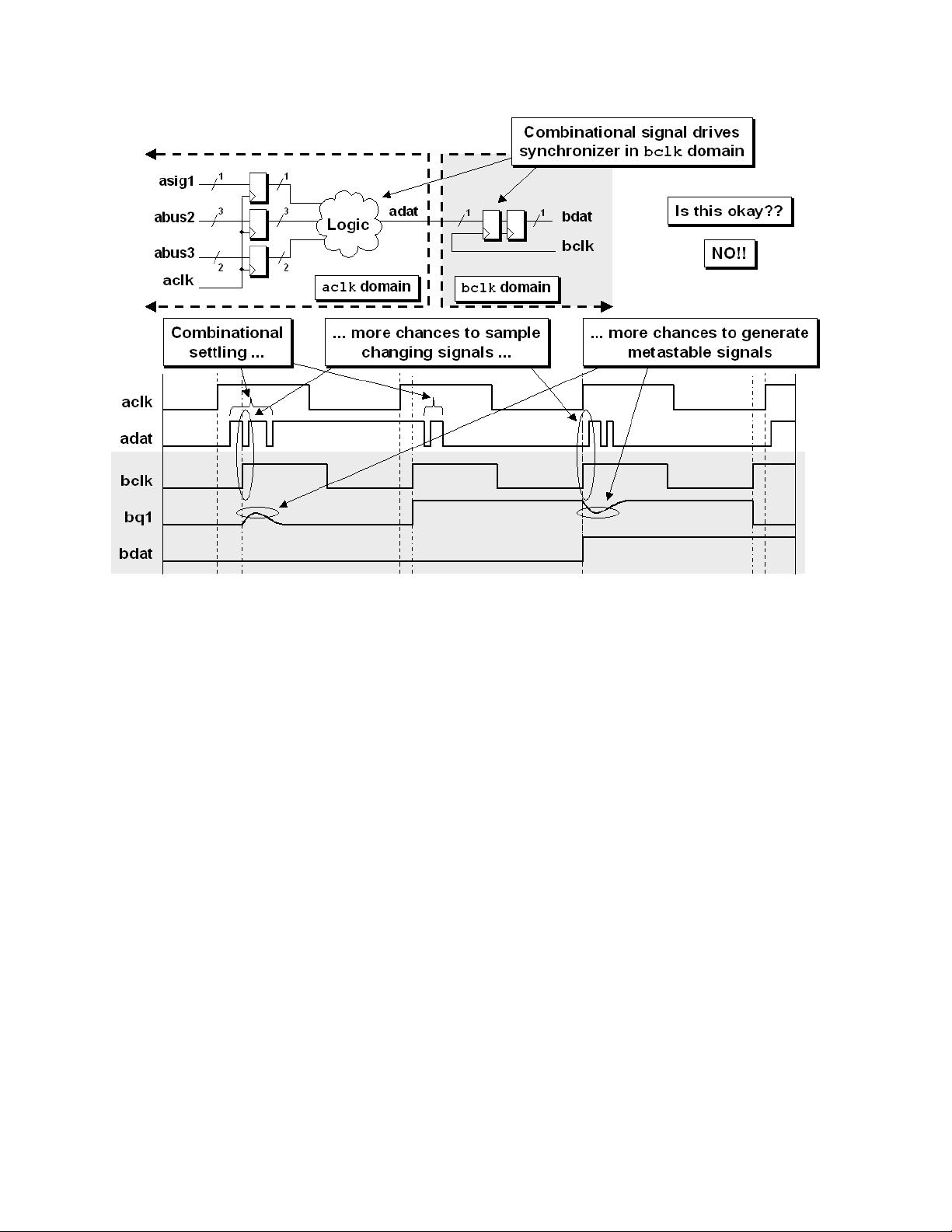

Metastability是指数字电路在两个稳定状态之间短暂而不可预测的过渡状态。在时钟域穿越中,如果信号没有被正确同步,就可能导致这种不稳定状态,进而引发错误。

3.0 同步器(Synchronizers)

3.1 两种同步场景

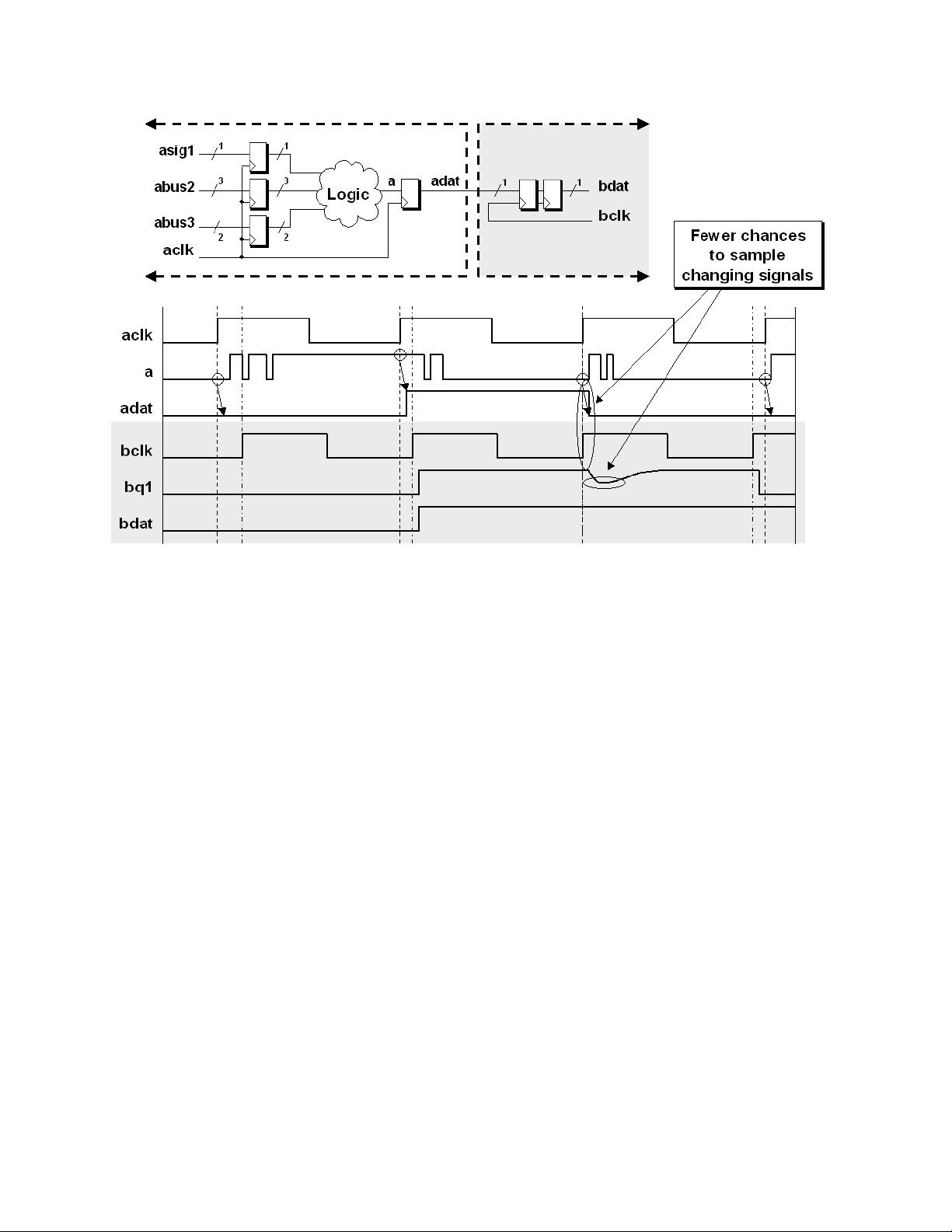

文章讨论了两种基本的同步情况:一种是简单的信号传输,另一种是需要确保数据在接收时钟域内稳定的情况。

3.2 双 flop-flop 同步器

文中介绍了使用两个触发器作为基本同步器的原理,但同时也指出这种方法并不能完全消除 metastability 的风险。

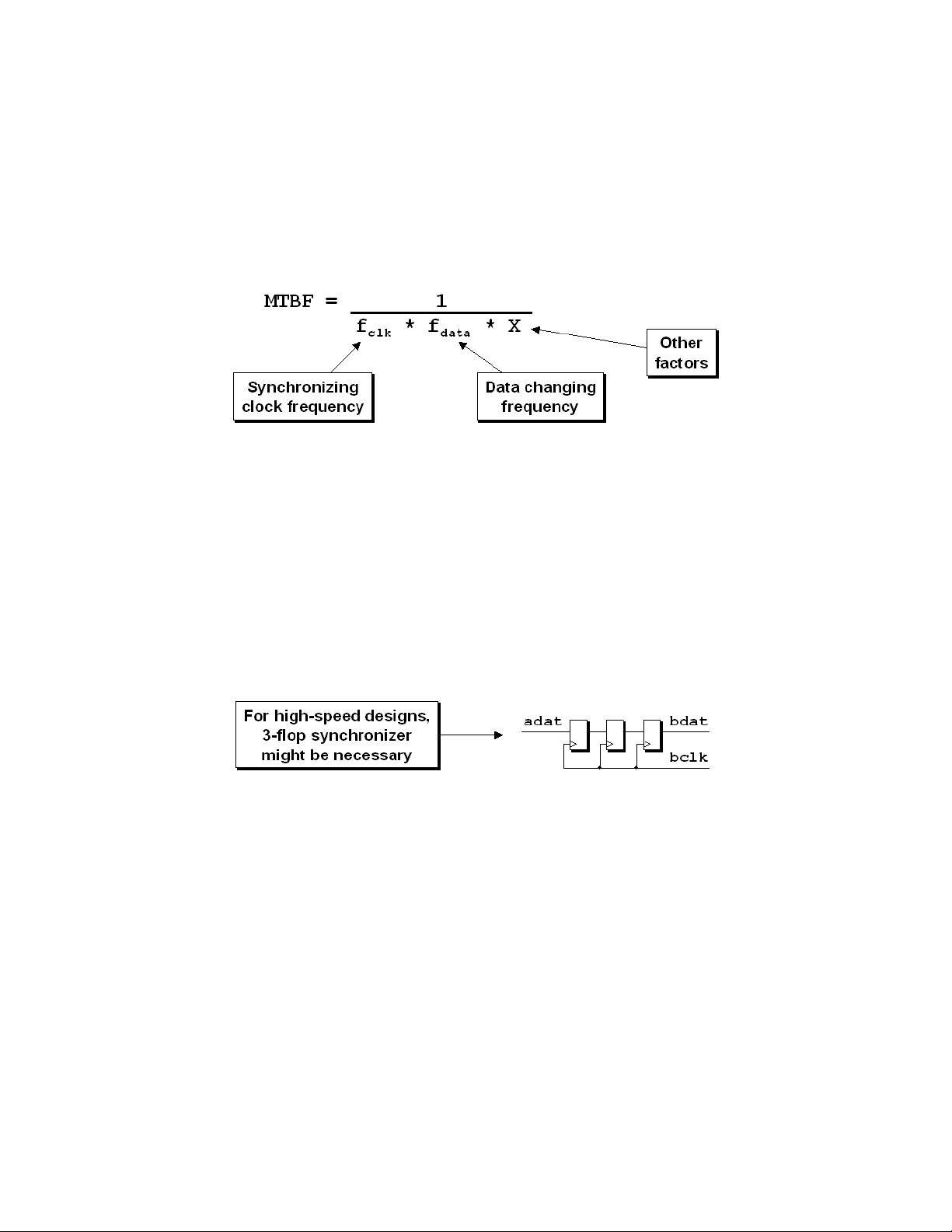

3.3 MTBF(平均故障间隔时间)

MTBF用于评估同步器的可靠性,它表示设备在出现故障之前可以正常工作的平均时间。

3.4 三 flop-flop 同步器

为了提高可靠性,通常使用三个或更多触发器构成的同步器来降低 metastability 出现的概率。

3.5 系统Verilog中的同步器优化

通过使用SystemVerilog的特性,可以实现更高效、更可靠的同步器设计,例如利用其强大的并发语句和结构化编程能力。

4.0 CDC验证

文章还涵盖了验证方面的方法,包括使用SystemVerilog的断言和覆盖机制来确保信号在穿越时钟域后的正确性。此外,还讨论了如何模拟和检测可能的metastability事件。

5.0 2-deep FIFO设计

针对多个控制信号在时钟域之间的传递,文中提出了一种有趣的两层FIFO设计,它可以有效管理多个控制信号的同步,同时减少 metastability 的风险。

6.0 结论

通过本文,读者可以了解到系统级的时钟域穿越设计和验证的关键技术,以及如何利用SystemVerilog的优势来实现高效、可靠的多时钟系统设计。

这篇论文提供了关于时钟域穿越设计与验证的全面指导,特别强调了使用SystemVerilog语言的效率和优势。对于系统级硬件设计者和验证工程师来说,这是一个宝贵的资源,有助于他们在多时钟系统设计中避免潜在的错误和不稳定状态。

2019-01-21 上传

2023-06-01 上传

2016-03-17 上传

2021-07-07 上传

2024-05-21 上传

点击了解资源详情

2024-11-25 上传

2024-11-25 上传

loglong

- 粉丝: 1

- 资源: 9

最新资源

- un-archive-my-folders:格式转换风格的 Windows 存档 - 不再有文件夹压缩综合症!

- webbundle:WebBundle库,用于打包网站

- Node.js - 安装与配置MySQL

- 创业计划书--刘明蕾-创业计划书

- 预约吧demo-易语言.zip

- weixin036在线课堂微信小程序+ssm(源码+部署说明+演示视频+源码介绍+lw).rar

- C# in DX9-DemoModelingApp-开源

- Show-DC-Presentation:javascript 画布 HTML 动画

- 基于java的医药管理系统设计(论文+源代码+毕业设计).rar

- C语言 来自11班小肖毅帆的贡献.rar

- matlab开发-wgplotwightedgraphplotabetterserversionofplot图.zip

- 创业计划书-暸望塔旅游公司创业计划书

- 2018-Yashwant-SearchByCity-ZipCode:小型OpenWeatherMap天气API解析器,任何人都可以通过键入城市的名称或邮政编码来搜索城市的天气。

- emberScheduler:灰烬中第一个正在运行的项目

- Python库 | flask_login_dictabase_blueprint-1.0.3.tar.gz

- weixin012微信小程序的科创微应用平台设计与实现+ssm(源码+部署说明+演示视频+源码介绍+lw).rar