FPGA实现的高速多路视频数据采集系统设计

版权申诉

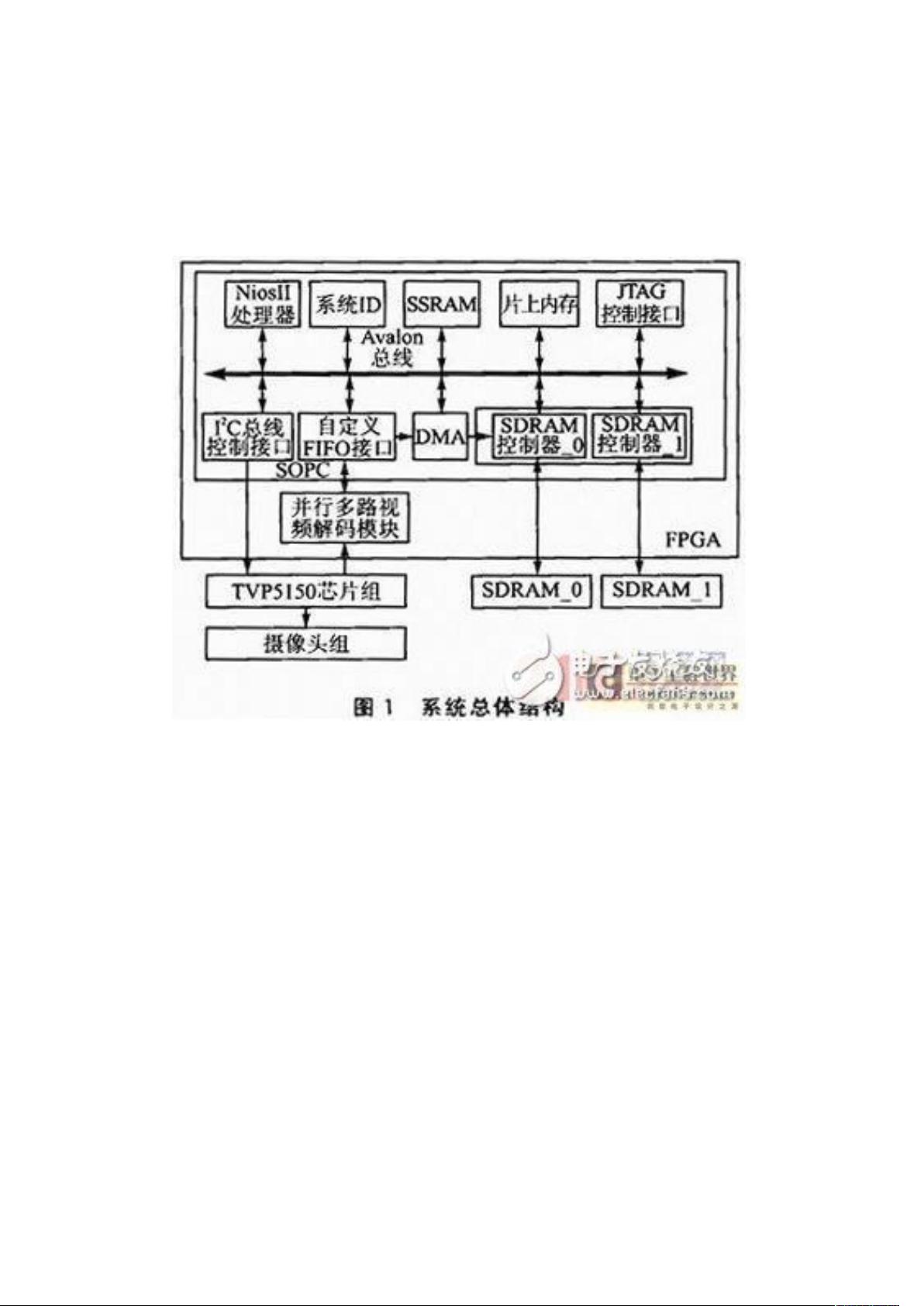

"本文详细介绍了如何设计一种基于FPGA的高速多路视频数据采集系统,该系统采用Altera公司的CycloneII系列EP2C70 FPGA芯片,能够同时处理2到6路视频信号,实现视频数据的高效解码与采集。系统基于SOPC技术,集成了NiosII软核处理器、存储器、I/O接口和自定义外设,具备高度灵活性和可重构性。NiosII CPU支持I2C总线配置,能对视频A/D采集芯片进行有效控制。系统中,自定义FIFO接口用于缓存数据,确保数据的连续性和准确性,而DMA技术则用于将数据从外设搬移到内存,减少CPU的工作负载。"

在详细设计部分,系统采用硬件描述语言(HDL)编写的视频解码模块,可以根据不同的视频编码格式进行重构,无需更改硬件设计。NiosII软核CPU具有高性能和可配置性,使得任务调度更加灵活,同时,通过NiosIDE开发环境可以轻松管理I2C总线上的设备配置。自定义FIFO接口是系统的一个关键组件,它允许根据每路视频的数据格式定制缓冲区的长度和数据宽度,确保了数据处理的适应性和效率。

系统结构上,主要包括四个主要部分:SOPC系统、多路视频解码模块、视频A/D转换芯片以及SDRAM存储器。SOPC系统利用FPGA的可编程逻辑资源,实现核心的处理功能;多路视频解码模块负责将模拟视频信号转化为数字数据;视频A/D转换芯片是采集前端,将模拟视频信号转换为数字信号;最后,SDRAM存储器作为数据存储介质,通过DMA(Direct Memory Access)技术,实现高速无CPU干预的数据传输。

该设计充分利用了FPGA的并行处理能力,增强了系统在视频数据采集和处理方面的性能。这种基于FPGA的高速多路视频数据采集系统对于需要处理大量视频流的应用,如监控、视频分析、机器视觉等,具有很高的实用价值和研究意义。通过这样的系统,可以实现实时、高效率的视频数据采集和处理,为后续的图像处理和分析提供可靠的数据基础。

2021-11-18 上传

2021-10-31 上传

2022-03-13 上传

2022-06-28 上传

2021-11-18 上传

2021-11-06 上传

2021-11-18 上传

2021-11-19 上传

ziyoudianzi15

- 粉丝: 0

最新资源

- 在ClistCtrl重绘中集成进度条控件

- 易买网电商项目:创新购物体验与技术实现

- 易语言PComm端口通信模块源码详解与应用

- PPT常用图库制作技巧与管理资源

- Informatica在AIX与Windows平台上的安装指导

- WebAssembly实现.wasm文件调用教程

- RocketMQ在Kubernetes上的YAML部署教程

- 实现xls向易语言edb数据库转换的关键技术

- Redux入门教程:Learn-Redux-Starter-Files解析

- 掌握tox插件:在当前Python环境中运行测试的技巧

- 免费获取Tomcat7与Tomcat8压缩包资源

- C++实现Huffman编码与解码技术详解

- 深度解析:知识管理的探索与思考

- 基于.NET Core和Angular的轻量级事件管理平台

- 深入解析jQuery弹出层插件nyroModal的实践应用

- 易语言HGE模块应用:源码解析与实践