VHDL语言解析:数据类型与运算操作

版权申诉

118 浏览量

更新于2024-07-03

收藏 1.12MB PPT 举报

"本资料详细介绍了VHDL语言中的数据类型和运算操作符,包括常数、变量和信号三类客体的定义、用途和特点。"

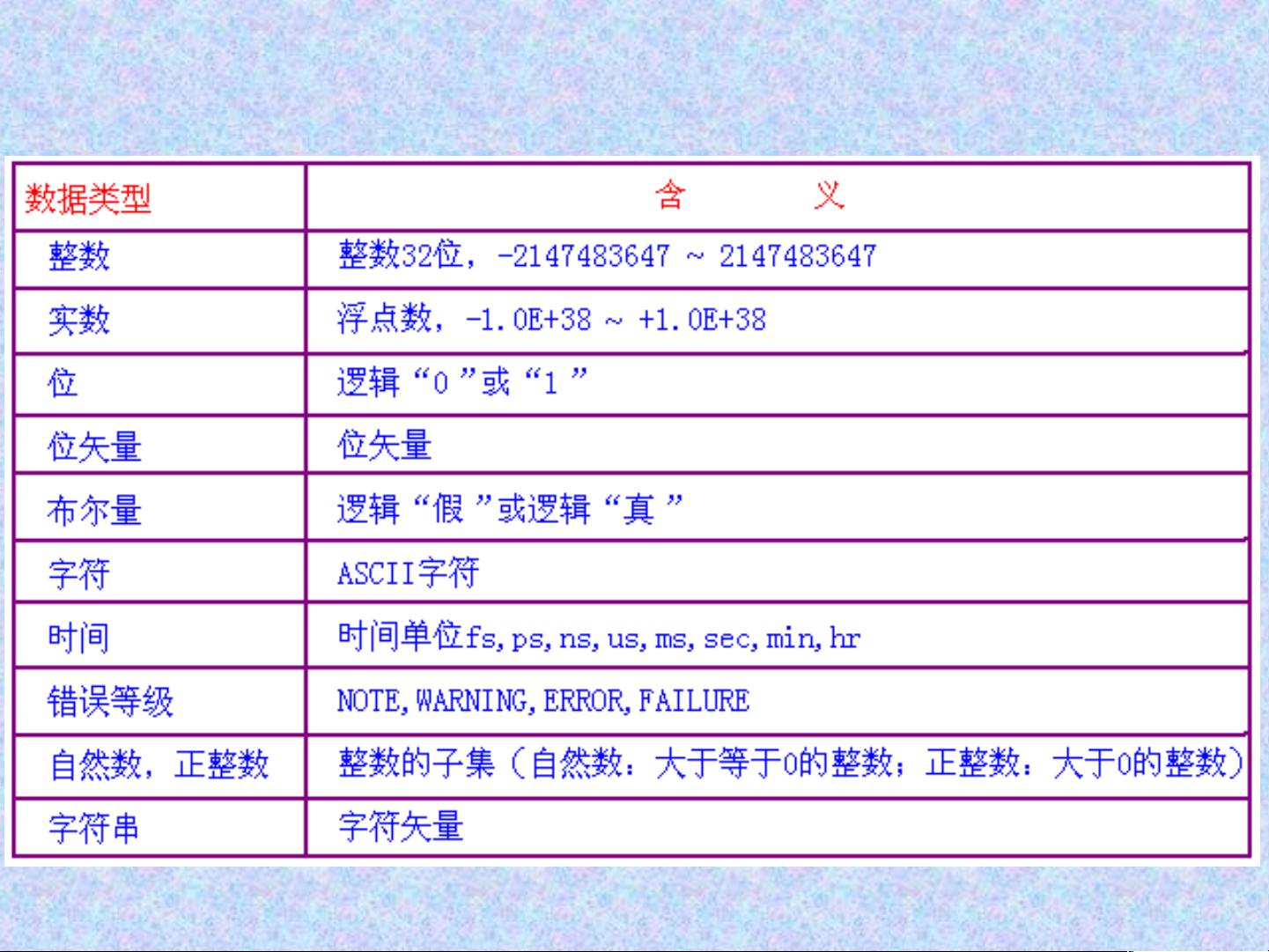

在VHDL(Very High-Speed Integrated Circuit Hardware Description Language)中,数据类型和运算操作符是构建硬件描述的关键元素。第四章主要探讨了VHDL语言中的客体,即信号、变量和常数,以及它们在电子电路设计中的意义。

首先,常数(Constant)是不可变的值,它们在程序开始前被赋值,并且在整个程序执行期间保持不变。常数说明使用`CONSTANT`关键字,指定常数名、数据类型和初始值。例如:

```vhdl

CONSTANT Vcc : REAL := 5.0;

CONSTANT DELAY : TIME := 100 ns;

CONSTANT FBUS : BIT_VECTOR := "0101";

```

这些常数在后续代码中作为固定的数值引用,如Vcc表示5.0V电压,DELAY表示100ns的时间延迟,FBUS是一个4位的二进制向量。

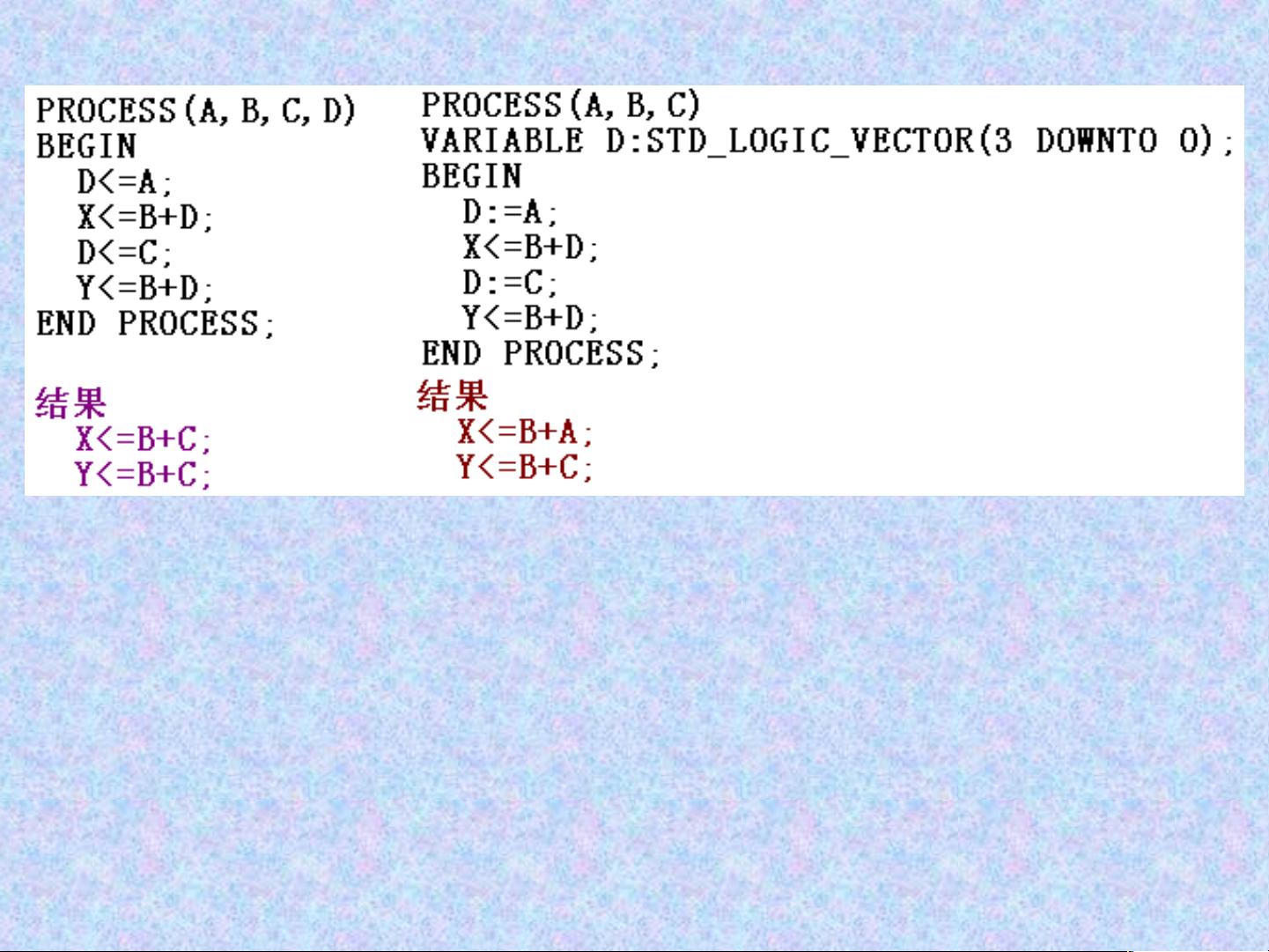

接着,变量(Variable)是局部量,仅限于进程、函数和过程语句中使用。与信号不同,变量的赋值是立即完成的,无延迟。变量声明如下:

```vhdl

VARIABLE x, y : INTEGER;

VARIABLE count : INTEGER RANGE 0 TO 255 := 10;

```

变量在仿真过程中不能模拟信号的延迟行为,因此如下的赋值语句是不合法的:

```vhdl

tmp3 := tmp1 + tmp2 AFTER 10 ns;

```

最后,信号(Signal)在VHDL中代表物理连接,它们的值会在特定时间点更新,如同电路中的电信号变化。信号的赋值可以有延迟,适合描述并行处理和时序逻辑。信号声明如下:

```vhdl

SIGNAL clk : STD_LOGIC; -- 用于表示时钟信号

SIGNAL data_in, data_out : STD_LOGIC_VECTOR(7 downto 0); -- 用于表示数据输入/输出

```

此外,VHDL还提供了丰富的运算操作符,包括算术运算符(如+、-、*、/)、比较运算符(如=、/=、<、>、<=、>=)和逻辑运算符(如AND、OR、NOT、XOR)。这些运算符允许开发者进行复杂的逻辑和数学计算,从而精确地描述硬件行为。

在实际设计中,理解并熟练掌握这些数据类型和运算操作符是实现高效、准确的VHDL代码的关键。通过合理使用常数、变量和信号,开发者能够有效地建模数字系统,进行硬件仿真和综合,最终生成适合FPGA或ASIC实现的设计。

2021-10-01 上传

2021-10-01 上传

2021-10-11 上传

点击了解资源详情

2022-07-06 上传

2021-10-07 上传

2021-10-03 上传

2021-10-07 上传

2010-05-11 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- node-silverpop:轻松访问Silverpop Engage API的Node.js实现

- 最小宽度网格图绘制算法研究

- 多数据源事务解决方案:统一管理单应用中的多数据库

- 利用Next.js匿名浏览Reddit子板块图片

- SpringBoot+H5官网模板,覆盖多种网页资源播放

- Gitshots-server:简化开源贡献的提交记录服务

- Scrapy-Dash工具:轻松生成Scrapy文档集

- Node.js v18.12.0发布,优化Linux PPC64LE服务器性能

- 蚂蚁设计专业版快速使用指南与环境配置

- Vue.js 2.3.4源码解读及开发环境配置指南

- LDBase:Lazarus开发者的dbf数据库管理开源工具

- 高效部署WordPress的VENISON脚本教程

- Saffron Bahraman-crx插件:控制产品线的栽培与培养

- Gitpod中运行前后端应用程序的指南

- Node.js v20.3.0新版本发布 - 开源跨平台JavaScript环境

- 掌握非线性方程根的迭代求解-Matlab方法实现