FPGA设计规范与Verilog语法要点解析

版权申诉

115 浏览量

更新于2024-07-04

1

收藏 2.53MB PDF 举报

本文档是关于FPGA设计的第四节,重点讲述了FPGA设计中的规则、技巧要点以及Verilog语言的常见语法。旨在帮助学习者理解如何使用Verilog有效地设计FPGA电路,避免设计混乱导致的问题。

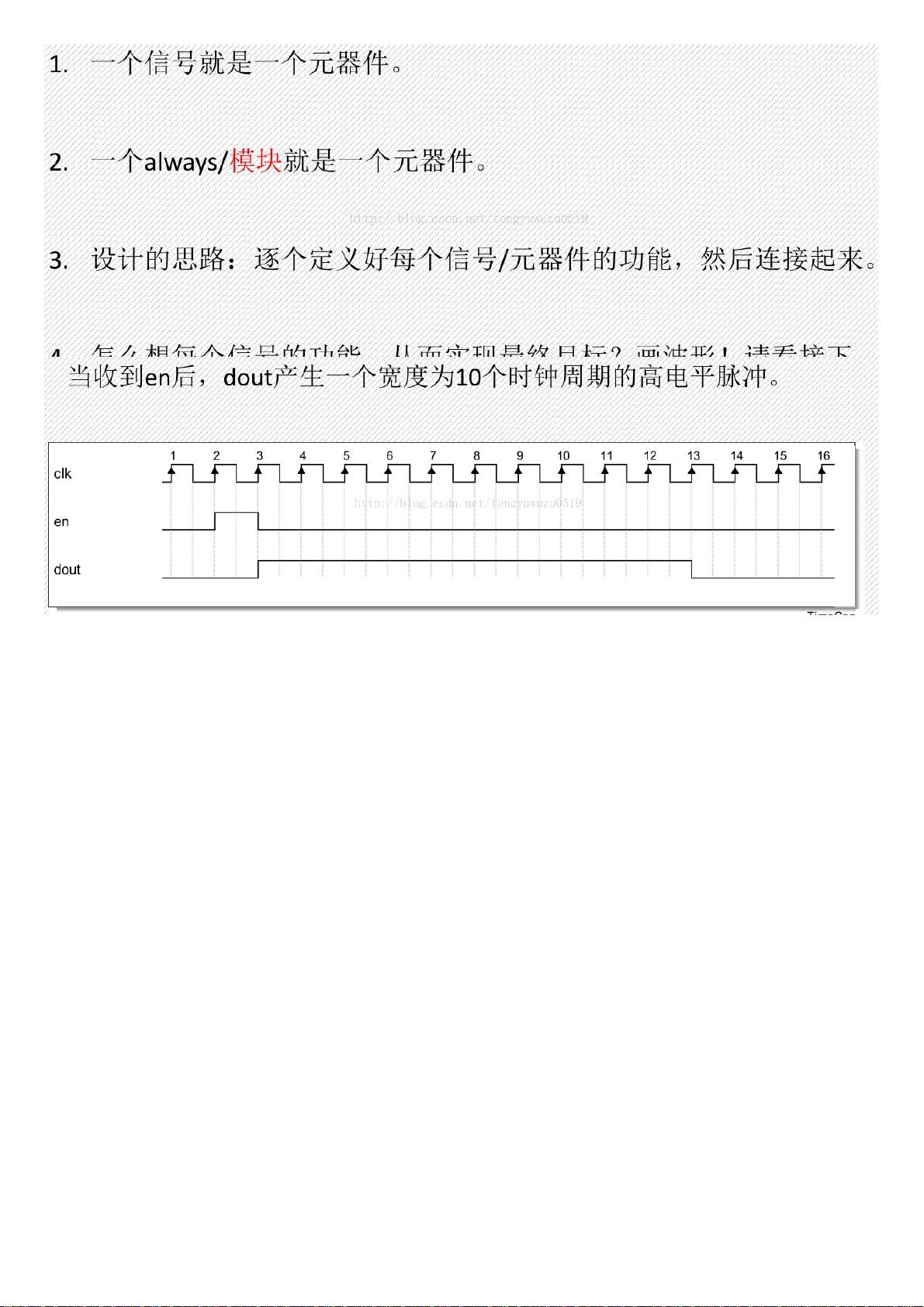

在FPGA设计中,使用Verilog语言是一种常见的方法。与C语言不同,Verilog设计需要遵循更严格的规范和逻辑,因为它是用来描述硬件电路的。设计不规范或逻辑混乱可能会导致功能无法实现,问题难以定位。为了提高设计效率和代码质量,需要了解并遵守一些设计原则。

首先,文章提到了D触发器的基础知识,这是数字电路中最基本的时序元件。D触发器在时钟上升沿到来时更新Q端的状态,如果没有时钟边沿,则Q的值保持不变。在设计时,应将D触发器视为硬件实体,并遵循并行处理的思维方式,而不是线性执行的软件思维。

接着,文章强调了设计思维的重要性,将设计看作是硬件芯片,每个部分都有其特定的功能。在设计过程中,应避免使用某些在设计阶段不必要的Verilog语法,例如`initial`、`task/function`、`for/while/repeat/forever`、`integer`、`X/Z态`、`Casex/casez`、`force/wait/fork`以及非同步延迟如`#5`等,这些通常在仿真阶段使用。同时,提倡使用如`reg/wire`、`parameter`、`assign`、`always`以及`ifelse`、`case`、算数运算符和赋值运算符等常用语法,确保设计简洁高效。

对于设计规范,推荐使用`<=`进行时序逻辑赋值,`=`用于组合逻辑赋值,以清晰地区分时序和组合逻辑。在编写代码时,尽量使用`ifelse`和`case`结构进行条件判断,以提高代码的可读性和可维护性。

这篇文档提供了一套FPGA设计的基础指导,包括Verilog语言的使用规范和设计思路,有助于初学者更好地理解和掌握FPGA设计的关键要点。通过遵循这些规则和技巧,可以避免设计中可能出现的问题,提高设计的可靠性和效率。

2022-04-22 上传

2022-04-22 上传

2023-02-27 上传

2023-02-27 上传

2023-02-27 上传

2021-10-02 上传

2021-07-13 上传

2022-04-22 上传

2021-08-11 上传

_webkit

- 粉丝: 31

- 资源: 1万+

最新资源

- 毕业设计&课设--扶贫助农管理系统-毕业设计.zip

- 3d-nii-visualizer:使用VTK和Qt5的NIfTI(nii.gz)3D可视化工具

- GoogleIntegratedSystemConky:适用于Linux用户的带有Google Keep,Google日历,系统信息和Lua时钟的Conky配置

- Qaccidentmap

- Excel模板企业付款申请单支付申请单模板.zip

- snake-test

- 毕业设计&课设--东北大学本科毕业设计 论文latex模板 .zip

- custom_timechart

- weather_app:天气应用程序,它使用openweathermap.org中的数据提供基于城市或美国邮政编码的天气状况和天气预报

- Reviewable:支持可审核

- 毕业设计&课设--大四毕业设计做的基于树莓派的人脸识别系统(调用百度云api).zip

- takimApp

- Excel模板创意进销存.zip

- bemaker:WELL项目建设者

- 编码教程:来自我的Twitch流和YouTube视频的一系列编码教程

- Operating-Systems-One:操作系统