IEEE合规Verilog设计高效可综合有限状态机策略

需积分: 10 134 浏览量

更新于2024-07-17

收藏 1.98MB PDF 举报

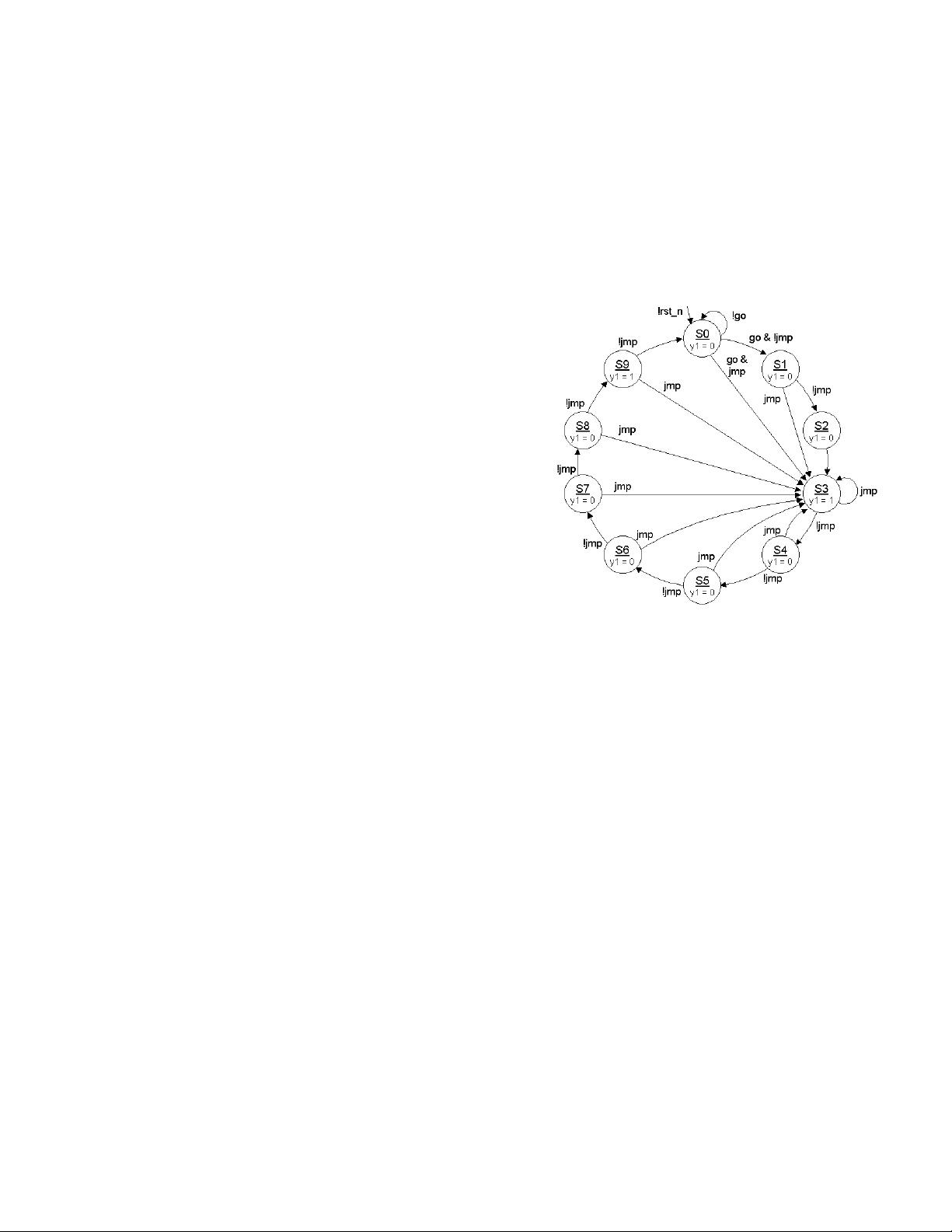

本文档深入探讨了高效可合成有限状态机(Finite State Machine, FSM)设计的基础原理,特别关注在符合IEEE标准的Verilog模拟器上实现的RTL(Register Transfer Level)编码技巧。作者Clifford E. Cummings来自Sunburst Design, Inc., 在论文中强调了一种成熟的实践方法,着重于两种常见的编码风格:单个`always`块和双`always`块。

首先,文章详细介绍了为何推荐采用双`always`块风格来编写带有组合输出的FSM。这种风格的优势在于,它有助于降低时序分析的复杂性,增强代码的可读性和一致性。通过对比,作者展示了如何有效地利用Verilog特有的“一对一”(onehot)编码方式,这在某些情况下能减少硬件资源并简化逻辑实现。

此外,论文还深入讨论了如何合理地对FSM的输出进行注册,以防止竞态条件和确保输出信号的正确性。作者澄清了一些关于错误状态编码、全案例(full-case)和并行案例(parallel-case)使用的常见误区,强调了在实际设计中的正确应用。

在标准合规性方面,论文涵盖了IEEE 1364-2001 Verilog标准的各个方面,包括设计的兼容性和可能的改进。同时,它还提到了提议的IEEE 1364.1 Verilog合成互操作性标准和Accellera SystemVerilog标准,这些新标准旨在提升设计的可合成性和可重用性。

这篇论文提供了一个实用的指南,帮助设计者优化Verilog编码,以实现高效的可合成FSM设计,同时确保遵循最新的技术规范,提高设计质量和效率。对于从事硬件开发的工程师来说,理解和掌握这些原则和技术至关重要,以应对现代集成电路设计中的挑战。

4139 浏览量

点击了解资源详情

127 浏览量

132 浏览量

2033 浏览量

197 浏览量

210 浏览量

137 浏览量

238 浏览量

drjiachen

- 粉丝: 172

- 资源: 2138

最新资源

- kindergarten

- 基于VB实现ACCESS汽车租凭管理系统(论文+系统).rar

- 软件测试工程师面试题及答案(全)文档集

- 最好用的JAVA代码混淆工具proguard-7.0.0.zip

- mixlib-cli:用于创建命令行应用程序的混合-为参数说明和处理提供了简单的DSL

- Flutter_Localizations:一个示例flutter应用程序,演示了如何使用本地化来支持2种语言

- 自平衡智能小车第二版-电路方案

- zstack.zip

- 基于MATLAB的遗传算法工具箱(51个MATLAB工具+源代码).zip

- Weights-Initialization-in-Nueral-Networks:神经网络中的权重初始化技术

- 20200917-头豹研究院-汽车应用系列深度研究:2019年中国经营性汽车租赁行业应用概览.rar

- CICD_automation

- 变频器 SINAMICS G120D,配备控制单元 CU240D-2.zip

- 耶鲁大学人脸识别数据集

- sinatra-book:正式回购到sinatrasinatra-book教程+食谱

- DFRobot_DS323X