FPGA与ADS8364实现的电能质量监测IP核设计

54 浏览量

更新于2024-09-04

收藏 229KB PDF 举报

"电能质量监测系统信号采集模块控制器IP核设计"

本文主要讨论了在电能质量监测系统中,利用FPGA(Field-Programmable Gate Array)和ADS8364芯片设计的高效信号采集模块控制器IP核。这个IP核具有接口简洁、采集精度高、多路信号同步采集以及优化CPU资源等优点,适用于高速交变电压信号的精确、实时监测。

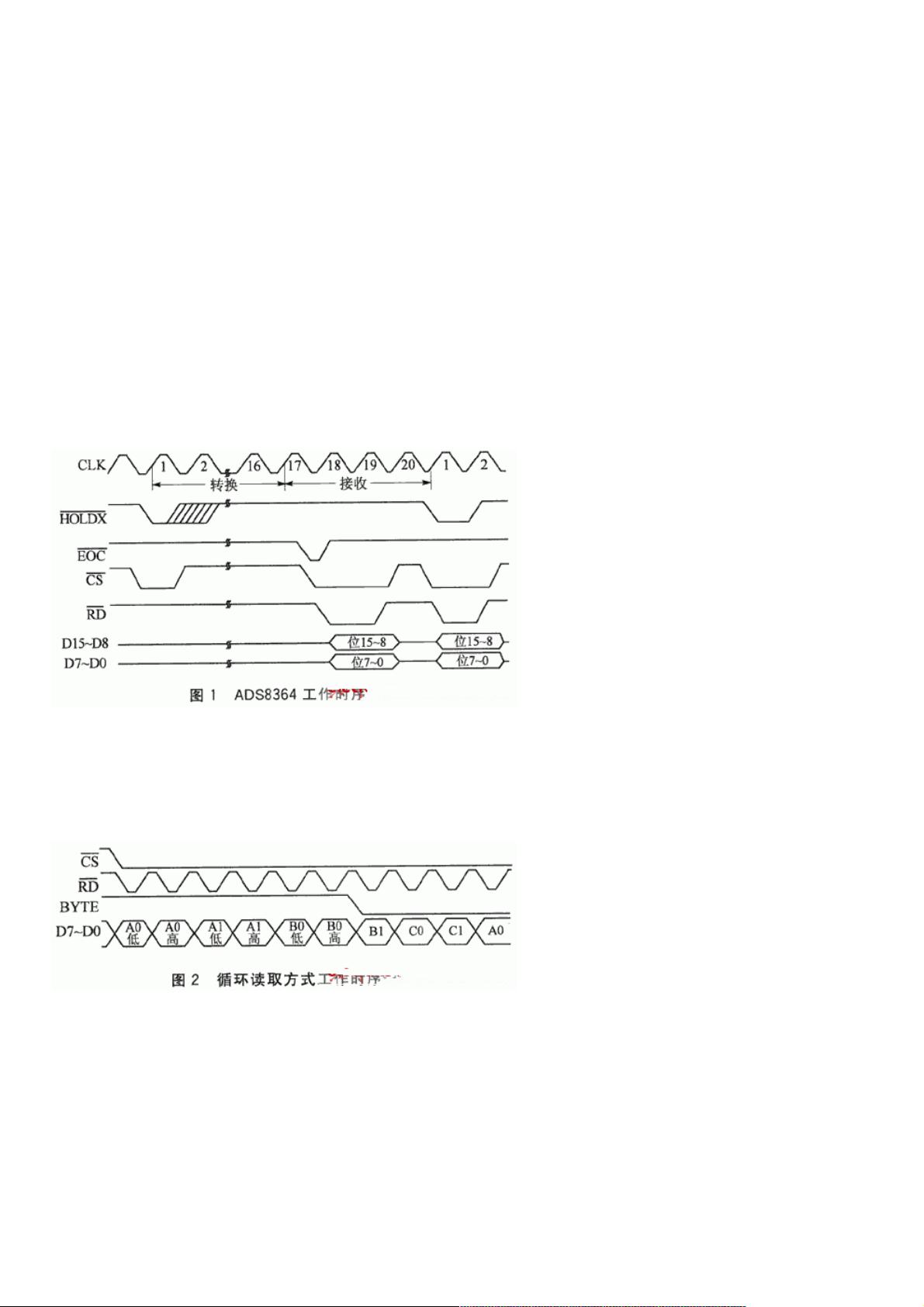

首先,ADS8364是由TI(Texas Instruments)公司生产的高速、低功耗、6通道同步采样的16位A/D转换器,特别适合于高速数据采集系统。它具备模拟参考电压输入、输出引脚和6个信号输入通道,以及数字控制引脚,如读/写、复位、片选和转换结果输出。在转换过程中,当HOLDX引脚保持低电平至少20ns时,转换启动。完成转换后,EOC引脚会给出低电平信号,指示处理器接收数据。数据的读取可以通过直接读取、循环读取或FIFO方式,具体取决于系统的数据分析处理器。

在设计中,6个通道的16位数据被存储到FPGA中的FIFO(First-In-First-Out)控制器,待存储满一个周期后,FIFO会产生中断信号,通知PowerPC处理器进行高速读取。这样避免了CPU频繁读取数据,有效降低了CPU负担,节约了宝贵的计算资源。

在实现上,通过硬件描述语言(可能包括VHDL或Verilog)对整个系统进行建模,确保ADS8364与FPGA之间的通信协调一致,满足高精度和高实时性的需求。例如,使用适当的时序控制,确保在转换数据的接收过程中,所有引脚的工作状态同步,以保证监测设备的正常运行。

此外,ADS8364的保持信号HOLDA、HOLDB和HOLDZ用于控制6个ADC的同步工作,确保所有通道在同一时刻进行采样,从而实现多通道的同步数据采集。这种设计对于监测电力系统中的电压和电流波动,以及识别谐波、电压暂降等电能质量问题至关重要。

该IP核设计充分利用了FPGA的灵活性和ADS8364的高性能特性,实现了电能质量监测系统中高效、精确的信号采集,有助于提升系统的整体性能和效率。这种解决方案对于现代电力系统监控和管理具有重要意义,特别是在分布式能源、智能电网等领域的应用中。

2021-09-06 上传

2021-10-16 上传

2020-08-12 上传

2020-10-24 上传

2021-10-16 上传

2021-10-16 上传

2012-10-24 上传

2021-10-16 上传

点击了解资源详情

weixin_38525735

- 粉丝: 3

- 资源: 881

最新资源

- Angular实现MarcHayek简历展示应用教程

- Crossbow Spot最新更新 - 获取Chrome扩展新闻

- 量子管道网络优化与Python实现

- Debian系统中APT缓存维护工具的使用方法与实践

- Python模块AccessControl的Windows64位安装文件介绍

- 掌握最新*** Fisher资讯,使用Google Chrome扩展

- Ember应用程序开发流程与环境配置指南

- EZPCOpenSDK_v5.1.2_build***版本更新详情

- Postcode-Finder:利用JavaScript和Google Geocode API实现

- AWS商业交易监控器:航线行为分析与营销策略制定

- AccessControl-4.0b6压缩包详细使用教程

- Python编程实践与技巧汇总

- 使用Sikuli和Python打造颜色求解器项目

- .Net基础视频教程:掌握GDI绘图技术

- 深入理解数据结构与JavaScript实践项目

- 双子座在线裁判系统:提高编程竞赛效率