DS90UB903Q-Q1, DS90UB904Q-Q1

ZHCSB32E –JUNE 2010–REVISED APRIL 2013

www.ti.com.cn

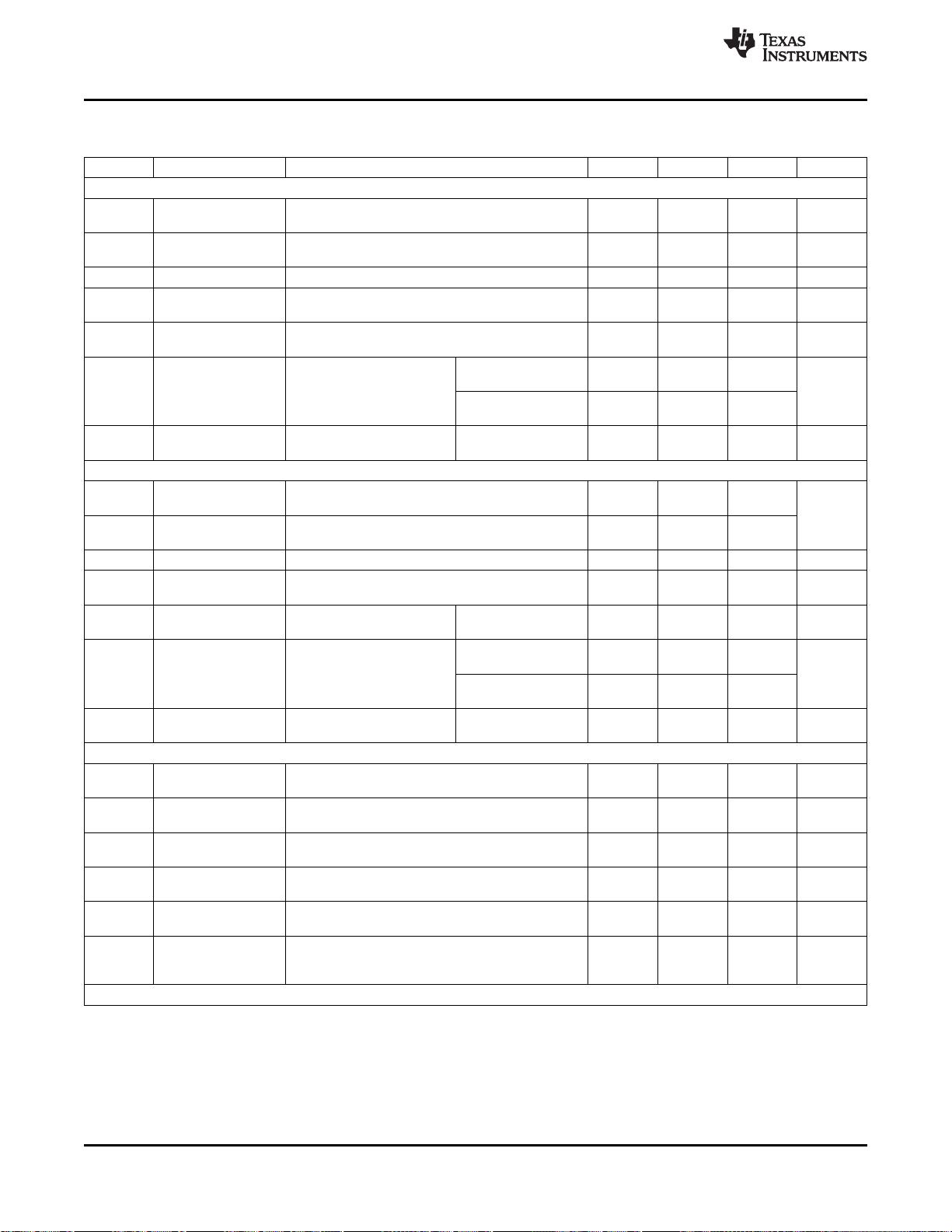

Serializer Switching Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol Parameter Conditions Min Typ Max Units

t

LHT

CML Low-to-High Transition

R

L

= 100Ω (Figure 6) 150 330 ps

Time

t

HLT

CML High-to-Low Transition

R

L

= 100Ω (Figure 6) 150 330 ps

Time

t

DIS

Data Input Setup to PCLK 2.0 ns

Serializer Data Inputs (Figure 12)

t

DIH

Data Input Hold from PCLK 2.0 ns

t

PLD

Serializer PLL Lock Time R

L

= 100Ω

(1)(2)

1 2 ms

t

SD

R

T

= 100Ω, PCLK = 10–43 MHz

6.386T 6.386T 6.386T

Serializer Delay Register 0x03h b[0] (TRFB = 1) ns

+ 5 + 12 + 19.7

(Figure 14)

t

JIND

Serializer output intrinsic deterministic

Serializer Output jitter . Measured (cycle-cycle) with

0.13 UI

Deterministic Jitter PRBS-7 test pattern

PCLK = 43 MHz

(3)(4)

t

JINR

Serializer output intrinsic random jitter

Serializer Output Random

(cycle-cycle). Alternating-1,0 pattern. 0.04 UI

Jitter

PCLK = 43 MHz

(3)(4)

t

JINT

Serializer output peak-to-peak jitter

includes deterministic jitter, random

Peak-to-peak Serializer jitter, and jitter transfer from serializer

0.396 UI

Output Jitter input. Measured (cycle-cycle) with

PRBS-7 test pattern.

PCLK = 43 MHz

(3)(4)

λ

STXBW

Serializer Jitter Transfer PCLK = 43 MHz, Default Registers

1.90 MHz

Function -3 dB Bandwidth (Figure 20)

(3)

δ

STX

Serializer Jitter Transfer PCLK = 43 MHz, Default Registers

0.944 dB

Function (Peaking) (Figure 20)

(3)

δ

STXf

Serializer Jitter Transfer

PCLK = 43 MHz, Default Registers

Function (Peaking 500 kHz

(Figure 20)

(3)

Frequency)

(1) t

PLD

and t

DDLT

is the time required by the serializer and deserializer to obtain lock when exiting power-down state with an active PCLK

(2) Specification is ensured by design.

(3) Typical values represent most likely parametric norms at 1.8V or 3.3V, T

A

= +25°C, and at the Recommended Operation Conditions at

the time of product characterization and are not ensured.

(4) UI – Unit Interval is equivalent to one ideal serialized data bit width. The UI scales with PCLK frequency.

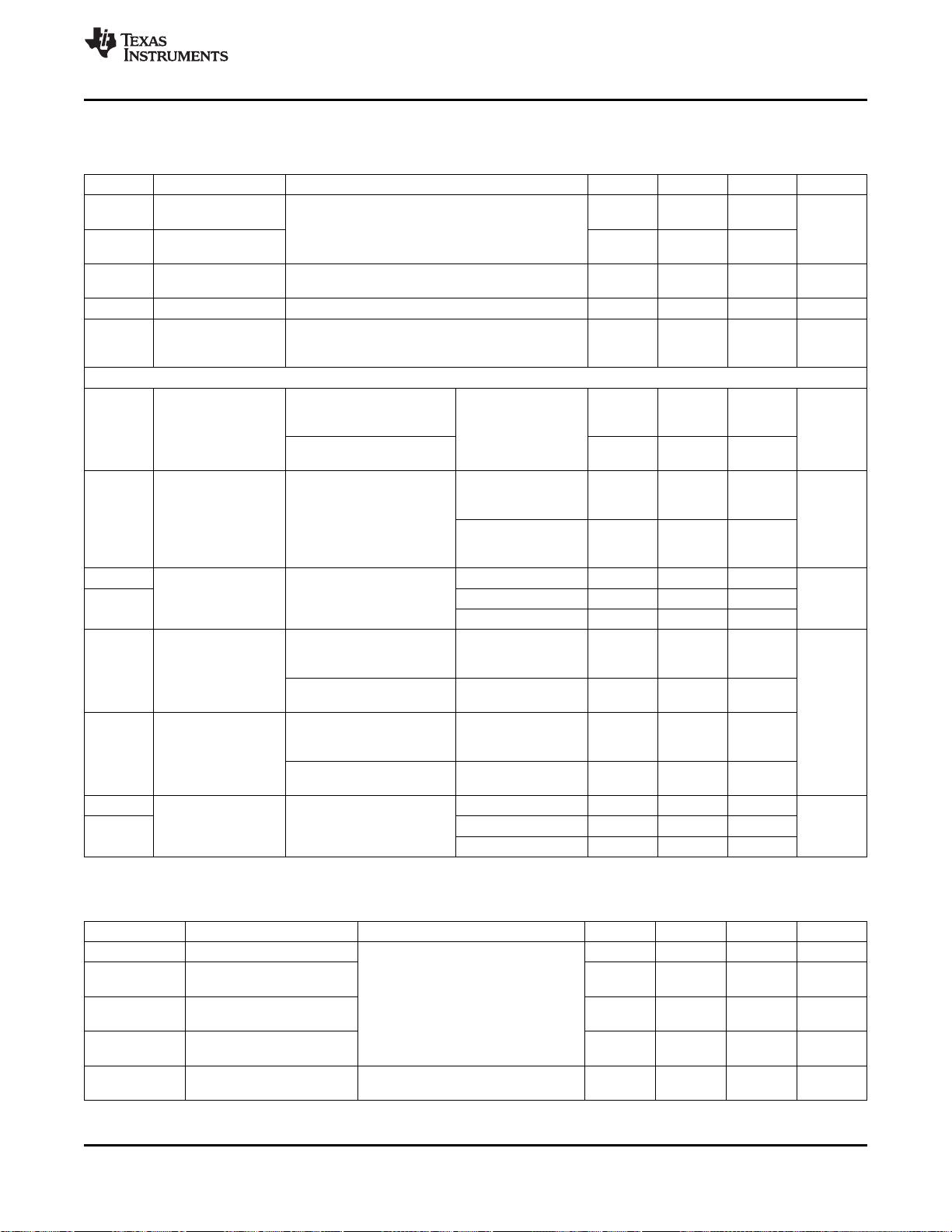

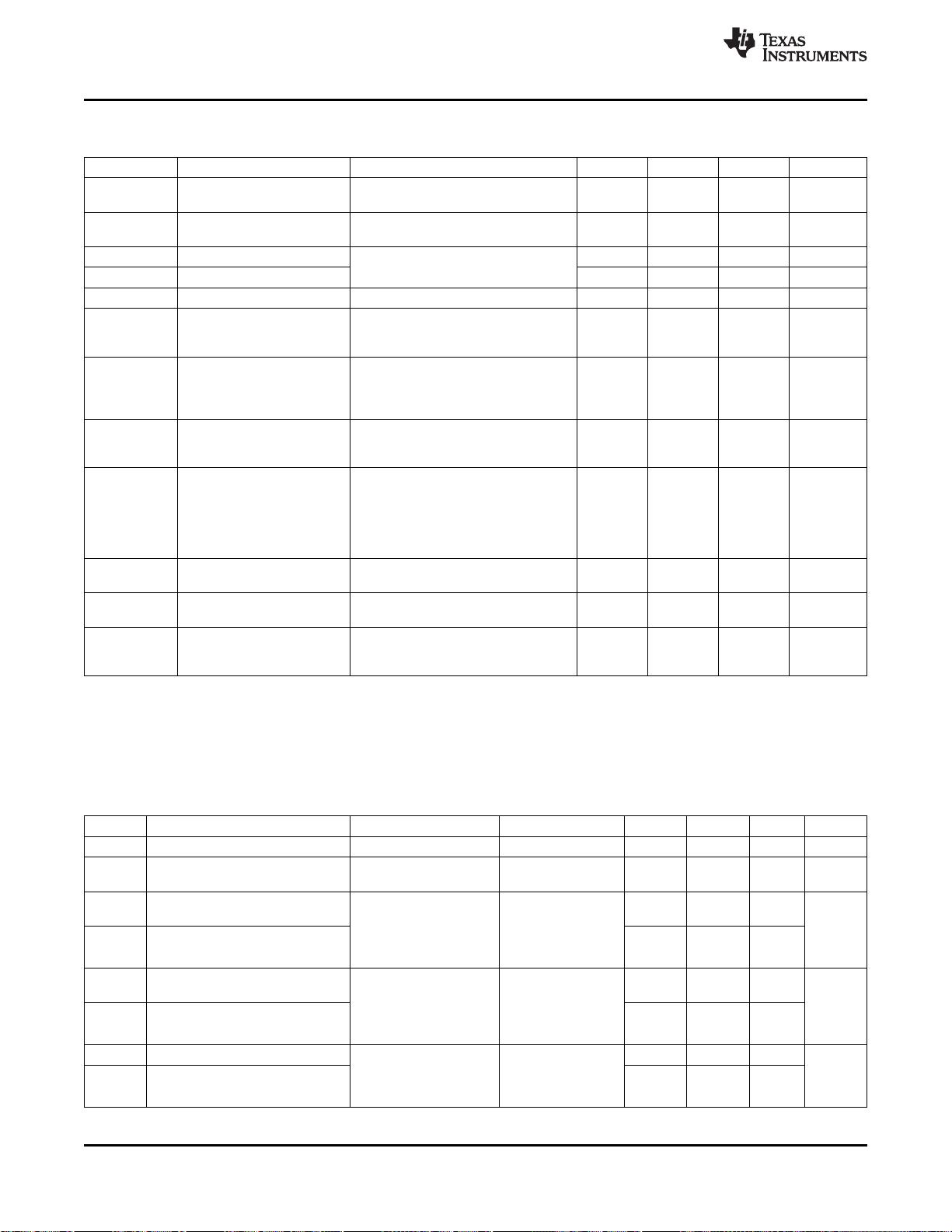

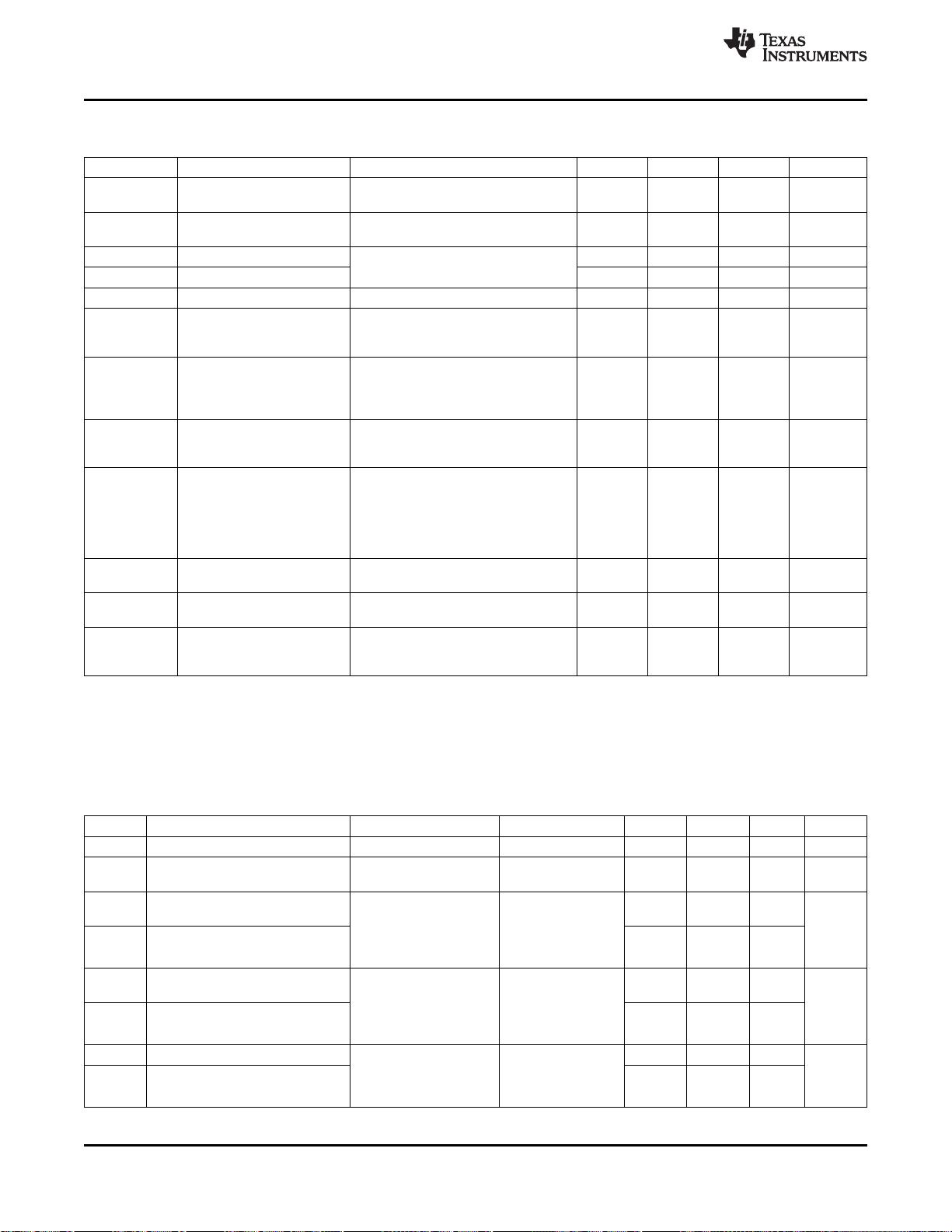

Deserializer Switching Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

Symbol Parameter Conditions Pin/Freq. Min Typ Max Units

t

RCP

Receiver Output Clock Period t

RCP

= t

TCP

PCLK 23.3 T 100 ns

t

PDC

Default Registers

PCLK Duty Cycle PCLK 45 50 55 %

SSCG[3:0] = OFF

LVCMOS Low-to-High Transition V

DDIO

: 1.71V to 1.89V or

t

CLH

1.3 2.0 2.8

Time 3.0 to 3.6V,

C

L

= 8 pF (lumped load) PCLK ns

t

CHL

LVCMOS High-to-Low Transition

Default Registers

1.3 2.0 2.8

Time

(Figure 16)

(1)

LVCMOS Low-to-High Transition V

DDIO

: 1.71V to 1.89V or

t

CLH

1.6 2.4 3.3

Time 3.0 to 3.6V,

Deserializer ROUTn

C

L

= 8 pF (lumped load) ns

t

CHL

Data Outputs

LVCMOS High-to-Low Transition

Default Registers

1.6 2.4 3.3

Time

(Figure 16)

(1)

t

ROS

ROUT Setup Data to PCLK V

DDIO

: 1.71V to 1.89V or 0.38T 0.5T

3.0V to 3.6V, Deserializer ROUTn

t

ROH

ns

C

L

= 8 pF (lumped load) Data Outputs

ROUT Hold Data to PCLK 0.38T 0.5T

Default Registers

(1) Specification is ensured by characterization and is not tested in production.

10 Copyright © 2010–2013, Texas Instruments Incorporated