Data Sheet ADuC7023

Rev. C | Page 19 of 96

OVERVIEW OF THE ARM7TDMI CORE

The ARM7® core is a 32-bit reduced instruction set computer

(RISC). It uses a single 32-bit bus for instruction and data. The

length of the data can be 8 bits, 16 bits, or 32 bits. The length of

the instruction word is 32 bits.

The ARM7TDMI is an ARM7 core with four additional features: T

support for the thumb (16-bit) instruction set, D support for

debug, M support for long multiplications, and I includes the

EmbeddedICE module to support embedded system debugging

THUMB MODE (T)

An ARM instruction is 32 bits long. The ARM7TDMI

processor supports a second instruction set that has been

compressed into 16 bits, called the Thumb® instruction set.

Faster execution from 16-bit memory and greater code density

can usually be achieved by using the Thumb instruction set

instead of the ARM instruction set, which makes the

ARM7TDMI core particularly suitable for embedded

applications.

However, the Thumb mode has two limitations. Thumb code

typically requires more instructions for the same job. As a

result, ARM code is usually best for maximizing the

performance of time critical code. Also, the Thumb instruction

set does not include some of the instructions needed for

exception handling, which automatically switches the core to

ARM code for exception handling.

See the ARM7TDMI user guide for details on the core

architecture, the programming model, and both the ARM

and ARM Thumb instruction sets.

LONG MULTIPLY (M)

The ARM7TDMI instruction set includes four extra instruc-

tions that perform 32-bit by 32-bit multiplication with a 64-bit

result, and 32-bit by 32-bit multiplication-accumulation (MAC)

with a 64-bit result. These results are achieved in fewer cycles

than required on a standard ARM7 core.

EmbeddedICE (I)

EmbeddedICE provides integrated on-chip support for the core.

The EmbeddedICE module contains the breakpoint and watch-

point registers that allow code to be halted for debugging purposes.

These registers are controlled through the JTAG test port.

When a breakpoint or watchpoint is encountered, the processor

halts and enters debug state. Once in a debug state, the

processor registers can be inspected as well as the Flash/EE,

SRAM, and memory mapped registers.

EXCEPTIONS

ARM supports five types of exceptions and a privileged

processing mode for each type. The five types of exceptions are:

• Normal interrupt or IRQ. This is provided to service

general-purpose interrupt handling of internal and

external events.

• Fast interrupt or FIQ. This is provided to service data

transfers or communication channels with low latency. FIQ

has priority over IRQ.

• Memory abort.

• Attempted execution of an undefined instruction.

• Software interrupt instruction (SWI). This can be used to

make a call to an operating system.

Typically, the programmer defines interrupt as IRQ, but for

higher priority interrupt, that is, faster response time, the

programmer can define interrupt as FIQ.

ARM REGISTERS

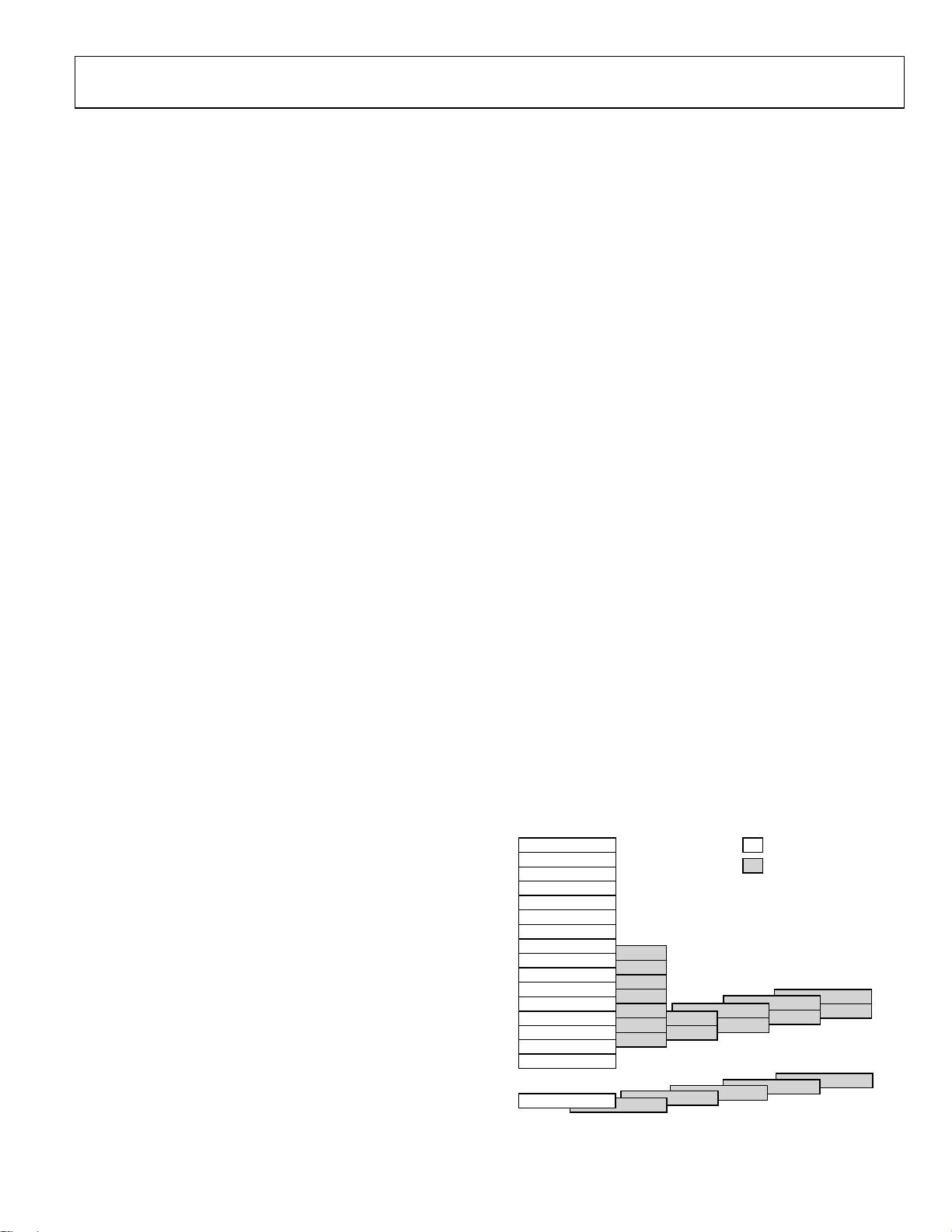

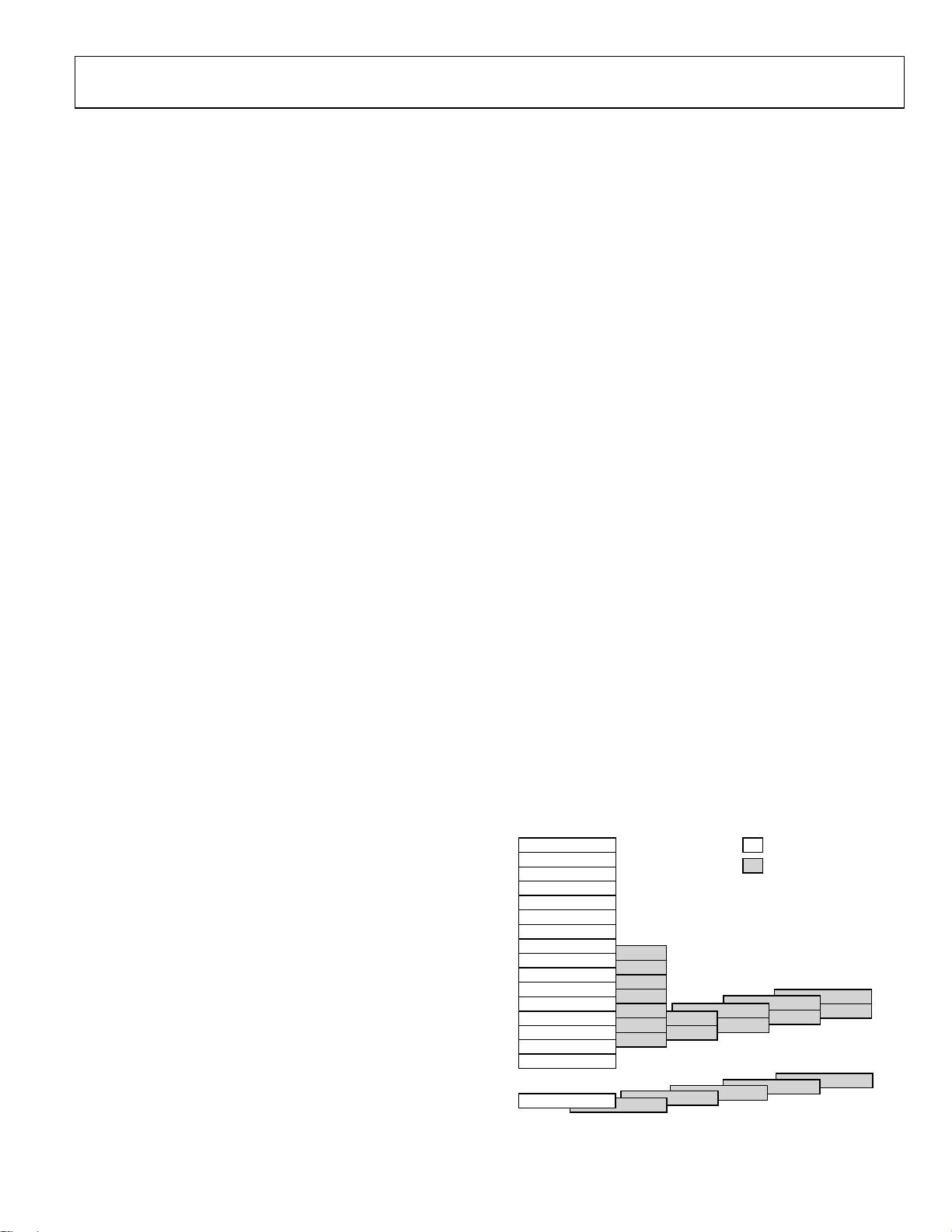

ARM7TDMI has a total of 37 registers: 31 general-purpose

registers and six status registers. Each operating mode has

dedicated banked registers.

When writing user-level programs, 15 general-purpose 32-bit

registers (R0 to R14), the program counter (R15), and the

current program status register (CPSR) are usable. The

remaining registers are only used for system-level programming

and exception handling.

When an exception occurs, some of the standard registers are

replaced with registers specific to the exception mode. All excep-

tion modes have replacement banked registers for the stack

pointer (R13) and the link register (R14) as represented in

Figure 14. The fast interrupt mode has more registers (R8 to R12)

for fast interrupt processing. This means the interrupt processing

can begin without the need to save or restore these registers,

and thus save critical time in the interrupt handling process.

08675-008

USABLE IN USER MODE

SYSTEM MODES ONLY

SPSR_UND

SPSR_IRQ

SPSR_ABT

SPSR_SVC

R8_FIQ

R9_FIQ

R10_FIQ

R11_FIQ

R12_FIQ

R13_FIQ

R14_FIQ

R13_UND

R14_UND

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R14

R15 (PC)

R13_IRQ

R14_IRQ

R13_ABT

R14_ABT

R13_SVC

R14_SVC

SPSR_FIQ

CPSR

USER MODE

FIQ

MODE

SVC

MODE

ABORT

MODE

IRQ

MODE

UNDEFINED

MODE

Figure 14. Register Organization