Cortex-M3处理器技术详解

"Cortex-M3技术参考手册涵盖了微处理器的概述、编程模型、系统控制、存储器映射、异常处理、电源管理和嵌套向量中断控制器(NVIC)以及存储器保护单元(MPU)等内容,适用于STM32F103等基于Cortex-M3的微控制器开发。"

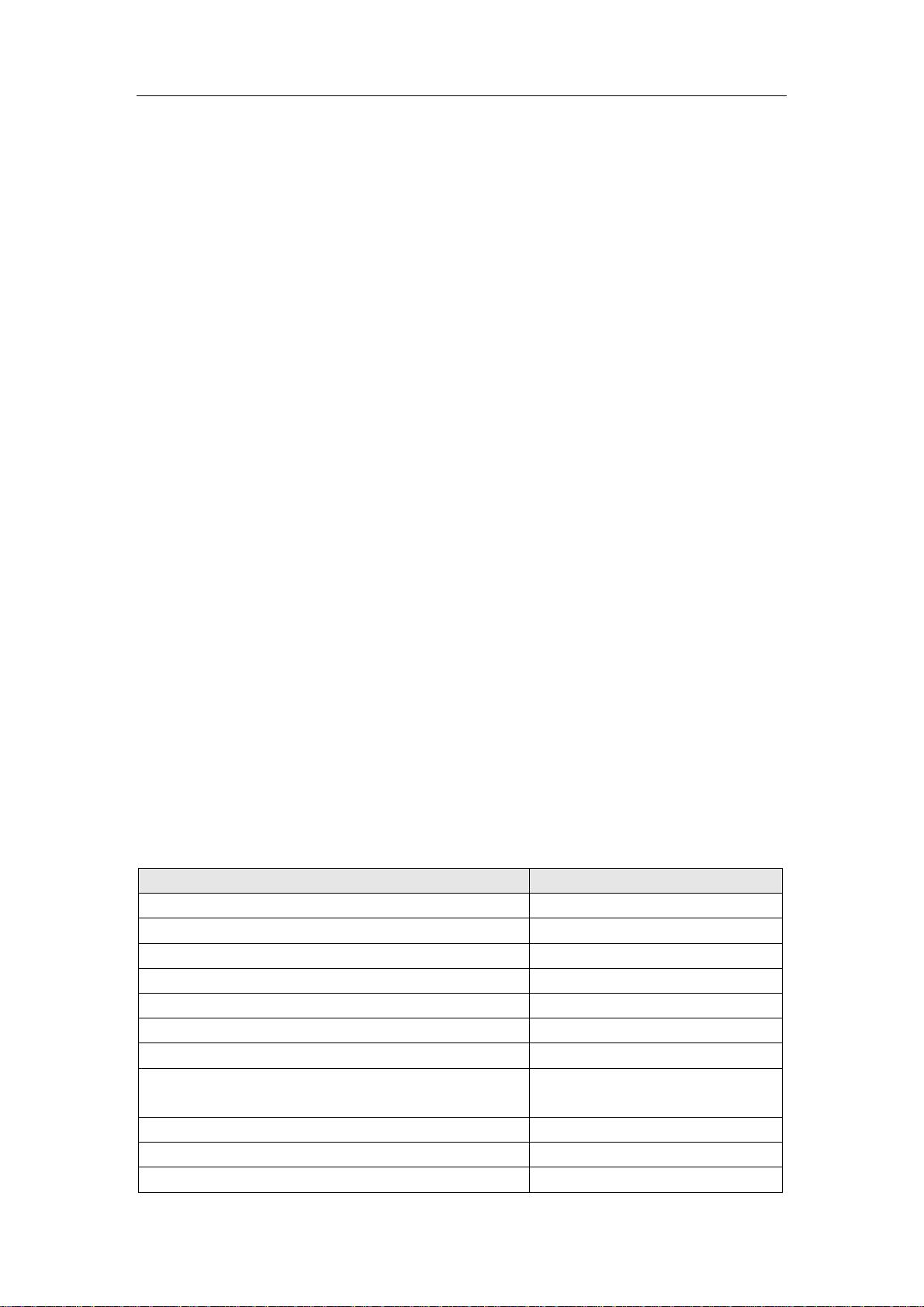

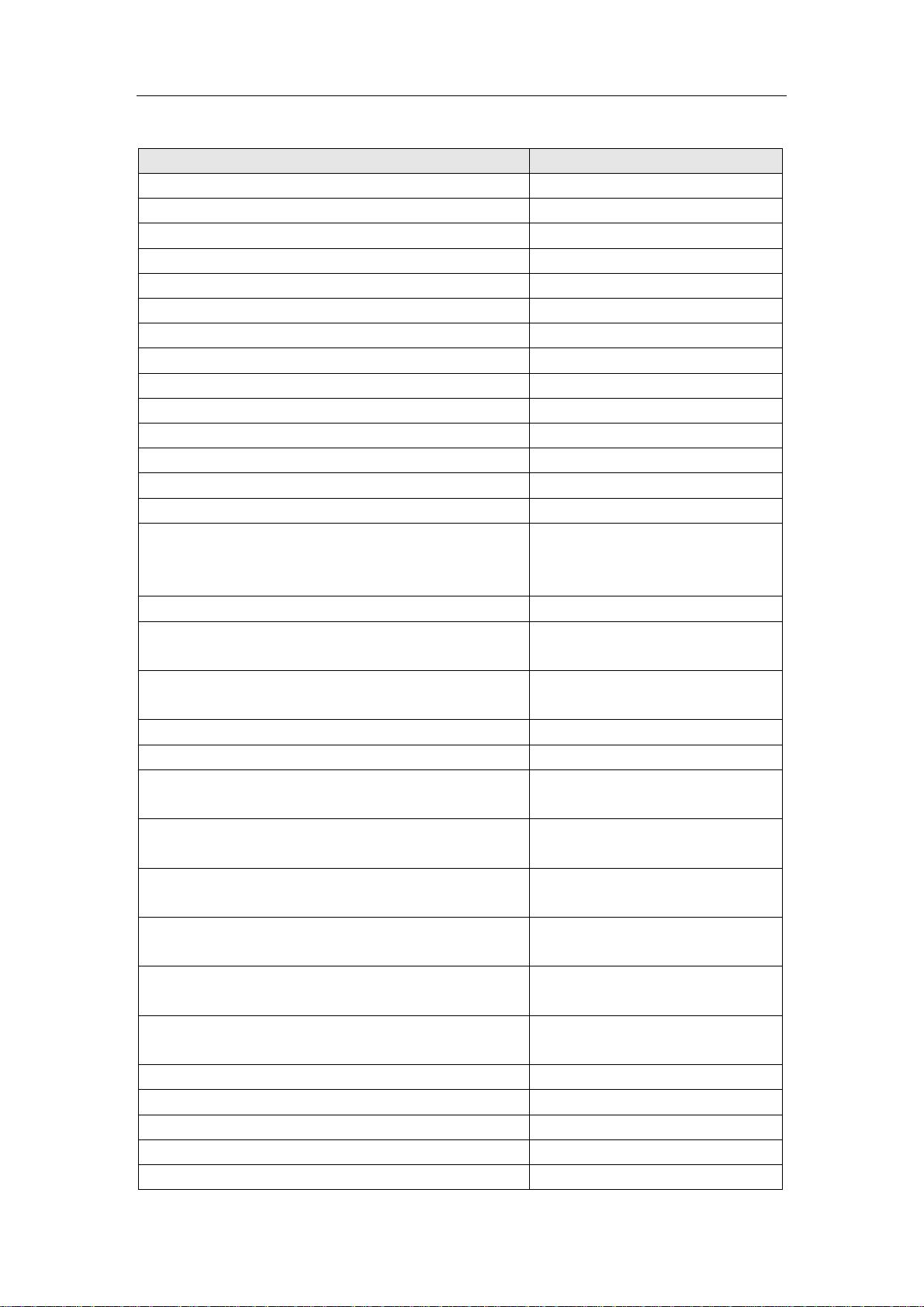

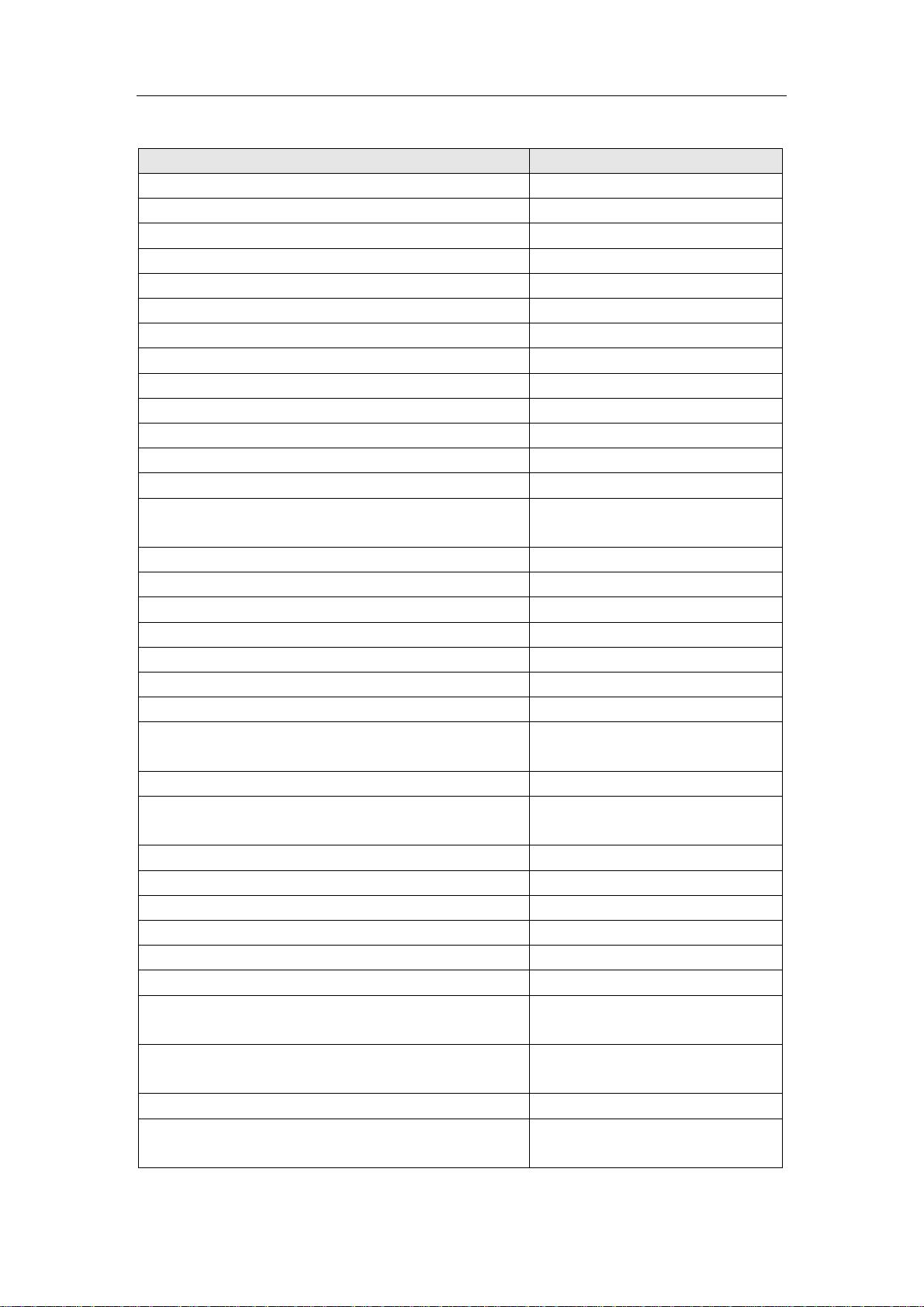

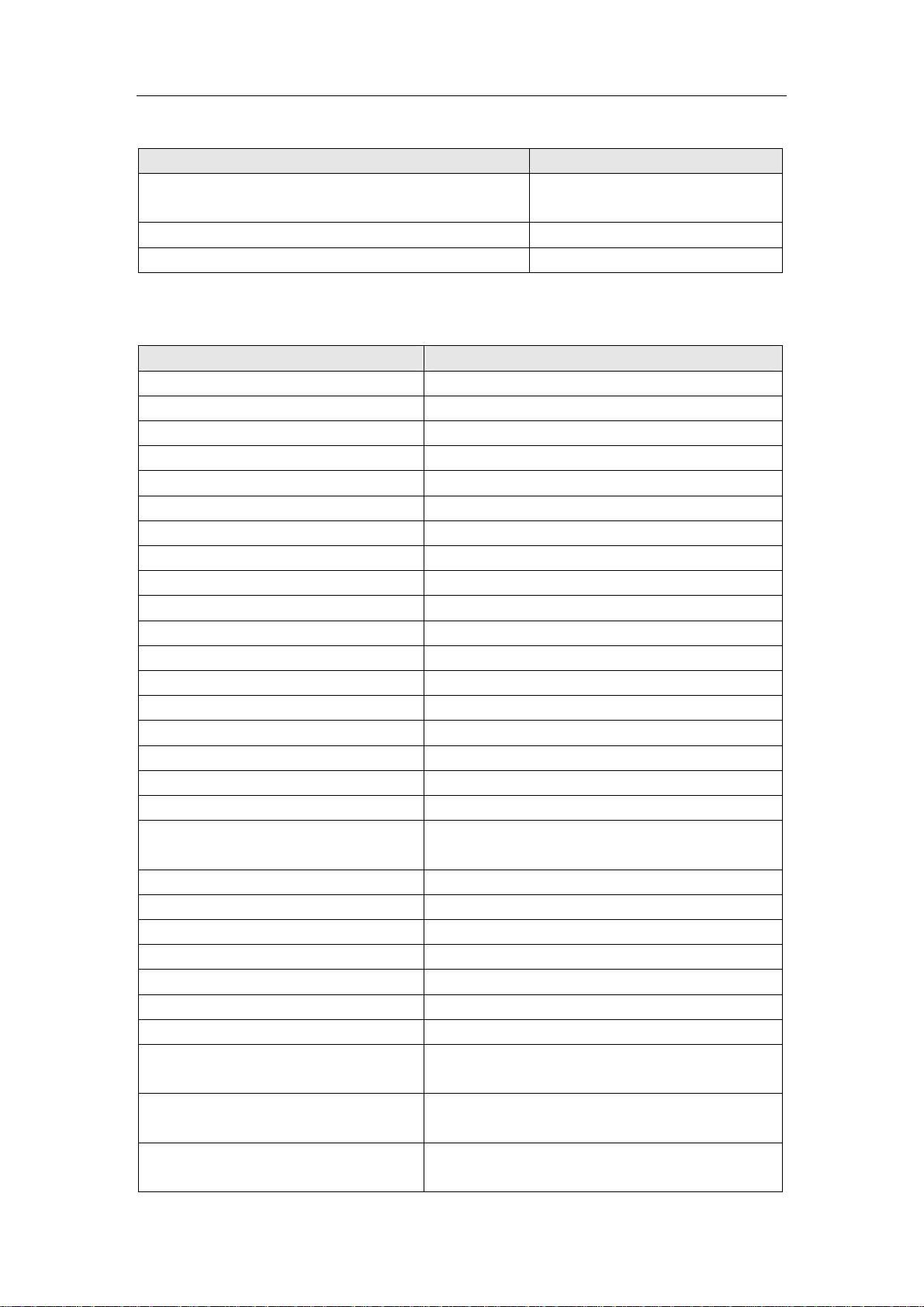

在Cortex-M3处理器中,核心组件包括处理器内核、嵌套向量中断控制器(NVIC)、总线矩阵、快速中断控制器(FPB)、数据watchpoint和trace(DWT)、内置 tracing macrocell(ITM)、内存保护单元(MPU)、嵌入式跟踪宏单元(ETM)、跟踪端口接口单元(TPIU)以及软件/jTAG调试端口(SW/JTAG-DP)。这些组件协同工作,提供了高效能的实时处理能力和丰富的调试功能。

编程模型方面,Cortex-M3有特权和用户两种工作模式,以及运行和睡眠两种工作状态。处理器拥有通用寄存器和特殊用途的程序状态寄存器(如xPSR),并支持多种数据类型。存储器格式和指令集设计适应了高效的嵌入式编程需求。

系统控制涉及众多处理器寄存器,包括NVIC、调试接口寄存器、MPU和跟踪单元的寄存器,这些寄存器用于系统配置、中断处理、调试和内存保护。

存储器映射是Cortex-M3处理内存访问的关键,其中bit-band技术允许对单个比特进行操作。ROM存储器表则包含了固件信息。

异常模型定义了处理器如何响应中断和异常事件,包括不同类型的异常、优先级管理、特权级别、堆栈处理以及异常的进入和退出流程。

电源管理方面,Cortex-M3支持睡眠和深度睡眠模式,以优化能效。

NVIC作为Cortex-M3中断管理的核心,提供非屏蔽中断和脉冲中断处理,并且具有灵活的优先级设置。

MPU提供了内存区域的保护,允许设定访问权限,确保代码和数据的安全性。

Cortex-M3技术参考手册是开发者理解和利用Cortex-M3微控制器进行系统设计和编程的重要参考资料。

相关推荐

wjm2005427

- 粉丝: 1

- 资源: 1

最新资源

- StateEstimationforRobotics-CN.pdf.tar.gz

- Desktop,c语言火车票订票管理源码,c语言

- node-font-list:获取系统中安装的字体列表

- 菲尼克斯微型继电器手册.rar

- MICROMAKEL3+ 3ds chitubox插件

- Honeywell_hackathon

- developer-knowledge:独立的增强型知识项目分层清单,可以成为更好的软件开发人员。 标题

- h2gis,H2数据库的空间扩展。.zip

- NewtonJson.rar

- shell:一种用于IBM Cloud Functions and Composer的基于电子的开发工具

- 20210315-中国联通-通信行业:5G终端白皮书V4(2021年度).rar

- 单片机频率计仿真protues

- 情人节图标 .svg素材下载

- Android_Projects:我尝试学习Android开发时所做的旧项目

- 主题默认值:Hexsoftstudio CSS默认值

- Gestrue,安卓、安卓、安卓.zip