Vivado FPGA设计实战指南:从创建项目到生成比特流

下载需积分: 13 | DOC格式 | 736KB |

更新于2024-07-20

| 102 浏览量 | 举报

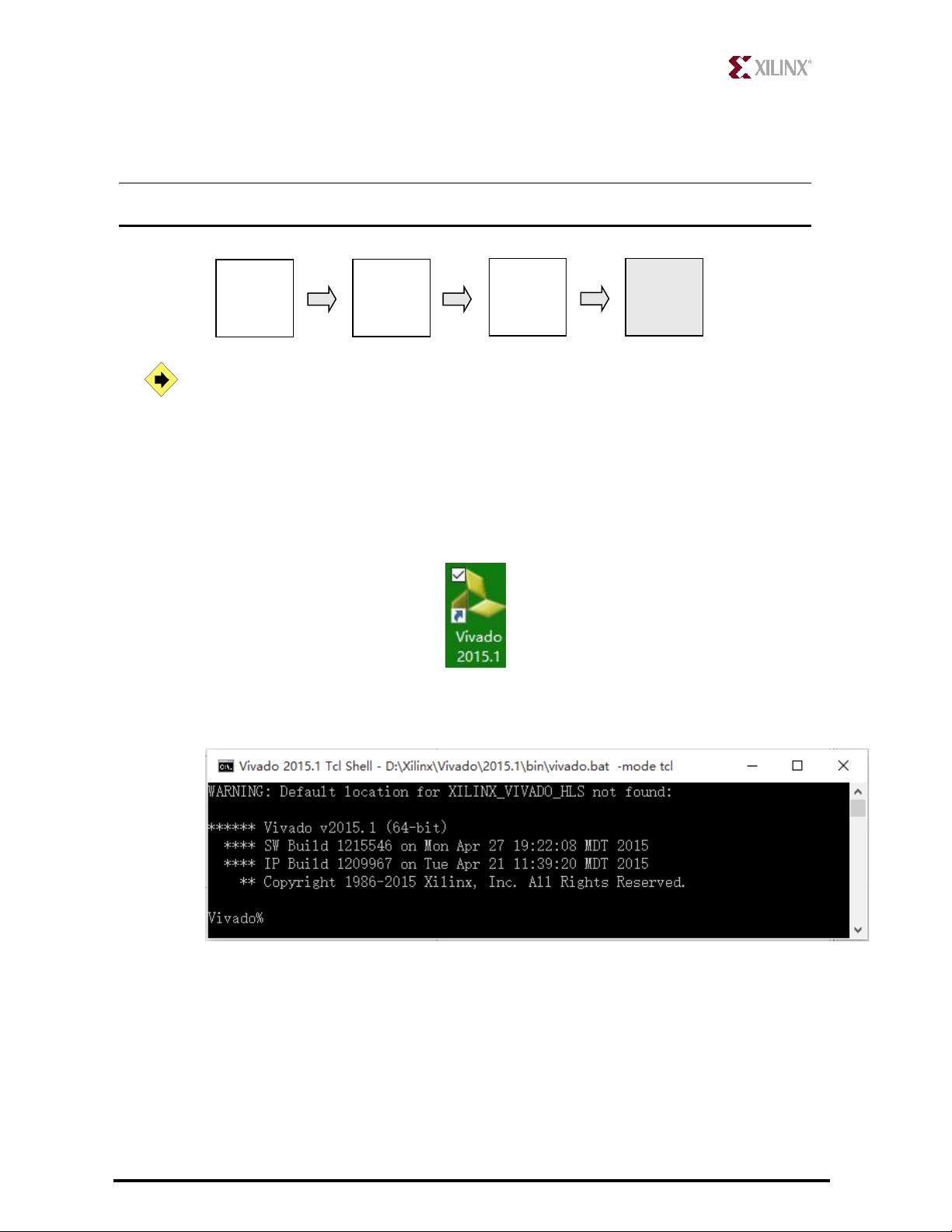

"Vivado设计流程指导手册详细介绍了如何使用Vivado开发FPGA项目,特别是针对Zynq™-7000All Programmable SoC Starter Kit的实践操作。教程涵盖从创建Verilog HDL模型到硬件验证的完整流程,涉及创建项目、设置约束、仿真、综合、实现及生成比特流等多个环节。"

在Vivado FPGA设计流程中,首先,你需要创建一个项目(1)。这通常包括选择目标器件,例如Artix-100,以及设定项目的基本属性。接着,你会导入自己编写的或已有的Verilog HDL模型(2),这是描述数字电路逻辑的基础。

创建用户约束文件(3)是流程中的关键步骤。约束文件(XDC)用于指定硬件接口的具体要求,如引脚分配、时序约束等。在本教程中,你会学习如何利用部分提供的XDC文件并添加额外的约束。

行为仿真(4)允许你在实际硬件实现前检查设计的逻辑行为。Vivado的XSIM工具提供了一个平台,可以运行测试激励并查看响应,以确保逻辑设计符合预期。

接下来,设计的综合(5)阶段将HDL代码转换成逻辑门级表示,优化设计以适应目标FPGA的结构。这一过程会考虑时序、面积和功耗等因素。

实现设计(6)阶段则将综合后的逻辑映射到FPGA的具体物理资源上,包括布线和资源分配。这一步完成后,设计的硬件描述已经转换成了适合加载到FPGA的配置数据。

生成比特流文件(7)是整个流程的高潮,它是一个二进制文件,包含了配置FPGA所需的所有信息。一旦比特流生成,就可以下载到硬件中。

最后,验证(8)是通过下载比特流到Nexys4 board上,观察FPGA的实际工作情况,确认设计的功能正确性。此外,教程还强调了使用Tcl脚本自动化设计流程的可能性,以提高效率。

在实验的每个步骤中,都会有详细的说明和图示指导,帮助初学者逐步熟悉Vivado工具和FPGA设计的基本概念。通过此教程,你将能够掌握从概念到硬件实现的关键技能,包括HDL编程、约束设置、仿真验证以及硬件配置。

相关推荐

qq_29292673

- 粉丝: 0

最新资源

- DOS与Windows文件管理:FAT16与FAT32对比分析

- 计算机网络操作系统:作业管理与用户界面

- 计算机操作系统简介:操作系统的历史与功能

- 操作系统概述:计算机网络下的系统软件详解

- Windows Communication Foundation (WCF) 深入解析

- Java网络编程入门:简单快速实现常见任务

- 精通Java网络编程:解锁简单高效的网络应用开发

- 操作系统原理详解:模块、功能与发展历程

- Java入门基础教程:环境配置与 HelloWorld 示例

- 操作系统调度算法详解:内存管理与模拟实践

- M41T0时钟芯片驱动的可校时数字钟设计与实现

- Java设计模式解析与实战

- Java设计模式解析与实战

- 深入理解MFC:窗口创建与消息处理

- 清华版《Java2实用教程》源代码解析

- Java Servlet API 2.1a中文翻译与应用指南