FPGA实现的圆阵数字自适应波束形成系统:高效与简易架构

79 浏览量

更新于2024-08-28

收藏 320KB PDF 举报

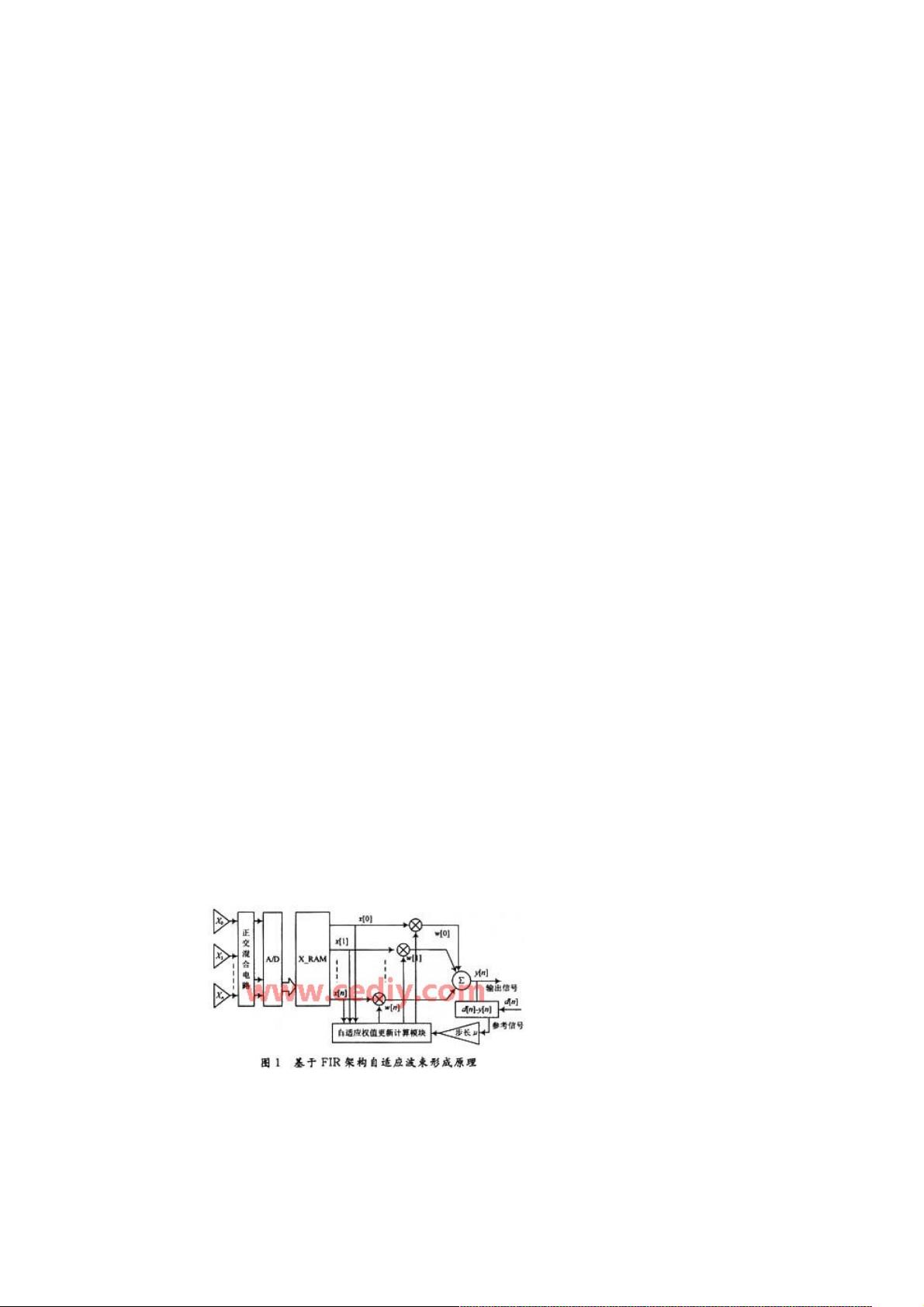

本文主要探讨了一种专为FPGA优化的圆阵数字自适应波束形成系统的设计与实现。该系统的核心在于结合了快速傅立叶变换(FIR)滤波器结构和延迟最小均方(DLMS)算法,旨在提升计算速度并节省硬件资源。关键设计亮点是采用了循环移位乘加器(Cycle-Displacement Pipelined MAC,简称CDP-MAC)来构建复数乘加模块,这种算法通过数据流水线技术有效地实现了多运算的并行处理,提高了系统的实时性能。

系统中的自适应部分采用了并行乘法器,用于实时更新权值,确保了波束形成过程中的动态适应能力。这在实时性要求极高的应用中,如雷达、声纳探测和超声成像等领域,显得尤为重要,能够快速响应目标的变化,提升信号处理的实时跟踪和测量精度。

开发过程中,文章强调了利用FPGA作为硬件平台的优势,FPGA因其灵活性和高集成度,使得整个数字自适应波束形成系统结构更加紧凑,且易于实现和调试。与传统的DSP软件编程和CPLD控制逻辑相比,这种方法简化了设计流程,降低了硬件成本,并且提高了系统整体的性能。

通过详细的仿真验证,基于FPGA的数字自适应波束形成系统(DABF)证实了其在时间效率方面的优越性,以及在复杂任务下的高效执行能力。关键词包括数字自适应波束形成、延迟最小均方算法、流水乘加器和FIR滤波器,这些都是构建此系统的关键技术。

这篇文章为高性能实时信号处理系统提供了一种有效的硬件解决方案,对于电子工程师和系统设计师来说,具有重要的参考价值,特别是在追求高效率和低成本的现代电子设备中。

135 浏览量

216 浏览量

189 浏览量

135 浏览量

点击了解资源详情

256 浏览量

121 浏览量

2022-07-15 上传

weixin_38729399

- 粉丝: 7

最新资源

- 武汉大学数字图像处理课程课件精要

- 搭建个性化知识付费平台——Laravel开发MeEdu教程

- SSD7练习7完整解答指南

- Android中文API合集第三版:开发者必备指南

- Python测试自动化实践:深入理解更多测试案例

- 中国风室内装饰网站模板设计发布

- Android情景模式中音量定时控制与铃声设置技巧

- 温度城市的TypeScript实践应用

- 新版高通QPST刷机工具下载支持高通CPU

- C++实现24点问题求解的源代码

- 核电厂水处理系统的自动化控制解决方案

- 自定义进度条组件AMProgressView用于统计与下载进度展示

- 中国古典红木家具网页模板免费下载

- CSS定位技术之Position-master解析

- 复选框状态持久化及其日期同步技术

- Winform版HTML编辑器:强大功能与广泛适用性