AXI桥接PCIe Gen3子系统v3.0设计指南

需积分: 0 93 浏览量

更新于2024-06-18

收藏 3.26MB PDF 举报

AXI Bridge for PCI Express Gen3 Subsystem v3.0 是一款专为高性能计算和数据传输设计的IP核心,旨在连接Advanced eXtensible Interface (AXI)总线与下一代PCI Express (PCIe) Gen3标准,以实现系统内部的高速通信。这款产品是基于Vivado Design Suite的PG194版本,发布于2023年11月24日,由AMD Adaptive Computing开发,致力于创造一个包容性的工作环境。

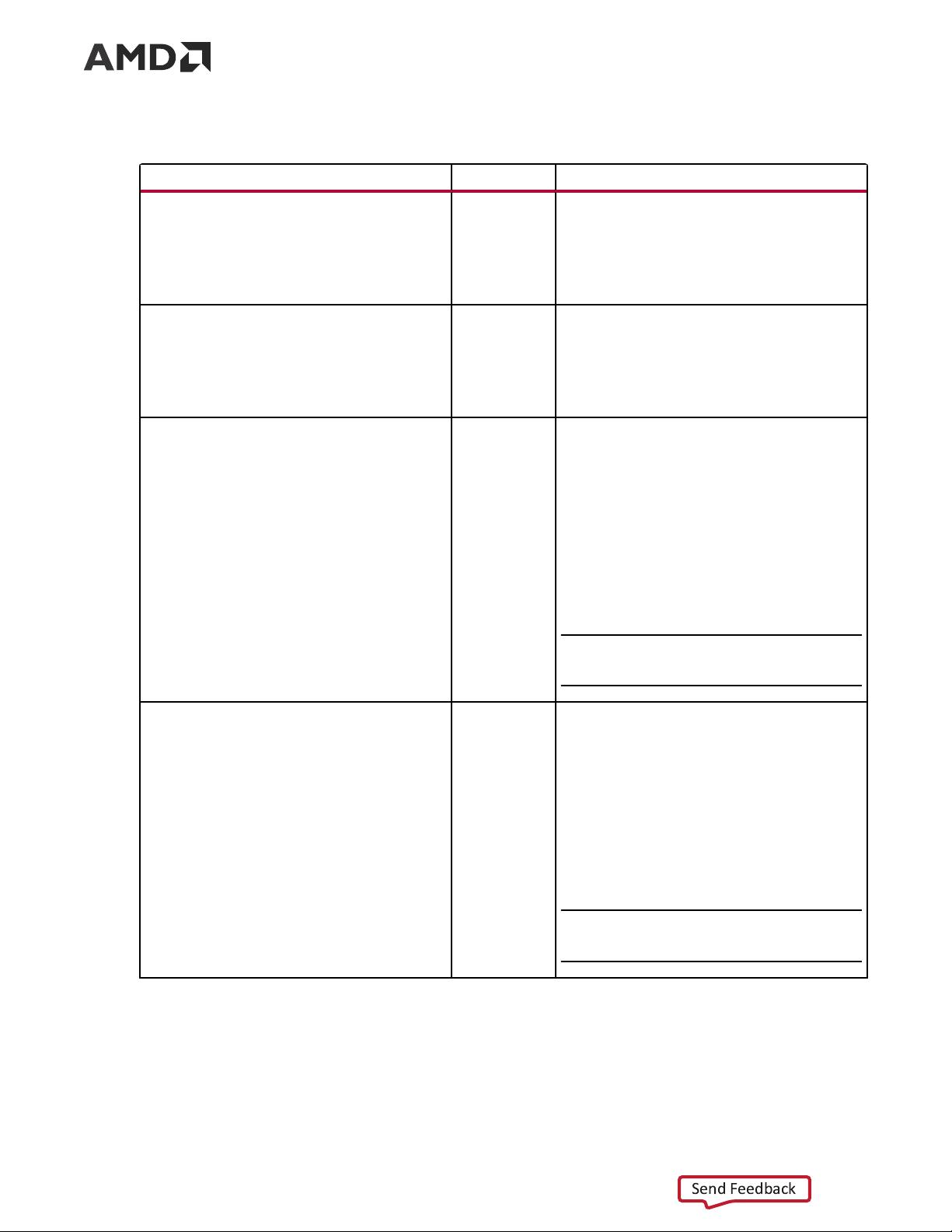

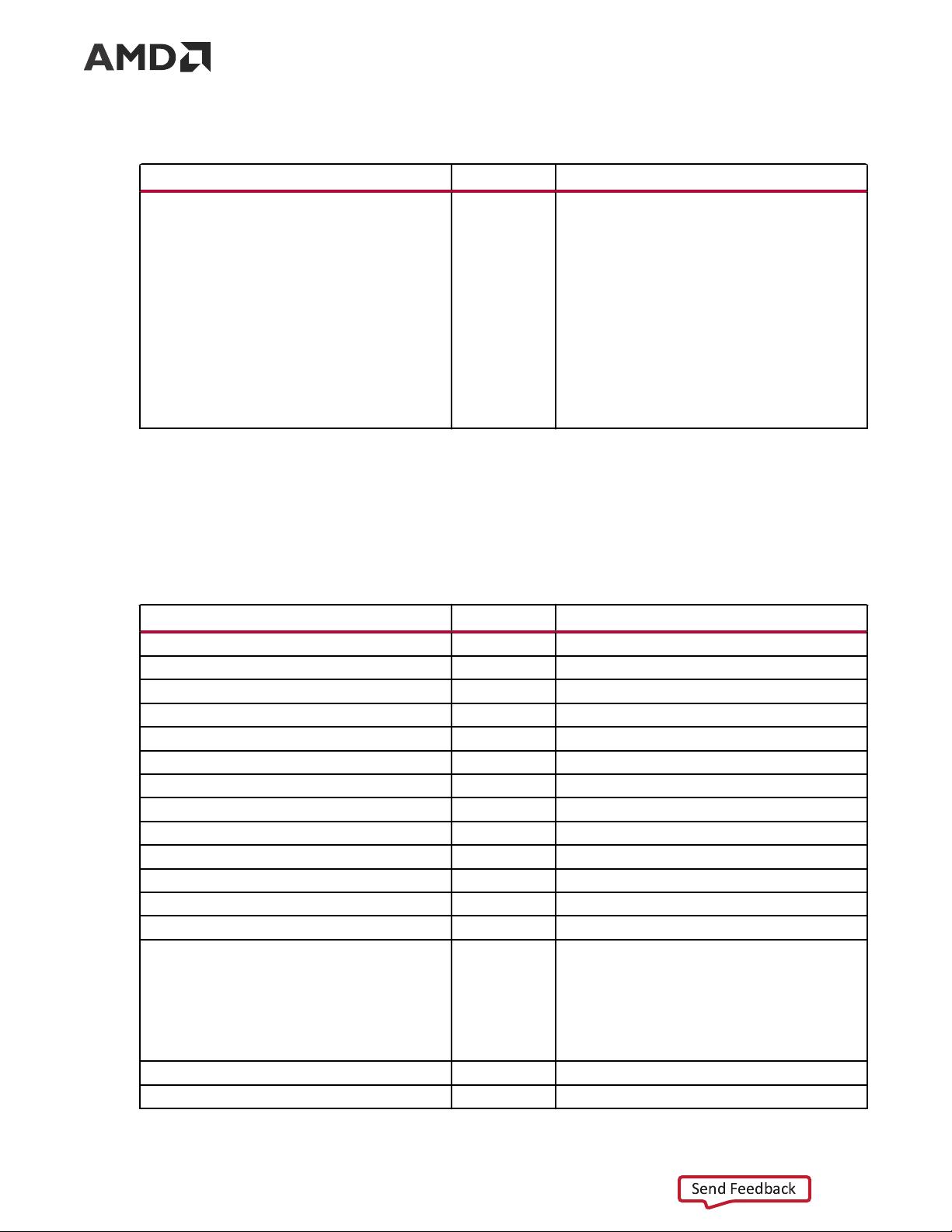

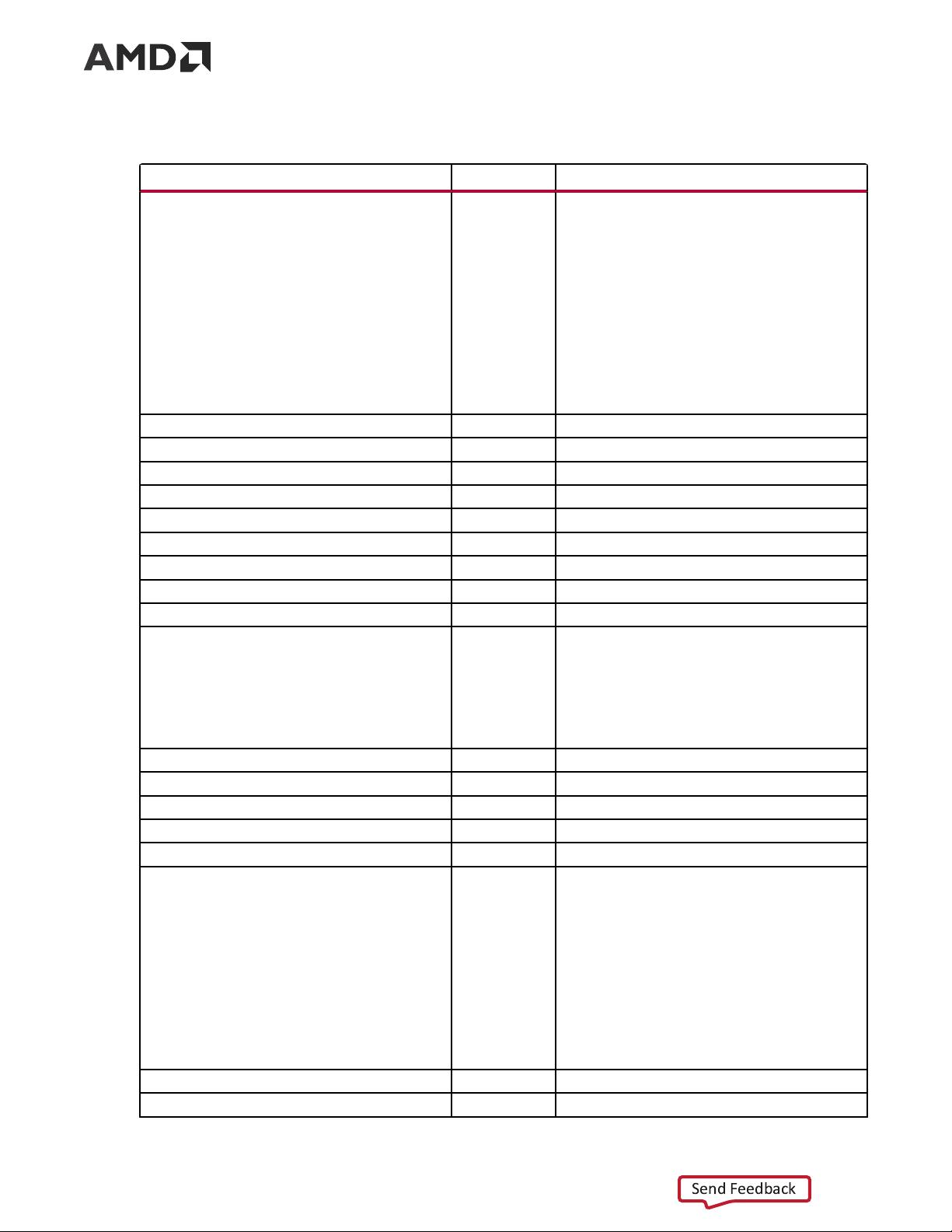

该产品的特点包括支持PCIe Gen3的多种交易类型和功能,如差分信号、错误校验机制以及高级配置/状态交换(CAS)。然而,需要注意的是,它可能存在一些不支持的功能和局限性,比如特定的PCIe能力可能在某些配置下不可用。此外,设计时要考虑PCIe交易类型的兼容性和PCIe规范的要求,例如数据速率、带宽和时序约束。

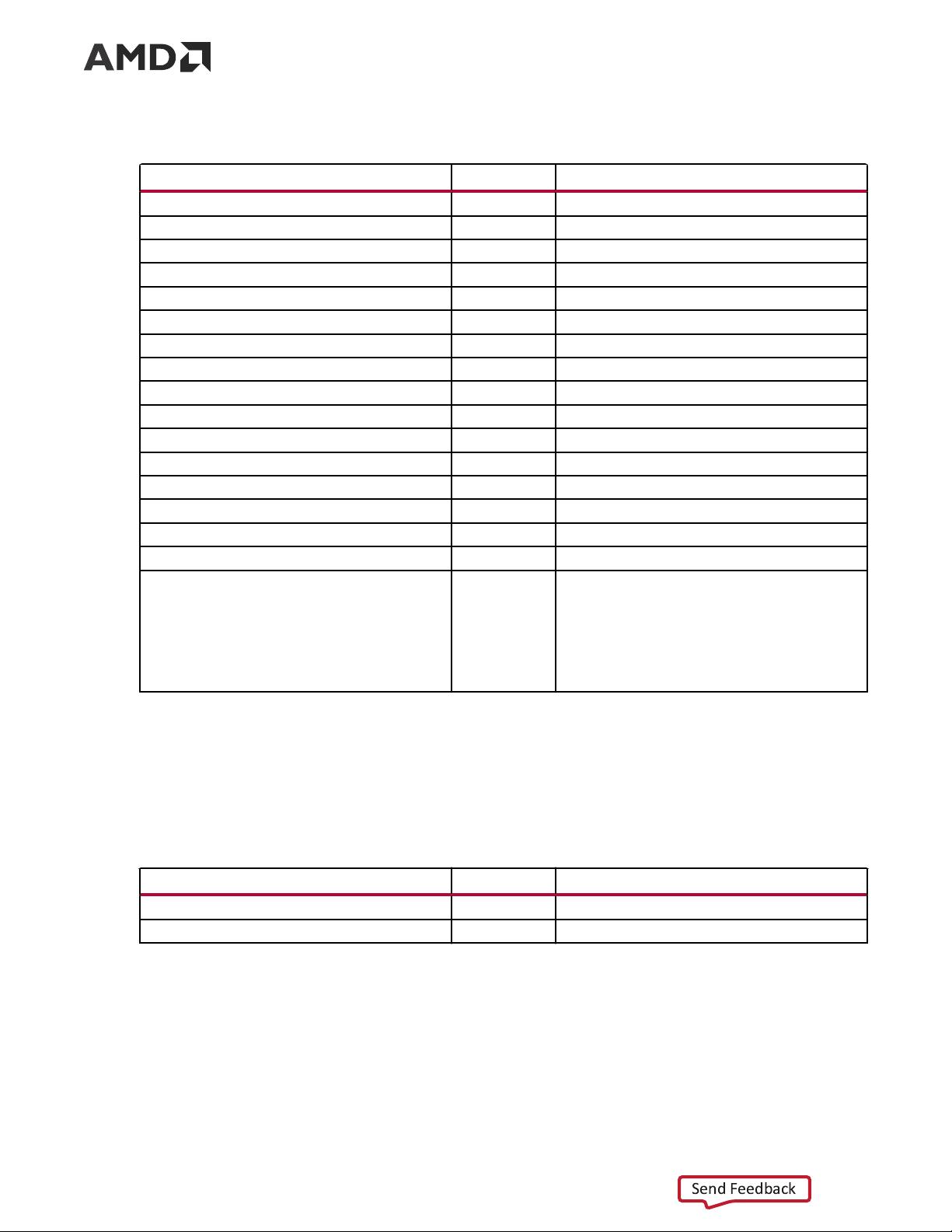

对于接口规范,该桥接器符合相关PCIe标准,确保了系统的兼容性和互操作性。性能和资源利用方面,产品强调了高效的数据传输速率和对设计者硬件资源的优化管理。对于最小设备要求,用户需要确保其系统具备足够的AXI控制器和PCIe端口来充分利用这款IP。

产品规格部分详细列出了接口描述、桥接参数以及内存映射,设计者在集成时需要遵循这些指南。设计流程涉及选择合适的桥接配置,理解不同端口的功能划分,并根据实际应用调整参数以满足性能需求。

此外,AMD已启动内部项目,以消除产品和相关文档中的非包容性语言,这反映了公司对于创建无偏见环境的决心。尽管早期产品可能仍存在此类问题,但AMD正在积极更新以适应不断发展的行业标准。用户在参考文档时,应关注任何关于语言和术语变化的后续通知。

AXI Bridge for PCI Express Gen3 Subsystem v3.0是一个关键的工具,帮助设计师构建高效、兼容的系统架构,同时需关注其最新的产品更新和语言政策,以确保设计的现代性和可接受性。

2009-09-25 上传

2021-10-03 上传

2024-08-14 上传

2021-09-03 上传

2023-11-24 上传

2024-05-27 上传

2023-06-25 上传

麦克四伟

- 粉丝: 107

- 资源: 3

最新资源

- 高清艺术文字图标资源,PNG和ICO格式免费下载

- mui框架HTML5应用界面组件使用示例教程

- Vue.js开发利器:chrome-vue-devtools插件解析

- 掌握ElectronBrowserJS:打造跨平台电子应用

- 前端导师教程:构建与部署社交证明页面

- Java多线程与线程安全在断点续传中的实现

- 免Root一键卸载安卓预装应用教程

- 易语言实现高级表格滚动条完美控制技巧

- 超声波测距尺的源码实现

- 数据可视化与交互:构建易用的数据界面

- 实现Discourse外聘回复自动标记的简易插件

- 链表的头插法与尾插法实现及长度计算

- Playwright与Typescript及Mocha集成:自动化UI测试实践指南

- 128x128像素线性工具图标下载集合

- 易语言安装包程序增强版:智能导入与重复库过滤

- 利用AJAX与Spotify API在Google地图中探索世界音乐排行榜