ESP32-C3技术参考手册:CPU, DMA, 存储器详解

需积分: 0 40 浏览量

更新于2024-07-06

4

收藏 6.63MB PDF 举报

"ESP32-C3技术参考手册(中文).pdf"

ESP32-C3是乐鑫信息科技推出的一款物联网微控制器,该芯片基于RISC-V架构,具有丰富的功能和高集成度。本手册详细介绍了ESP32-C3的各项特性和使用方法。

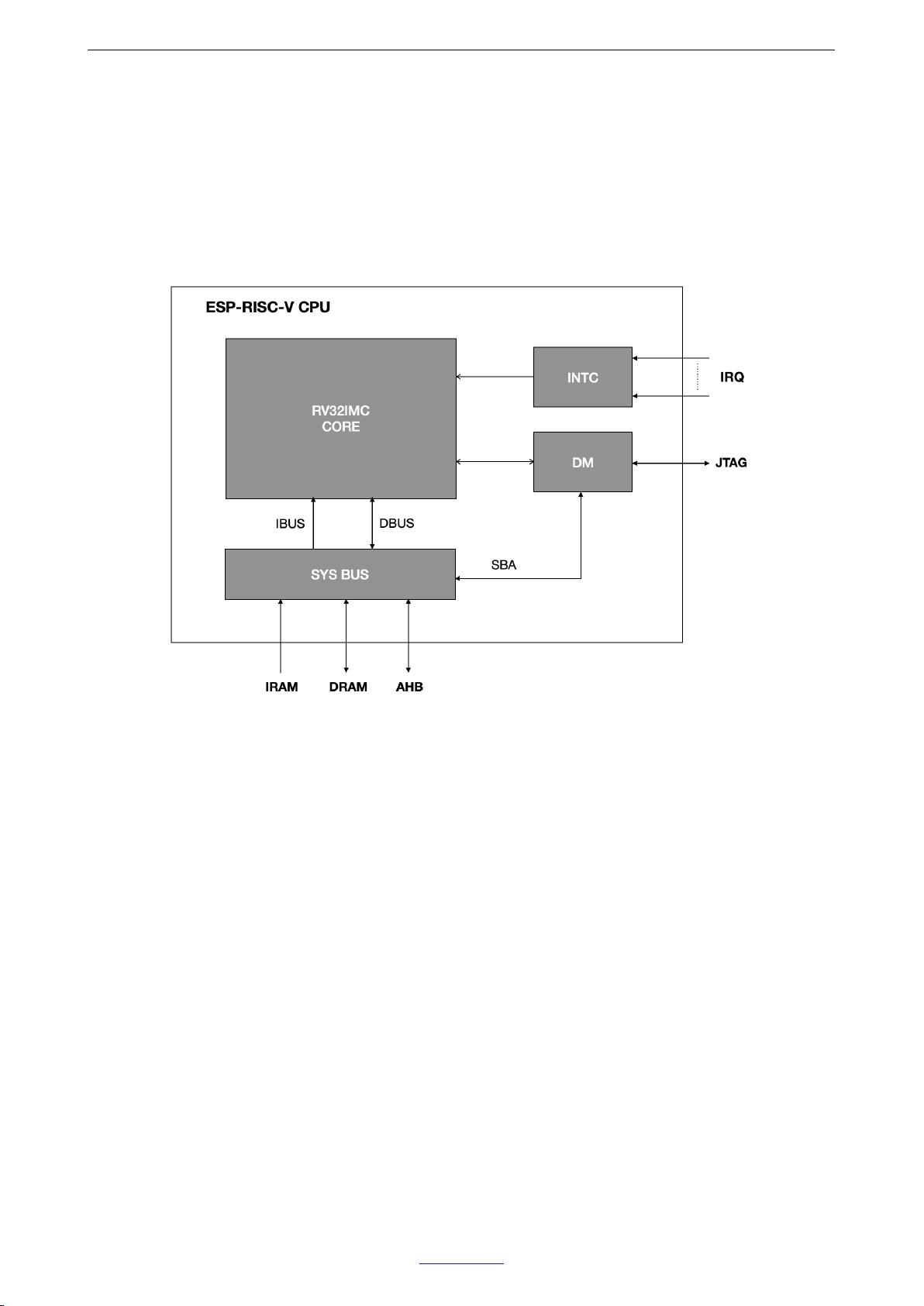

1. ESP-RISC-V CPU

- 概述:ESP32-C3采用的是RISC-V 32位单核CPU,这是一种开放源码指令集架构,设计简洁、高效。

- 特性:CPU支持无序执行、分支预测、硬件乘法和除法等功能,适合低功耗应用。

- 地址分布:CPU地址空间包括不同的内存区域,如代码、数据、堆栈等。

- 配置与状态寄存器(CSR):这些寄存器用于控制和查询CPU状态,包括中断、调试和性能监控等功能。

1. 中断控制器

- 特性:中断控制器支持多种中断源,提供灵活的中断处理机制。

- 功能描述:它可以管理和触发中断,处理来自不同硬件模块的请求。

- 建议操作:配置中断时需注意延迟和配置流程,确保中断及时准确地响应。

1. 调试

- 概述:芯片内置调试支持,便于开发和故障排查。

- 功能描述:提供了硬件断点、单步执行、数据观察点等功能,便于在开发过程中调试程序。

1. 硬件触发器

- 特性:硬件触发器可以自动执行特定操作,如定时启动任务。

- 功能描述:通过设置触发条件,可以在满足条件时启动预定义的操作序列。

1. 存储器保护

- 概述:提供内存保护机制,防止非法访问或错误操作导致系统崩溃。

- 功能描述:可以设置权限和访问控制,确保数据安全。

2. 通用DMA控制器(GDMA)

- 概述:GDMA能实现高速数据传输,减轻CPU负担。

- 特性:支持多种传输模式,如外设到存储、存储到外设以及存储到存储。

- 功能描述:GDMA通过链表管理传输任务,支持中断和仲裁机制,可动态调整带宽。

3. 系统和存储器

- 概述:系统包括内部和外部存储器,以及地址映射机制。

- 主要特性:内置存储器如SRAM,支持扩展外部存储如SPI Flash或SD卡。

- 功能描述:地址映射允许不同类型的内存被CPU正确寻址,内部存储器提供快速访问,外部存储器扩展存储容量。

该手册还包含更多关于GPIO、无线连接、电源管理、模拟信号接口等其他模块的详细信息,是开发ESP32-C3相关项目的重要参考资料。开发者可以通过查阅手册中的寄存器列表和详细描述,了解如何配置和控制芯片的各个部分,以实现所需的功能。

2018-01-28 上传

2024-01-23 上传

2024-09-08 上传

171 浏览量

2022-03-15 上传

2021-08-09 上传

2021-08-09 上传

2023-06-27 上传

崔家寨大当家

- 粉丝: 49

- 资源: 37

最新资源

- MATLAB新功能:Multi-frame ViewRGB制作彩色图阴影

- XKCD Substitutions 3-crx插件:创新的网页文字替换工具

- Python实现8位等离子效果开源项目plasma.py解读

- 维护商店移动应用:基于PhoneGap的移动API应用

- Laravel-Admin的Redis Manager扩展使用教程

- Jekyll代理主题使用指南及文件结构解析

- cPanel中PHP多版本插件的安装与配置指南

- 深入探讨React和Typescript在Alias kopio游戏中的应用

- node.js OSC服务器实现:Gibber消息转换技术解析

- 体验最新升级版的mdbootstrap pro 6.1.0组件库

- 超市盘点过机系统实现与delphi应用

- Boogle: 探索 Python 编程的 Boggle 仿制品

- C++实现的Physics2D简易2D物理模拟

- 傅里叶级数在分数阶微分积分计算中的应用与实现

- Windows Phone与PhoneGap应用隔离存储文件访问方法

- iso8601-interval-recurrence:掌握ISO8601日期范围与重复间隔检查