FPGA深度解析:组成、原理及开发流程

116 浏览量

更新于2024-08-31

收藏 398KB PDF 举报

"集成电路中的FPGA组成、工作原理和开发流程"

在集成电路中,FPGA(Field Programmable Gate Array,现场可编程门阵列)是一种重要的可编程器件,它结合了可编程逻辑阵列和可编程互连网络,使得设计者能够根据需求自由配置电路结构。FPGA的发展源自早期的PAL、GAL和EPLD器件,它在专用集成电路(ASIC)领域中扮演着半定制电路的角色,解决了传统定制电路灵活性低且成本高昂的问题,同时也弥补了可编程器件逻辑门数量有限的不足。

FPGA的结构主要包括三个关键部分:

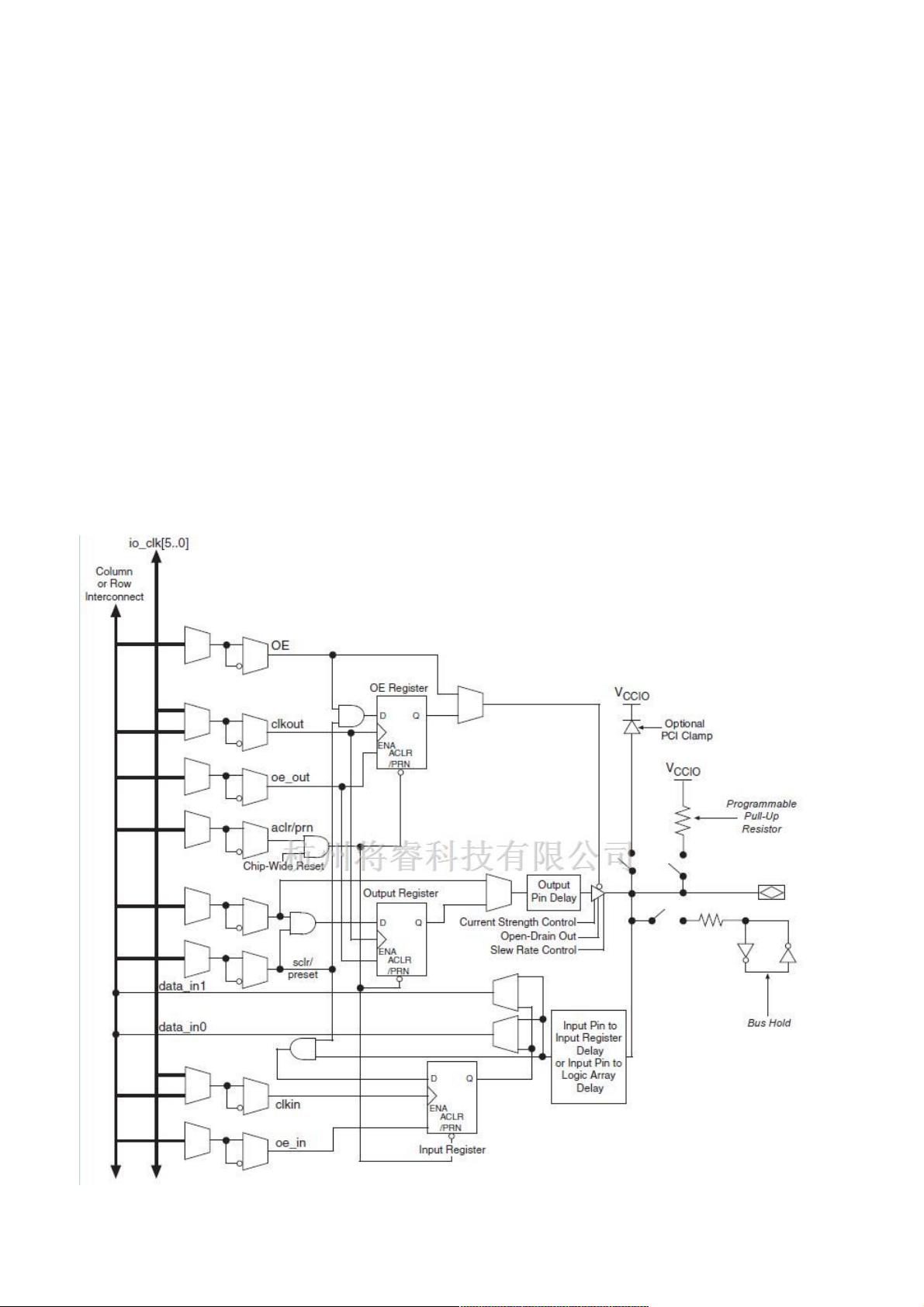

1. IOE(Input Output Element,输入输出单元):这是FPGA与外部电路交互的桥梁。IOE提供了多种电气特性以适应不同的接口标准,如LVTTL、LVCMOS、PCI、LVDS、RSDS等,支持不同电压电平(5V、3.3V、2.5V、1.8V、1.5V等)。例如,ALTERA公司的Cyclone IV E系列EP4CE115F29设备,拥有8个IOBank,每个IOBank能独立支持多种I/O标准,并且可配置驱动电流和上下拉电阻,增强了系统的灵活性。

2. LAB(Logic Array Block,逻辑阵列块):这是FPGA的核心逻辑部件,通常称为CLB(Configurable Logic Block,在Xilinx产品中)。LAB包含了多个可编程逻辑单元,如查找表(Look-Up Tables, LUTs),用于实现基本的逻辑功能。这些LUTs可以通过编程实现任意布尔函数,使得设计者可以构建复杂的数字逻辑电路。LAB的数量和结构因FPGA型号而异,它们可以组合以满足各种规模的逻辑设计需求。

3. Interconnect(内部连接线):这部分负责连接IOE和LAB之间的信号路径。FPGA内部的互连网络非常灵活,可以动态配置,确保信号能在各个部分之间高效、快速地传输。这些连接线路包括垂直和水平的布线资源,以及可编程开关,能够实现复杂的路由策略。

FPGA的工作原理基于配置存储器,这些存储器保存了用户定义的逻辑配置,当FPGA上电时,配置数据会被加载到内部的SRAM单元中,从而决定各个逻辑元素的功能和连接方式。一旦配置完成,FPGA就能按照预设的逻辑行为执行任务。

开发FPGA的过程通常包括以下步骤:

1. 设计:使用硬件描述语言(如Verilog或VHDL)编写代码来描述所需的数字逻辑。

2. 综合:将高级语言代码转换为逻辑门级别的网表,这个过程会优化逻辑并减少资源使用。

3. 布局布线:将生成的网表映射到FPGA的物理结构上,分配逻辑单元和布线资源。

4. 仿真:在逻辑和物理层面验证设计的功能和性能。

5. 下载配置:将最终的配置文件下载到FPGA中,进行硬件验证。

6. 调试和优化:根据测试结果进行必要的修改和优化,直至满足设计需求。

FPGA因其灵活性、高速度和即时原型验证能力,被广泛应用于各种领域,如通信、图像处理、嵌入式系统、航空航天、医疗设备等。随着技术的不断进步,FPGA的性能持续增强,同时其功耗和成本也在逐步降低,这使得FPGA在现代电子设计中扮演着越来越重要的角色。

2020-10-16 上传

2020-07-21 上传

2021-01-27 上传

2020-10-15 上传

2020-10-15 上传

2020-08-30 上传

2010-03-29 上传

2024-03-15 上传

2024-03-09 上传

weixin_38689976

- 粉丝: 6

- 资源: 924

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全