ZYNQ 7010 FPGA开发入门与关键技术

需积分: 0 23 浏览量

更新于2024-06-18

收藏 30.62MB PDF 举报

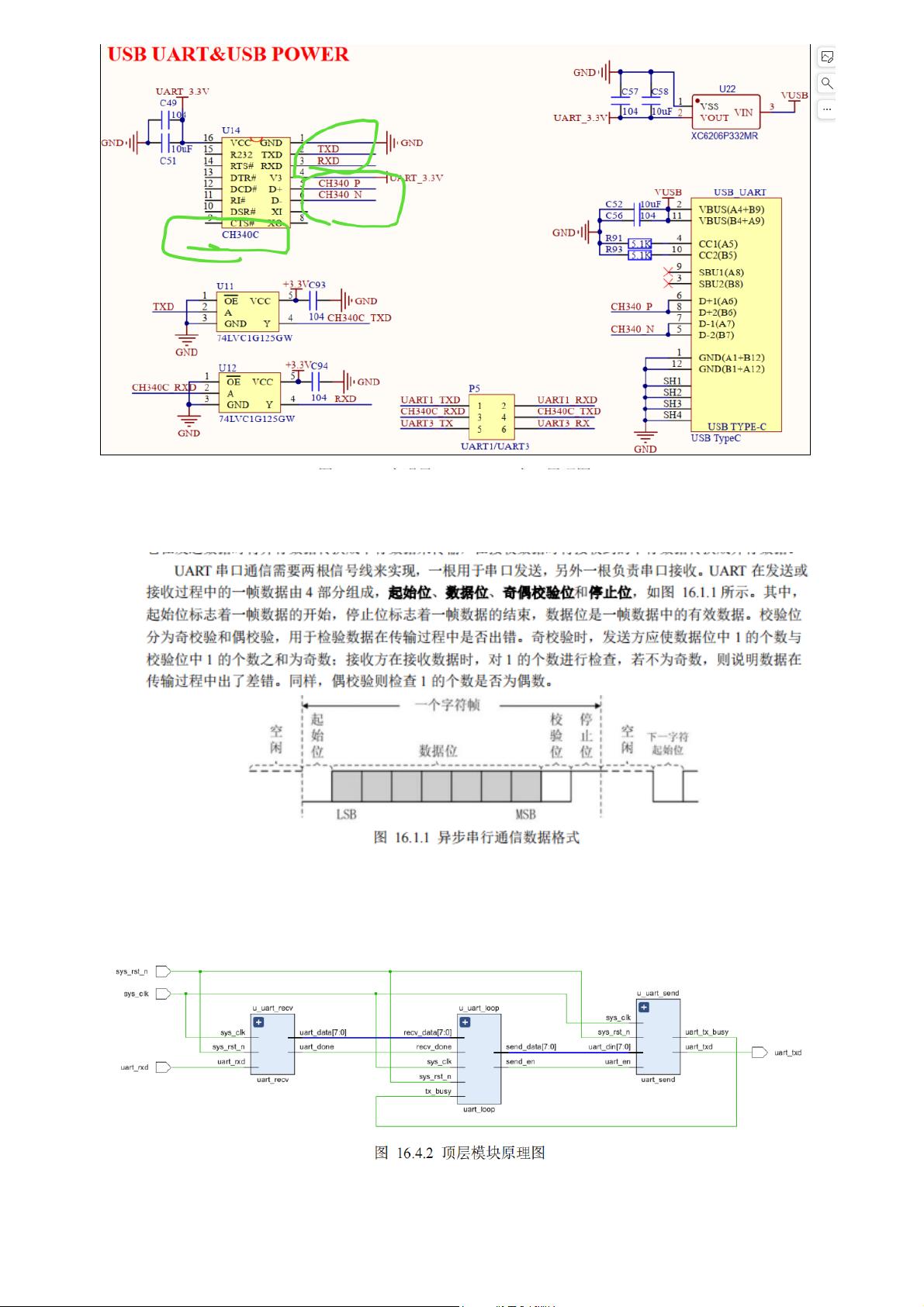

本文档是一份关于赛灵思ZYNQ 7010 FPGA开发的学习笔记,着重记录了两个月的学习过程。ZYNQ是一种基于ARM处理器的系统-on-a-chip (SoC) 芯片,由Xilinx公司生产,其特点在于集成了一颗处理系统(PS)和可编程逻辑部分(PL)。PL可以视为一个FPGA,允许用户灵活地设计硬件逻辑,而PS则负责运行嵌入式操作系统和处理软件任务。

在学习过程中,作者强调了约束文件的作用,这些文件用来配置FPGA的管脚连接,例如通过正点原子提供的开发板管脚信息可以直接复用。ZYNQ的特点是PL部分不能独立固化程序,因为非易失性存储器如SD卡和QSPIFlash接口属于PS区域,需要将软件bit流和elf文件合并成BOOT.BIN文件进行加载,这就涉及到ZYNQ嵌入式SDK的开发流程。

对于调试,作者指出添加调试信息会增加系统内存占用,完成后应将其注释掉。硬件调试依赖于FPGA片上资源,而软件调试则是通过编写测试bench(TB)文件进行。在Verilog设计中,选择reg或wire类型取决于信号在代码中的角色,如always和initial用于定义reg,而assign和输出通常用作wire。理解时序约束有助于调试,比如位运算和移位运算的规则,以及拼接运算符的使用。

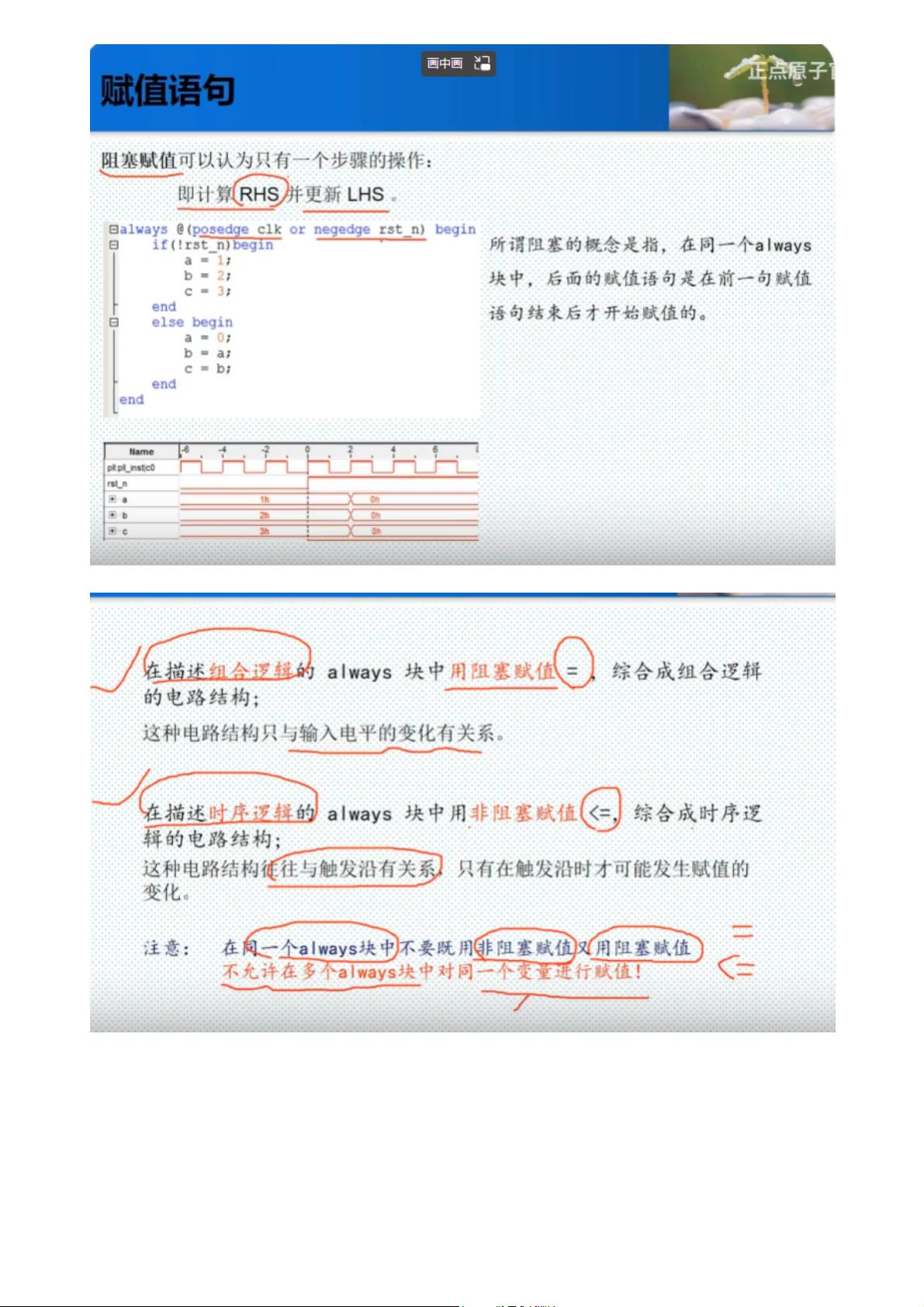

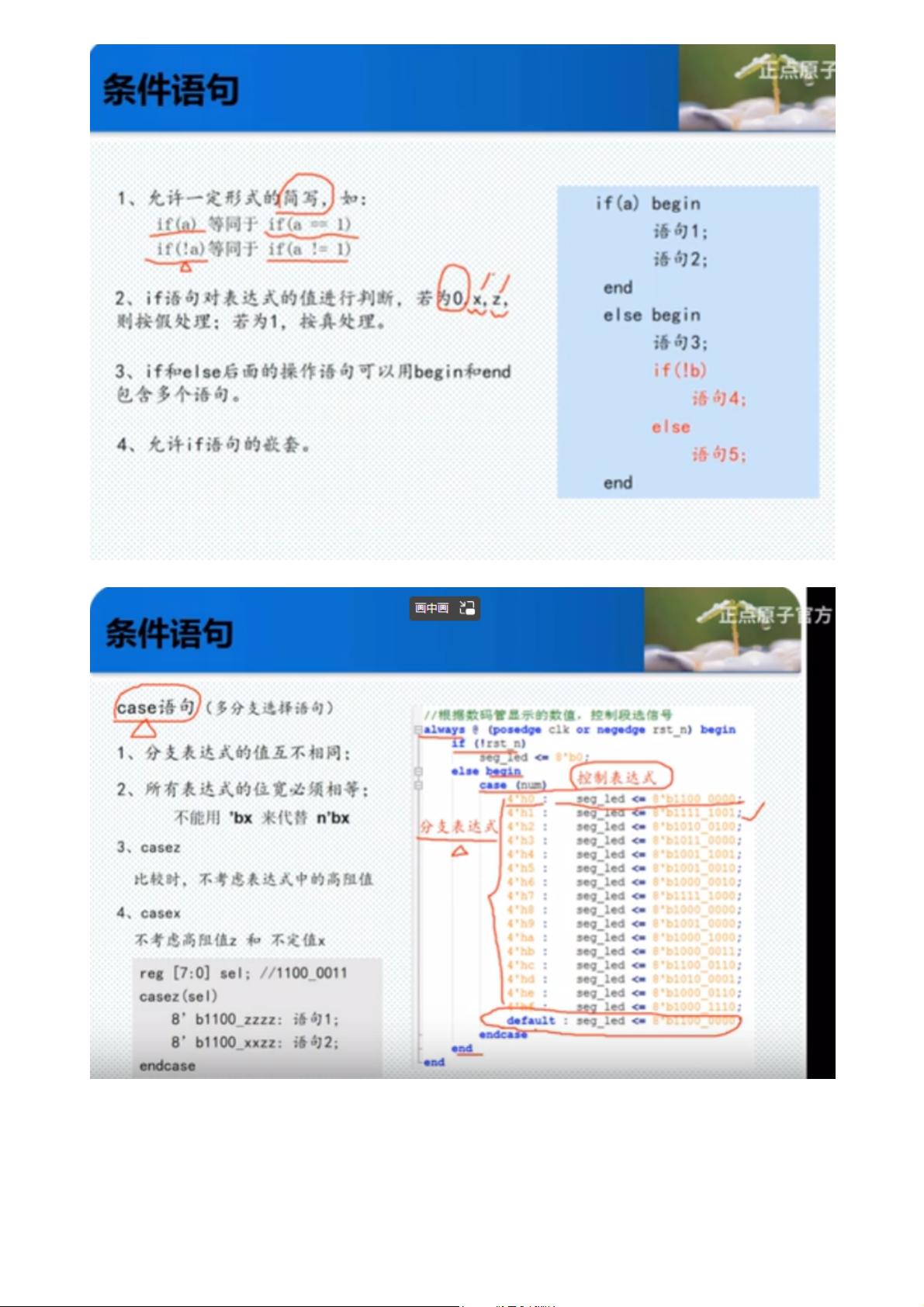

Verilog语言的设计特点是模块化,每个模块是自包含的最小功能单元,类似于C语言中的函数。在设计中,需要注意assign、always和元件实例化的并行与顺序执行差异。always不带时钟时等同于assign,可以作为阻塞或非阻塞赋值。同时,避免在多个always块中对同一变量重复赋值,因为它们是并行执行的,这类似switch语句,但要求变量位宽一致且值不同。

最后,模拟激励是验证设计的重要步骤,包括实验总结和实例化模块时的命名准确性,确保模块间的正确交互。

通过这份笔记,读者可以深入了解ZYNQ 7010开发的各个环节,从硬件配置到软件调试,再到Verilog语言的实际应用,为FPGA开发提供了实用的学习资料。

1337 浏览量

459 浏览量

2021-03-02 上传

308 浏览量

289 浏览量

little·fart

- 粉丝: 122

- 资源: 2

最新资源

- program_fin:用CodeSandbox创建

- sophie-haugland-js1-ma1:JavaScript 1模块分配1

- connect.zip

- next-mongodb-auth

- 安卓Android图书管理系统最新美化版可导入AndroidStudio

- yezuxlc,c语言反码与源码相加,c语言

- jodd,乔德!一套开源Java微框架和工具;软盘大小:tools+ioc+mvc+db+aop+tx+json+html<1.6MB.zip

- MyGraph-开源

- review:有关开发和工程课程的评论网络,更侧重于网络开发

- html5响应式国外城市政府城市宣传网站

- homebrew-freecad:FreeCAD的自制方法

- wordcloud python3.6 3.7 32位.zip

- manufactoring_website

- 安卓Android校园办公用品管理系统可导入AndroidStudio

- 注意:Markdown记事本应用

- Desafio