Verilog FPGA实现USB 2.0高速接口设计与应用

141 浏览量

更新于2024-08-31

1

收藏 542KB PDF 举报

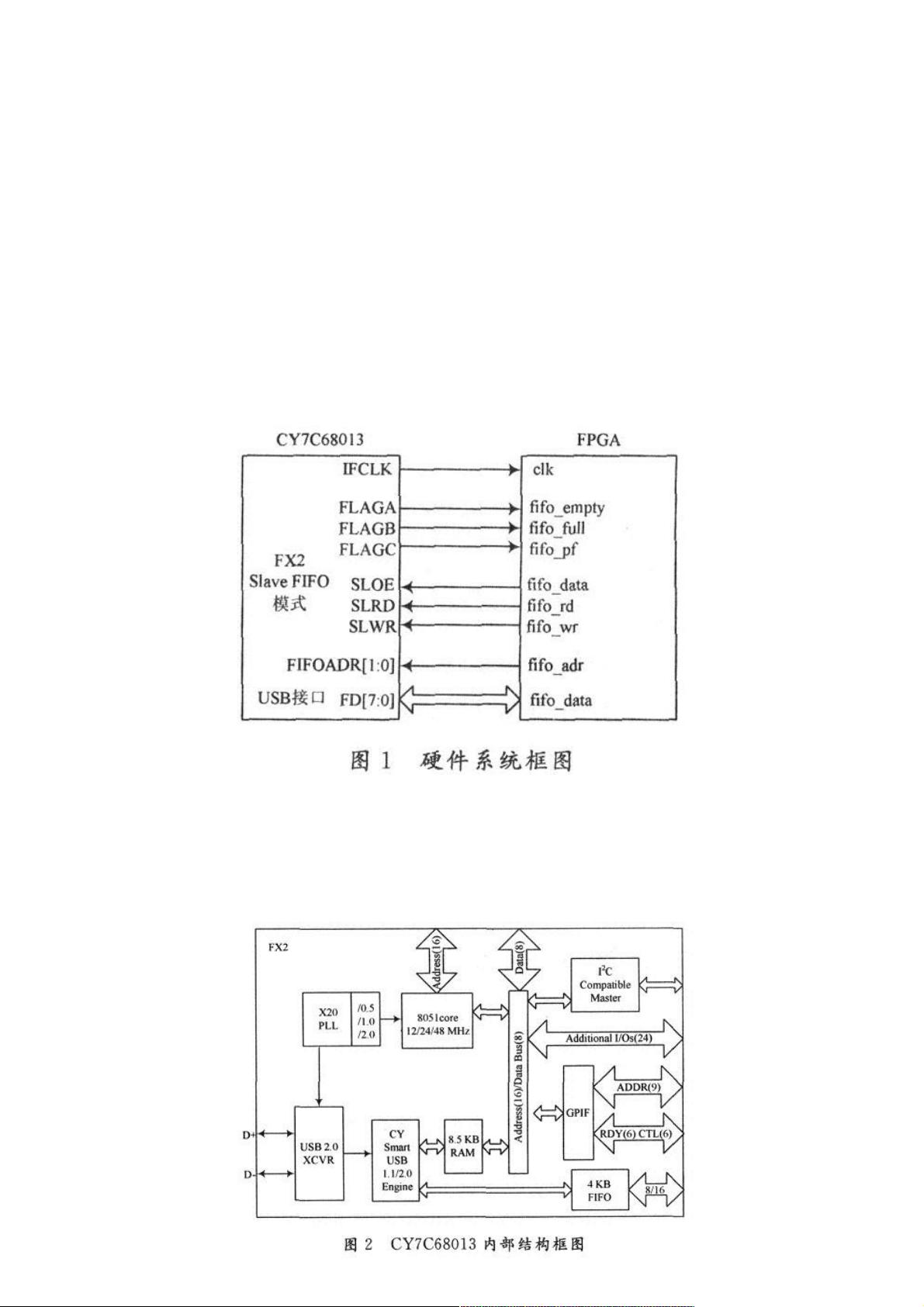

本篇文章主要探讨了基于Verilog的FPGA与USB 2.0高速接口的设计技术。在现代数据采集和传输中,高速USB 2.0接口已经成为常见的解决方案,尤其结合FPGA或DSP,能有效提升数据处理速度。本文设计的核心在于利用 Cypress 公司的USB 2.0接口芯片CY7C68013 的Slave FIFO模式,将FPGA作为外部主控制器,对内置的FX2 USB内部FIFO进行控制。

系统硬件模块设计是文章的重点,首先,设计者构建了一个典型的系统硬件框图,展示出FX2 USB与FPGA之间的连接,包括双向数据总线FD、标志管脚FLAGA~FLAGC、片选信号SLCS、数据总线使能信号SLOE、以及用于选择FIFO端点缓冲区的FIFOADR。FIFO的读写选通信号SLRD和SLWR也在此处发挥作用,确保数据的高效传输。

CY7C68013作为关键的USB 2.0接口芯片,具有显著的结构特点。它集成了增强型8051微控制器、USB引擎、数据收发器、I/O口和大容量FIFO等,性能强大且兼容性好。在Ports模式下,虽然数据传输效率较低,但适合于对速率要求不高的应用场景。而Slave FIFO模式则提供了高效的外部控制,使得FPGA能够像操作普通FIFO一样处理FX2的多层缓冲FIFO,实现了USB 2.0与FPGA之间的无缝数据交互。

此外,文章还提到了GPIF(可编程接口)工作模式,这是一种主机方式,GPIF作为内部主机控制端点FIFO,允许用户通过软件编程来精确控制数据的读写操作,这为更高级的数据处理提供了灵活性和定制化能力。

总结来说,本文介绍了如何通过Verilog在FPGA上实现与USB 2.0接口的高效协作,特别是在数据传输和高速采集场景中的应用,这对于需要处理大量数据或者对传输速率有较高要求的项目具有实际价值。

2020-01-21 上传

2019-08-24 上传

2021-07-13 上传

2023-11-30 上传

2023-08-26 上传

2023-05-16 上传

2023-09-15 上传

2024-04-29 上传

2023-09-01 上传

weixin_38524871

- 粉丝: 6

- 资源: 936

最新资源

- 黑板风格计算机毕业答辩PPT模板下载

- CodeSandbox实现ListView快速创建指南

- Node.js脚本实现WXR文件到Postgres数据库帖子导入

- 清新简约创意三角毕业论文答辩PPT模板

- DISCORD-JS-CRUD:提升 Discord 机器人开发体验

- Node.js v4.3.2版本Linux ARM64平台运行时环境发布

- SQLight:C++11编写的轻量级MySQL客户端

- 计算机专业毕业论文答辩PPT模板

- Wireshark网络抓包工具的使用与数据包解析

- Wild Match Map: JavaScript中实现通配符映射与事件绑定

- 毕业答辩利器:蝶恋花毕业设计PPT模板

- Node.js深度解析:高性能Web服务器与实时应用构建

- 掌握深度图技术:游戏开发中的绚丽应用案例

- Dart语言的HTTP扩展包功能详解

- MoonMaker: 投资组合加固神器,助力$GME投资者登月

- 计算机毕业设计答辩PPT模板下载