Design of Digital Signal Spectrum Analyzer

Based on FPGA

Dewen Qi

1

, Xuan Guo

1

, Weitao Du

1

1

Engineering Center of Digital Audio & Video

Communication University of China

Beijing, China

dewen_qi@cuc.edu.cn

Abstract—This paper presents a hardware software co-design

of embedded digital spectrum analyzer. As a digital hardware

design, it achieves better portability and modularity so that it

could be easily deployed and embedded into other systems as a

module and conduct arbitrary intermediate nodes spectrum

monitoring with ease while such tasks are hard for traditional

spectrum analysis instruments to accomplish since most of them

only provide limited user interface. Besides, this design

implements functions of real-time signal analysis and real-time

spectrum display with VGA port, which traditional embedded

data observation systems, for example SignalTap II Logic

Analyzer, do not have. Furthermore, this design serves as a

sample of hardware software co-design of soft-core processor

based system, which can be used for reference.

Keywords—Spectrum analyzer; FPGA; SOPC; Nios II; FFT

I. INTRODUCTION

Spectrum analyzer is a kind of instrument which analyses

signal spectrum to provide its frequency-domain feature that is

widely used in military, satellite communications, radio

monitoring and other fields. In recent years, the popularity of

digital devices sparked a new revolution in the field of

electronics, and as a result, the spectrum analyzer design also

evolved from conventional analog type to digital type. Among

the digital systems, field-programmable gate array (FPGA), has

advantages of design flexibility, high speed, ease of

modification, low power consumption, which results in its

widespread usage.

There are basically two kinds of methods to observe digital

spectrum. The first approach is using the digital spectrum

analysis instrument, which only provides limited user interface

and not suitable for analyzing system’s internal signal. Another

approach is collecting spectrum data from the embedded logic

analyzer of FPGA or printing spectrum data to personal

computer (PC) through the soft-core processor and then

plotting the spectrum with MATLAB. The second approach

makes it possible for users to assign internal nodes in the

system and monitor the spectrum of them while it is inefficient

and incapable of real-time spectrum analysis. To solve these

problems, this paper proposes a method of embedded digital

spectrum analysis, which not only can analyze signals and

display spectrum in real-time with the help of the fast Fourier

transform (FFT) IP core, but also is so portable that it can be

easily migrated to other systems to monitor spectrum of

intermediate nodes. In conclusion, this design has advantages

of real-time, stability, high reusability and simple peripheral

circuit.

II. S

YSTEM OVERVIEW

A. Overall system Scheme

Based on different approaches of signal analysis, there are

two kinds of spectrum analyzer implementation schemes,

based on the discrete Fourier transform (DFT) of modern

digital signal processing technology or based on the frequency

sweep tuning method, which belongs to traditional heterodyne

signal processing technology. This design chooses the former

approach for the ease of implementing DFT based on digital

devices.

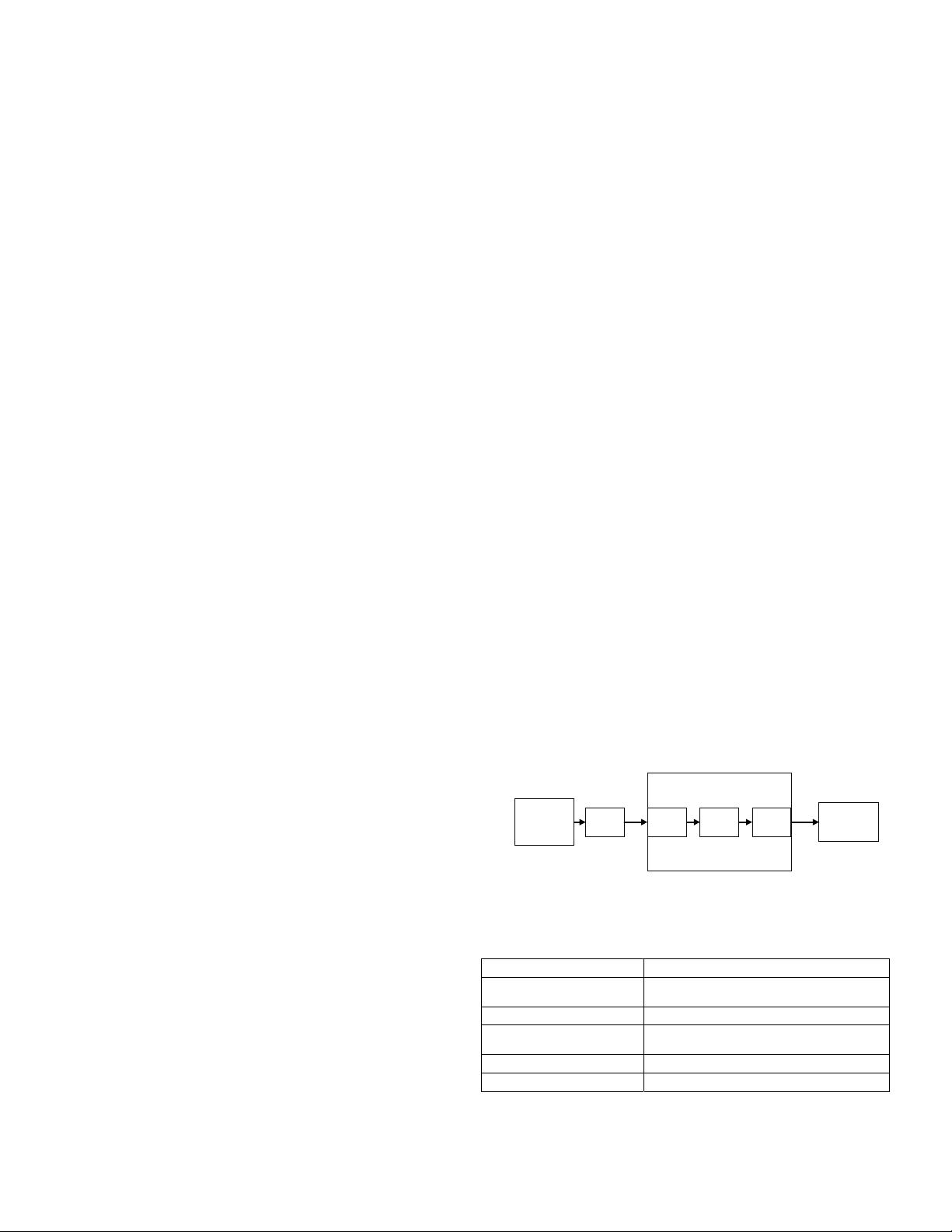

B. System Top-Level Structure

This design mainly consists of three parts: the signal source

for test, FPGA board and video graphics array (VGA) display

as is shown in Fig. 1. The major function of this system is

analyzing input signals and then displaying their spectrum and

energy progress. Besides, this design provides two kinds of

different source signal modes and different FFT processing

modes, as is shown in TABLE I. .

ADC

VGA

Display

Signal

Generator

FPGA Board

Video

DAC

GPIO

FPGA

Chip

Fig. 1. System Block Diagram

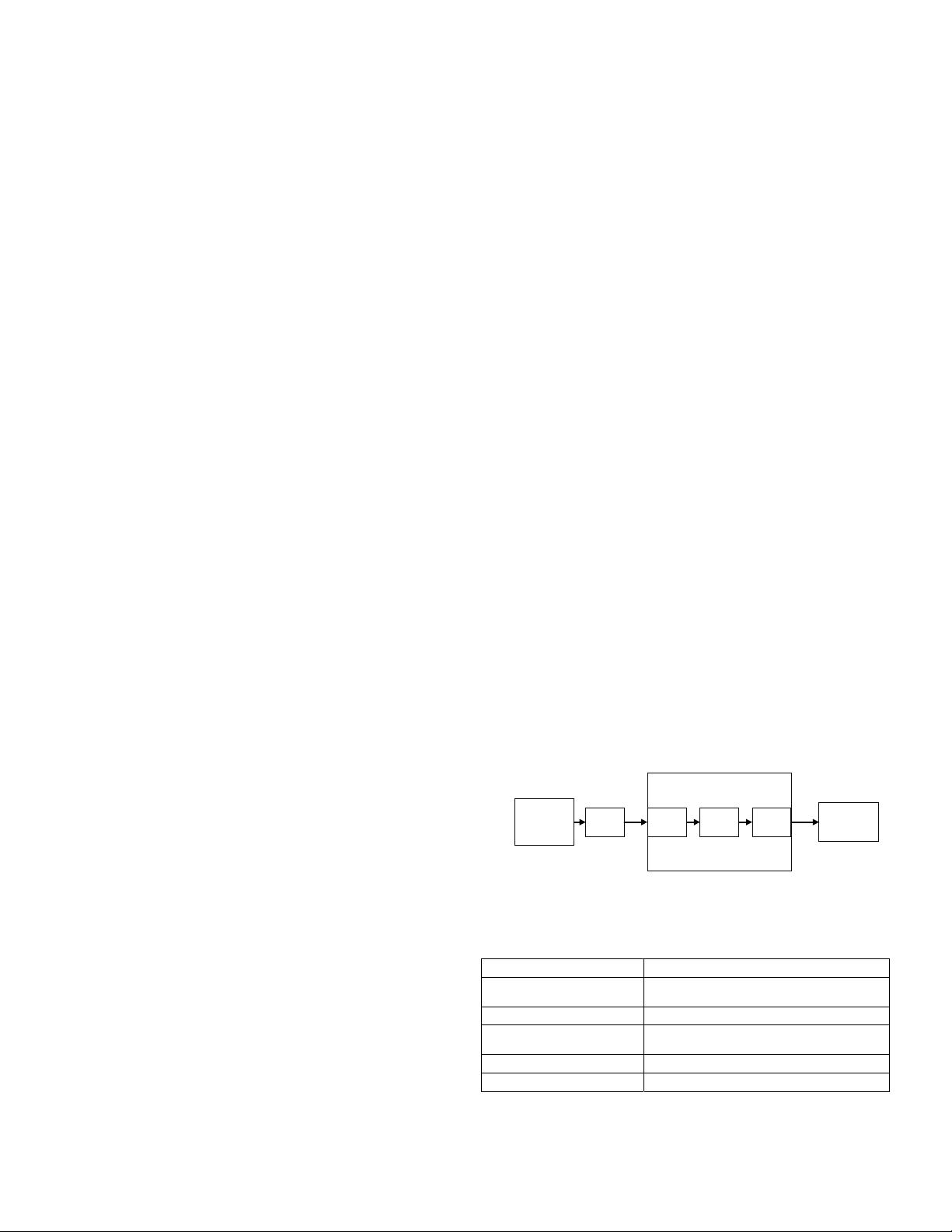

TABLE I. S

YSTEM OPTION

Mode Description

External signal mode

Choose external signals through the ADC

circuit to test.

Internal signal mode Choose internal signals from DDS to test.

CFFT mode

Use FFT algorithm in Nios II to perform

FFT.

FFT IP core mode Use FFT IP core to perform FFT.

DDS frequency adjust Range:0.5M-5MHz; stepper:0.5MHz

978-1-4673-9104-7/15/$31.00 ©2015 IEEE

Proceeding of the 2015 IEEE

International Conference on Information and Automation

Lijiang, China, August 2015