Intel MP规范与APIC多处理器架构解析

需积分: 27 73 浏览量

更新于2024-07-29

收藏 125KB PDF 举报

"Intel MP Specification, APIC"

本文档主要介绍了Intel多处理器(MP)规范,特别是高级可编程中断控制器(APIC)。APIC是x86架构中用于多处理器系统的关键组件,它允许在一个系统中有效地管理和调度多个处理器。这个技术使得在服务器、工作站和高性能计算环境中构建更强大的并行处理系统成为可能。

在x86平台中,APIC扩展了传统的中断控制系统,以支持多处理器环境中的中断路由和处理。传统的中断控制器,如8259 PIC(Programmable Interrupt Controller),在单处理器系统中工作良好,但在多处理器系统中,它们无法有效地处理来自不同处理器的中断,这可能导致性能下降和系统复杂性增加。APIC解决了这个问题,通过提供独立于处理器的中断处理机制,确保每个处理器可以处理自己的中断,从而提高系统的并行性和响应性。

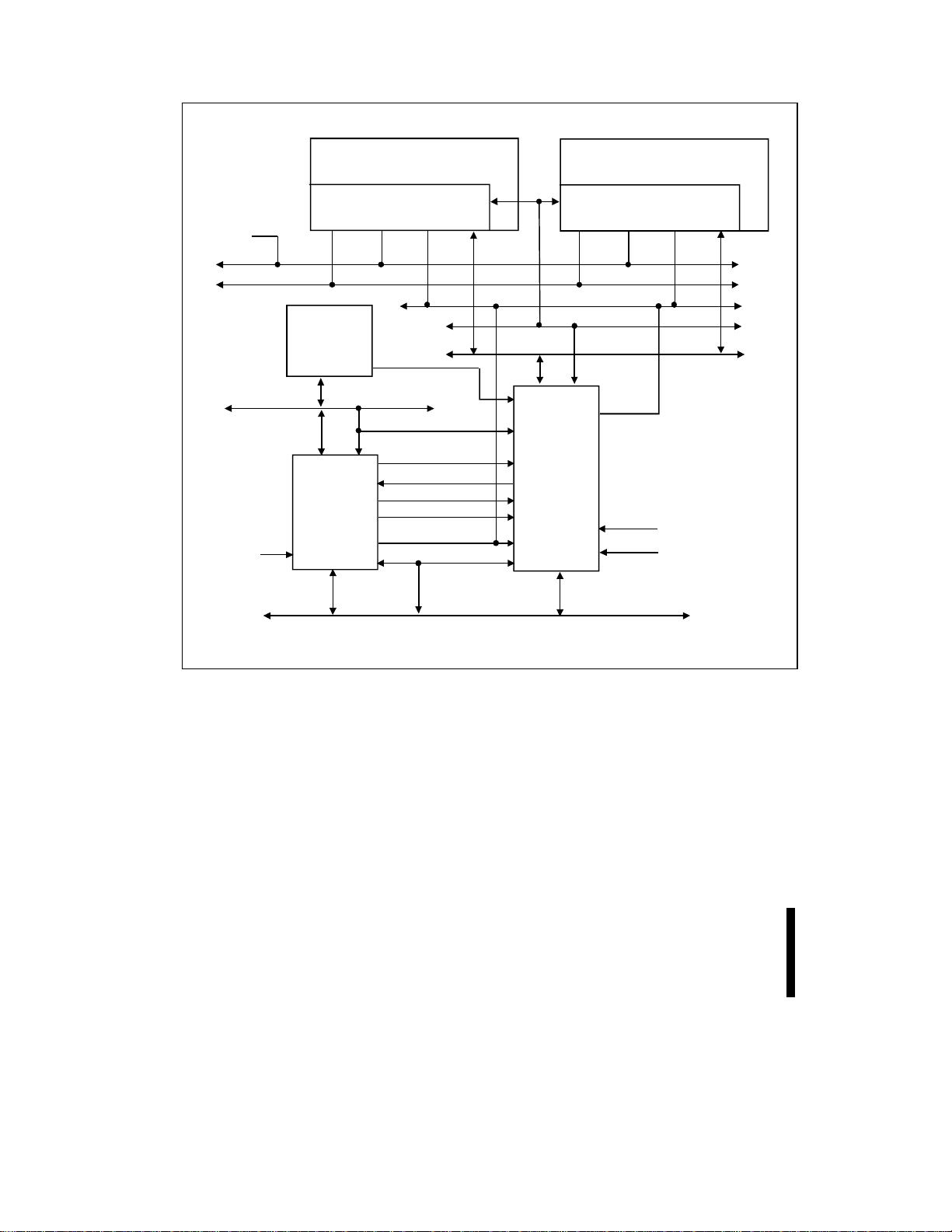

APIC由两部分组成:本地APIC(Local APIC)和I/O APIC(Input/Output APIC)。本地APIC安装在每个处理器上,负责处理来自硬件中断源和软件中断(如IPI,Inter-Processor Interrupts)的中断。I/O APIC则接收来自外设的中断请求,并根据系统配置将它们路由到适当的本地APIC。

Intel MP Specification定义了如何配置和通信这些APICs,以便在多处理器环境中正确地同步和协调操作。它包含了详细的硬件接口、初始化过程、中断处理机制以及处理器间通信的协议。规范还涵盖了错误处理和容错机制,这对于保证系统的稳定性和可靠性至关重要。

在多处理器系统中,APICs使得操作系统可以实现负载均衡,通过向空闲处理器发送IPI来分配任务,从而提高系统整体性能。此外,APIC还支持高级特性,如非屏蔽中断(NMI)和本地定时器中断,这些特性对于操作系统管理和调试非常有用。

需要注意的是,Intel产品并不针对医疗、救生或维持生命的应用设计。这意味着尽管Intel产品在许多方面都表现出色,但在这些关键领域,使用时需要特别谨慎,因为它们可能不满足这些特殊应用的严格安全标准。

Intel保留随时更改产品规格和描述的权利,而无需事先通知。如果存在已知的设计缺陷或错误(即“errata”),Intel可能会提供更新的信息。第三方品牌和名称归各自所有者所有。

总结来说,Intel MP Specification和APIC是x86多处理器系统的核心,提供了高效、灵活的中断管理和处理器间通信,促进了现代多核系统的设计和优化。

2009-03-25 上传

2009-06-23 上传

2013-04-19 上传

2023-05-09 上传

2023-06-11 上传

2023-06-11 上传

2023-12-24 上传

2023-07-27 上传

2023-05-22 上传

abennon

- 粉丝: 0

- 资源: 6

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能