A/D转换器输入端的连接误区与解决方案

28 浏览量

更新于2024-09-01

收藏 261KB PDF 举报

"本文主要探讨了A/D转换器输入端的正确理解和常见问题,强调了错误连接可能导致的测量误差。文章以一个简单的A/D转换器和集成采样保持(S/H)电路的应用实例作为起点,解释了采样保持电路的工作原理,并分析了实际电路中缓冲器的非理想特性如何影响A/D转换结果。文中通过等效电路模型揭示了采样过程中输入电压下降的原因,并提供了计算电容大小以减少压降的方法。"

A/D转换器是嵌入式系统中关键的组成部分,用于将模拟信号转换为数字信号。在设计中,正确理解和连接A/D转换器的输入端至关重要,因为错误的连接可能导致测量值偏离实际,从而影响系统的精度和性能。

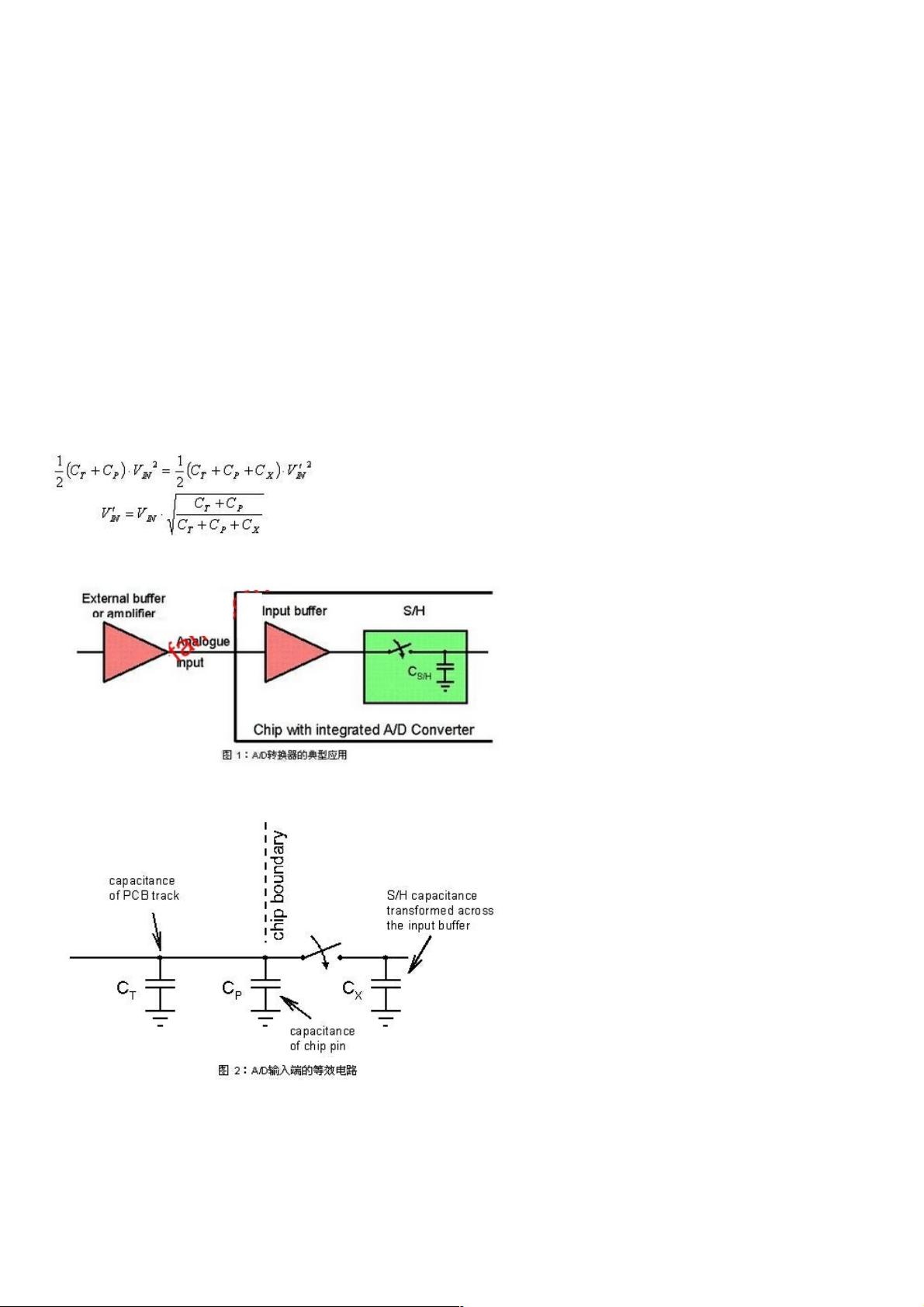

图1展示了一个包括A/D转换器和采样保持电路的简单应用,其中的采样保持电路由一个闭合开关和采样电容组成,同时使用一个模拟缓冲器来保护外部电路。尽管看似无误,但实际运行中,缓冲器的非理想特性(即作为一个阻抗变换器)会导致输入端电压下降。这是因为缓冲器的输入端电容与其输出端电容有关,当采样电容与输入端电容并联时,输入电压会下降。

为了更好地理解这个问题,可以使用图2所示的等效电路进行分析。在采样期间,外部电容(CT+CP)与采样保持电容(CX)并联,导致输入电压下降。若外部放大器无法快速响应这种变化,输入电压的降低将更加显著。计算表明,输入电压可能下降到95%,这显然会影响A/D转换的准确性。

为减小这种压降,可以通过增加连接到A/D转换器输入端的电容来实现。文章提供了一个计算公式,说明了为使压降低于A/D转换器的1/2 LSB,所需的最小电容。以12位A/D转换器为例,如果电容变化为0.5pF,那么输入端至少需要4nF的电容来确保压降小于1/2LSB。

遗憾的是,A/D转换器的数据手册往往没有提供足够的信息来精确计算这些参数。设计师需要根据实际应用环境和设备的规格来估算合适的电容值,以确保测量的准确性和系统的稳定性。

理解A/D转换器输入端的工作机制,以及如何优化其连接以避免测量误差,是成功实施嵌入式系统设计的关键。通过仔细考虑电路的等效模型和缓冲器的非理想特性,可以有效地改善A/D转换的性能,从而提升整体系统的精度。

167 浏览量

2020-10-21 上传

123 浏览量

134 浏览量

2021-09-30 上传

105 浏览量

123 浏览量

189 浏览量

125 浏览量

weixin_38613173

- 粉丝: 3

- 资源: 928

最新资源

- PJBlog2 qihh

- TodoRestApi:待办事项其余应用程序的服务器端

- spread:SPREAD 移动前景中的所有图形并尝试以愉快的方式排列它们。-matlab开发

- SeleniumDemo:Selenium自动化框架模板

- For-While

- kaggle dataset: publicassistance-数据集

- PHPWind论坛 prettyshow

- multitranslator

- 使用CNN的OCR韩语辅助应用程序

- SwiftUI仿表格效果完成代码

- Impermalink:用于创建缩短的,即将到期的链接的工具

- anime-sync

- Arduino-基于Web的MP3播放器-项目开发

- 预算跟踪器:使用503020方法的简单预算跟踪器

- TITUNI:Tituni - 标题程序。 还在测试中。-matlab开发

- BBSxp论坛 蓝语风格