CPLD/FPGA开发入门指南:5分钟上手与实践

下载需积分: 0 | PDF格式 | 2.01MB |

更新于2024-09-11

| 113 浏览量 | 举报

本文档旨在为初学者提供CPLD/FPGA开发的入门指南,帮助他们快速理解和掌握这一技术。CPLD(复杂可编程逻辑器件)和FPGA(现场可编程门阵列)在现代电子行业中扮演着重要角色,特别适合用于定制化硬件设计。

文章首先介绍了开发CPLD/FPGA的背景和必要性,随着电子行业的进步,这些可编程逻辑器件被广泛应用,成为创新产品开发的有效工具。作者结合个人学习经历,分享了一个简洁的开发流程,主要包括以下步骤:

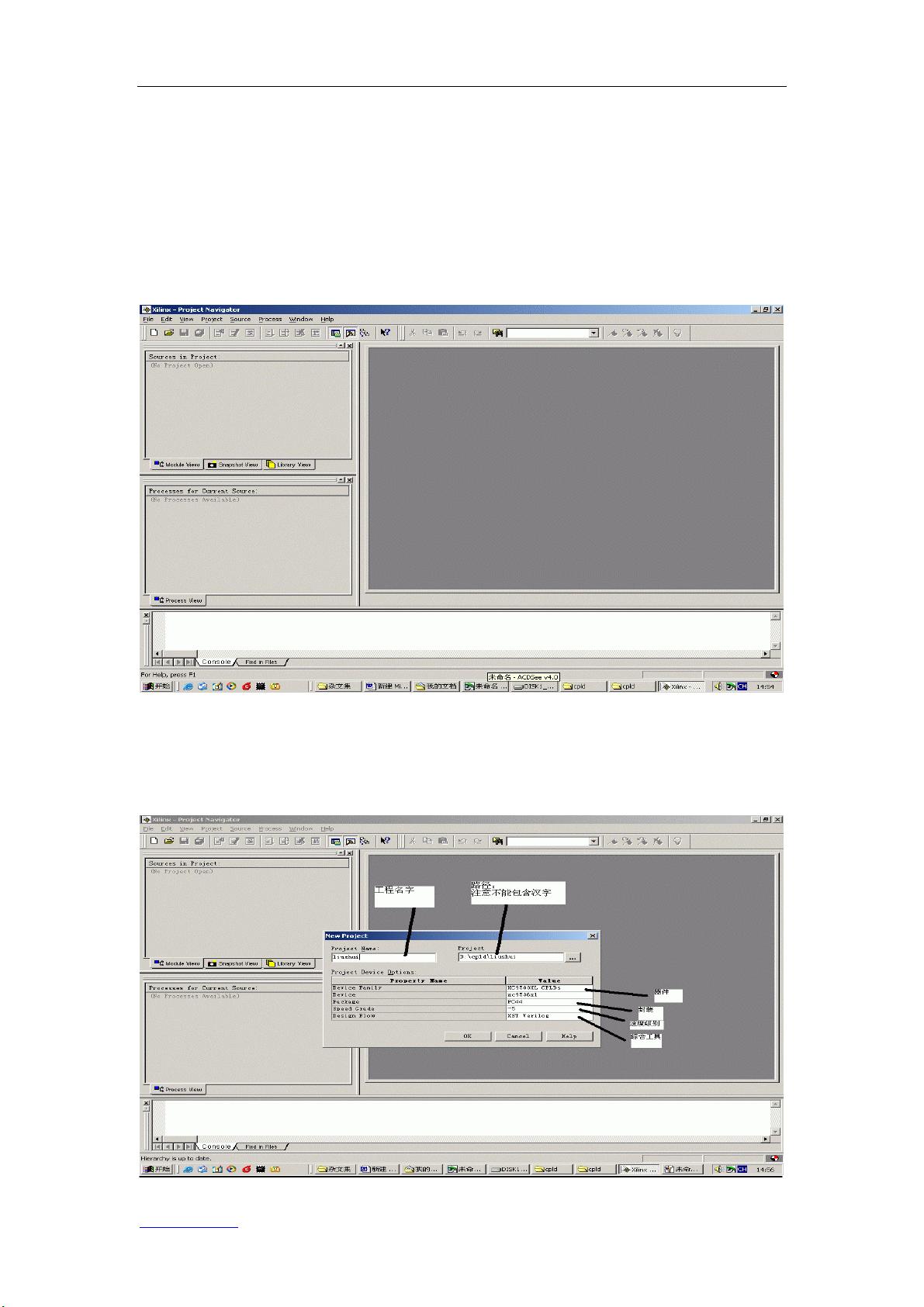

1. **硬件准备**:首先,读者需要准备一个基础的CPLD系统,包括10M有源晶体、支持JTAG接口的在线下载设备、AS1117电源模块、1K电阻以及8个发光管用于显示效果。同时,推荐使用Xilinx的集成编译软件ISE 5.0或6.0,注意确保计算机配置足够强大以避免运行时内存消耗过大导致死机。

2. **软件安装与选择**:安装ISE软件,因其对计算机内存需求较高,建议使用高性能配置。作者建议初学者学习Verilog HDL语言,因为它语法更接近C语言,上手速度快,对于入门者较为友好。

3. **编写测试代码**:以驱动8个发光管轮流点亮为例,利用Verilog HDL编写一段简单代码,通过设置计数器控制灯的点亮顺序,以便观察工作流程。代码中的reset和CLK信号用于复位和时钟控制,LED数组则作为输出。

4. **代码示例**:作者提供了详细的代码片段,展示了如何定义输入、输出和寄存器,并使用always块处理时钟上升沿触发事件。在复位条件下,所有LED熄灭,随后计数器启动,每计数满一次,一个LED会点亮。

通过这个教程,初学者可以逐步理解CPLD/FPGA的开发流程,从硬件配置到软件编程,再到实际电路操作。尽管作者强调这只是一个简单的指南,但它为新手提供了一个坚实的基础,可以帮助他们快速进入CPLD/FPGA的世界并提升实践能力。同时,鼓励读者在实践中提出疑问和改进意见,以进一步提升技术水平。

相关推荐

悟hzq

- 粉丝: 0

最新资源

- JS图片放大:自定义放大倍数的实现方法

- C# WinForm实现多文档标签选项卡技术分享

- Haar级联技术:人脸、眼睛和鼻子检测方法

- 情人节特供:php制作简易表白网站教程分享

- 实现websocket通信:客户端与WinformSocket交互示例

- PR视频编辑必备:FilmImpact转场预设包深度体验

- Booksy书评应用:Code Institute开发的里程碑项目

- 使用maven-runner轻松安装并运行jar文件

- Hibernate Synchronizer插件:Eclipse环境下的实体生成

- mexplus C Matlab MEX开发套件:简化MEX开发工具包

- wince6.0系统兼容FTD232 USB转串口驱动发布

- Java技术在建库资料库建设中的应用

- OvePlayer 0.6:全新钢琴谱播放体验

- pydy工具包:Python多体动力学研究与模型仿真

- 在Titanium中使用Google云消息传递处理通知

- Juniper-main:心理健康检查机器人的Java实现