2-8

Summarizing the results, it can be concluded

that the MOSFET transistor can be switched

between its highest and lowest impedance states

(either turn-on or turn-off) in four time intervals.

The lengths of all four time intervals are a

function of the parasitic capacitance values, the

required voltage change across them and the

available gate drive current. This emphasizes the

importance of the proper component selection

and optimum gate drive design for high speed,

high frequency switching applications.

Characteristic numbers for turn-on, turn-off

delays, rise and fall times of the MOSFET

switching waveforms are listed in the transistor

data sheets. Unfortunately, these numbers

correspond to the specific test conditions and to

resistive load, making the comparison of

different manufacturers’ products difficult. Also,

switching performance in practical applications

with clamped inductive load is significantly

different from the numbers given in the data

sheets.

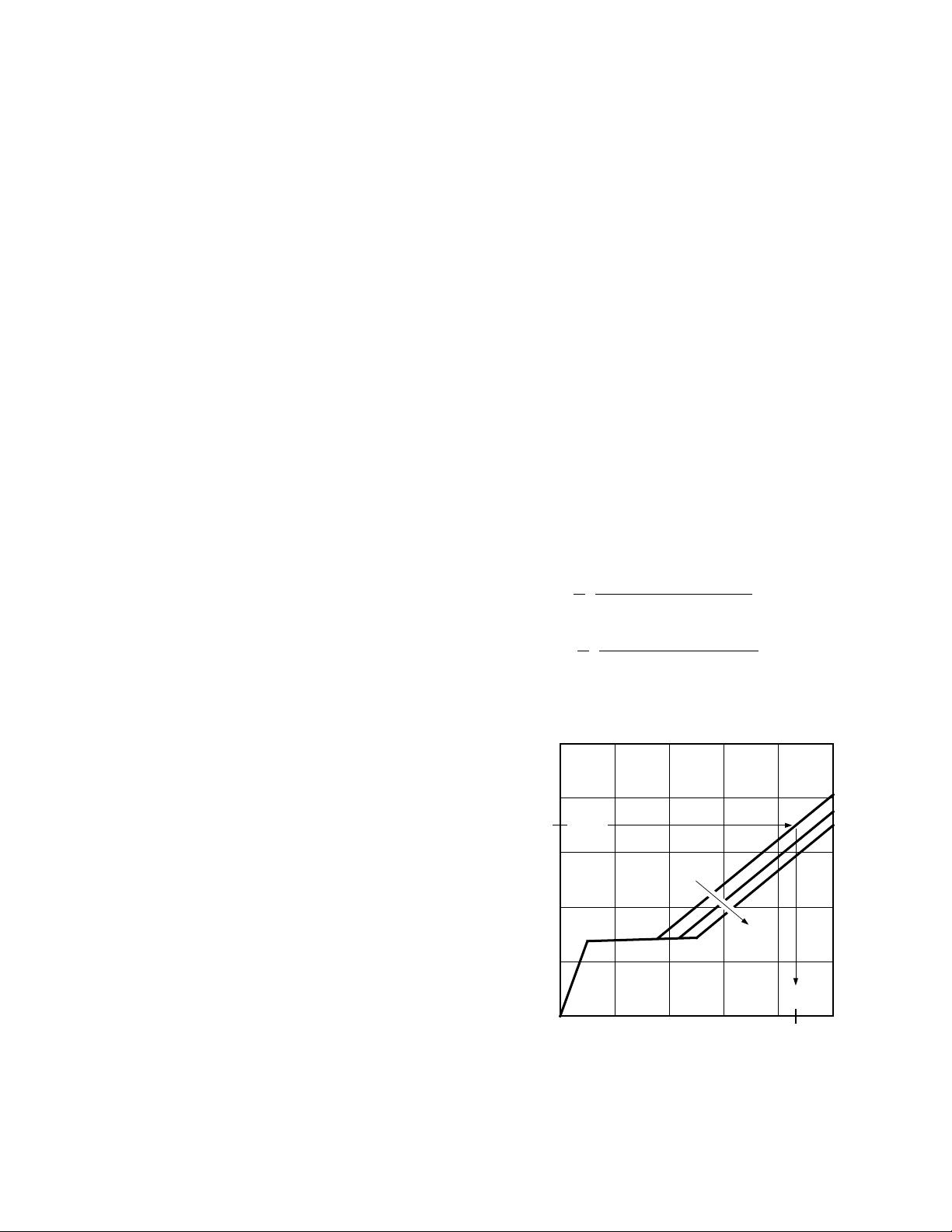

C. Power Losses

The switching action in the MOSFET

transistor in power applications will result in

some unavoidable losses, which can be divided

into two categories.

The simpler of the two loss mechanisms is

the gate drive loss of the device. As described

before, turning-on or off the MOSFET involves

charging or discharging the C

ISS

capacitor. When

the voltage across a capacitor is changing, a

certain amount of charge has to be transferred.

The amount of charge required to change the

gate voltage between 0V and the actual gate

drive voltage V

DRV

, is characterized by the

typical gate charge vs. gate-to-source voltage

curve in the MOSFET datasheet. An example is

shown in Fig. 6.

This graph gives a relatively accurate worst

case estimate of the gate charge as a function of

the gate drive voltage. The parameter used to

generate the individual curves is the drain-to-

source off state voltage of the device. V

DS(off)

influences the Miller charge – the area below the

flat portion of the curves – thus also, the total

gate charge required in a switching cycle. Once

the total gate charge is obtained from Fig. 6, the

gate charge losses can be calculated as:

DRVGDRVGATE

fQVP ⋅⋅=

where V

DRV

is the amplitude of the gate drive

waveform and f

DRV

is the gate drive frequency –

which is in most cases equal to the switching

frequency. It is interesting to notice that the

Q

G

⋅f

DRV

term in the previous equation gives the

average bias current required to drive the gate.

The power lost to drive the gate of the

MOSFET transistor is dissipated in the gate

drive circuitry. Referring back to Figures 4 and

5, the dissipating components can be identified

as the combination of the series ohmic

impedances in the gate drive path. In every

switching cycle the required gate charge has to

pass through the driver output impedances, the

external gate resistor, and the internal gate mesh

resistance. As it turns out, the power dissipation

is independent of how quickly the charge is

delivered through the resistors. Using the resistor

designators from Figures 4 and 5, the driver

power dissipation can be expressed as:

OFFDRV,ONDRV,DRV

IG,GATELO

DRVGDRVLO

OFFDRV,

IG,GATEHI

DRVGDRVHI

ONDRV,

PPP

RRR

fQVR

2

1

P

RRR

fQVR

2

1

P

+=

++

⋅⋅⋅

⋅=

++

⋅⋅⋅

⋅=

Vgs, Gate-to-Source Voltage (V)

Qg, Total Gate Charge (nC)

V

DS

V

DRV

Q

G

Fig. 6. Typical gate charge vs. gate-to-source

voltage.