TMS320F28xx/28xxx DSCs

模拟接口设计综述

5ZHCA063–2008

年

5

月

www.ti.com.cn

3.1.1 Required External Components for the ADC

ADCINA[7:0]

ADCINB[7:0]

ADCLO

ADCREFIN

ADCRESEXT

ADCREFP

ADCREFM

V

DD1A18

V

DD2A18

V

SS1AGND

V

SS2AGND

V

DDA2

V

SSA2

V

DDAIO

V

SSAIO

Analog�Input�0�V�to�3�V�with�respect�to ADCLO

Connect�to�analog�ground

Float�or�ground�if�internal�reference�is�used

2.2�µF

(A)

2.2�µF

(A)

22�K�

ADC Analog�Power�Pin�(1.8�V)

ADC Analog�Power�Pin�(1.8�V)

ADCREFP and ADCREFM

should�not�be�loaded�by

external�circuitry

ADC Analog�Ground�Pin

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�I/O�Ground�Pin

ADC�16-Channel

Analog�Inputs

ADC�External�Current

Bias�Resistor

ADC�Reference�Positive�Output

ADC�Reference�Medium�Output

ADC�Power

ADC Analog�and

Reference�I/O�Power

3.1.2 Analog Input Signal Interface

Source

Signal

AC

R

8

ADCIN0

C

10�pF

p

R

1�k

on

�

C

1.64�pF

h

28x�DSP

Switch

www.ti.com

ADC Set-Up and Operation

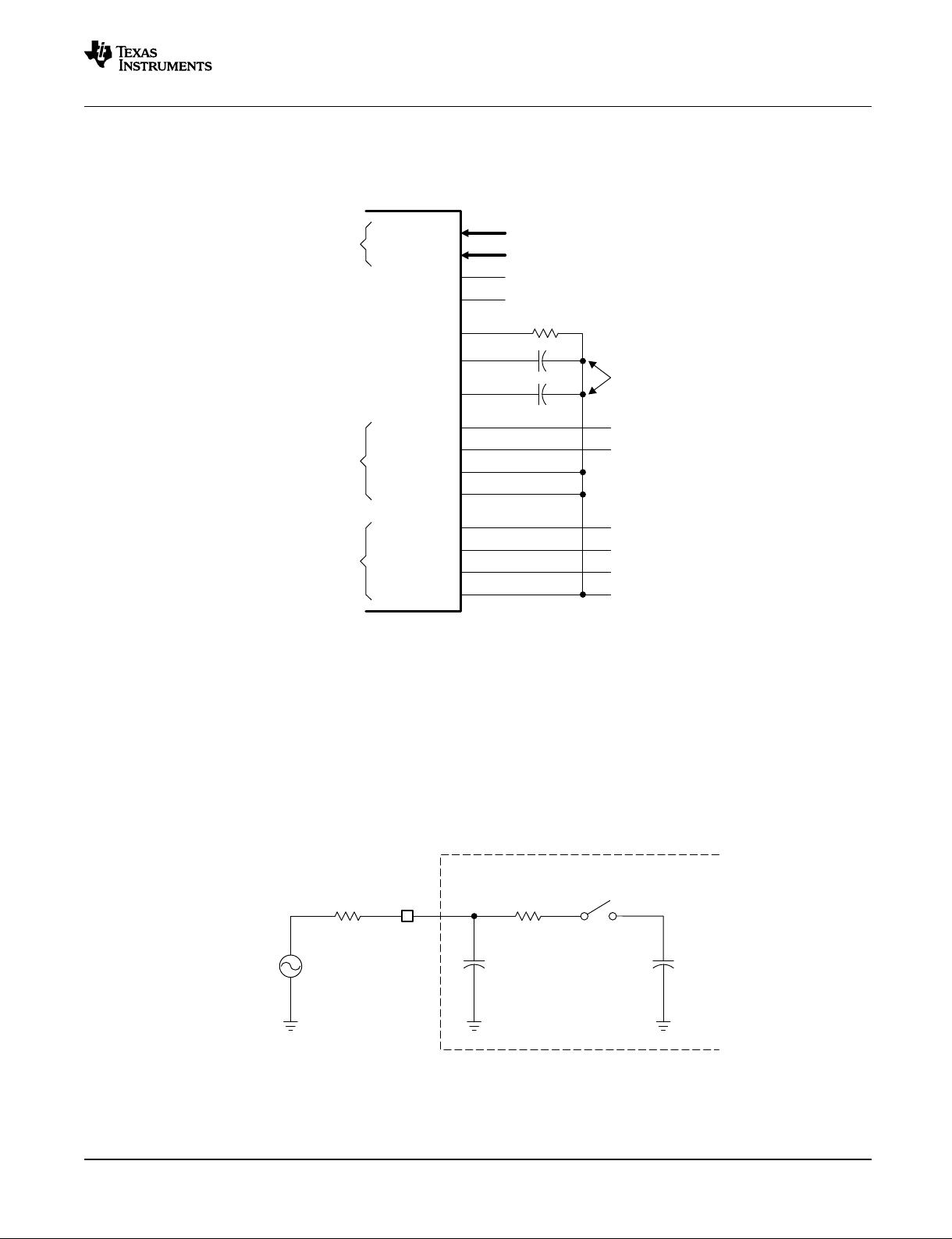

Few external components are required for biasing of internal band gap reference and filtering noise on

reference voltage signals. Figure 2, reproduced from F280xx data sheets, shows these parts and their

connections.

Figure 2. ADC Pin Connections for TMS320F280xx

These pins must be connected as shown above. The F281x devices require different values for these

parts (Appendix A).

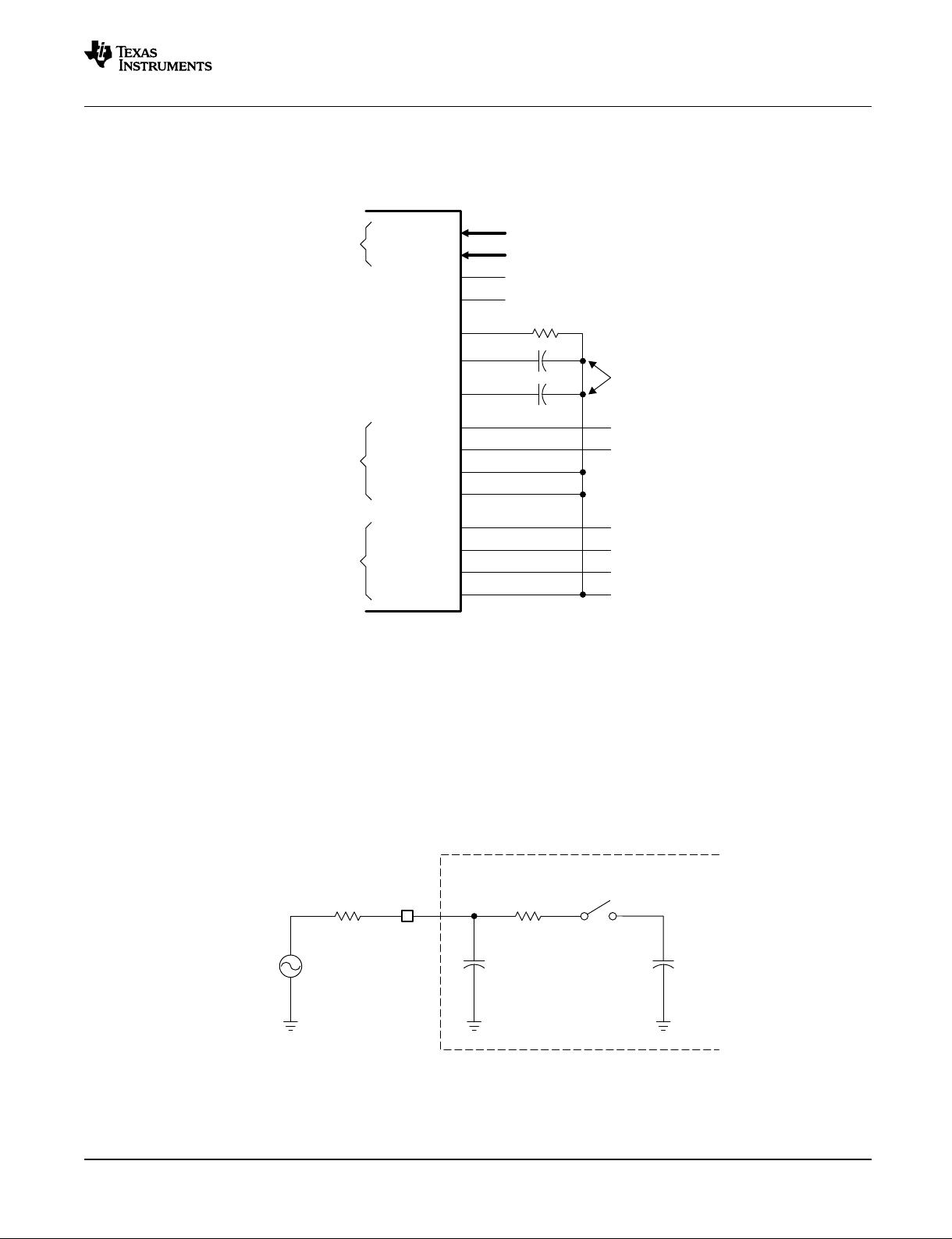

The next step is to design the hardware interface connecting the input analog signals to the ADCINxx

pins. Note that each input analog signal sees the load from the ADCIN pin as shown in Figure 3. C

h

is the

sample capacitor and R

on

is the ON resistance of the multiplexer path. C

p

is the parasitic capacitance

associated with the ADCIN pin.

Figure 3. Analog Input Impedance Model (F280xx)

SPRAAP6A– May 2008 An Overview of Designing Analog Interface With TMS320F28xx/28xxx DSCs 5

Submit Documentation Feedback

3.1.1 Required External Components for the ADC

ADCINA[7:0]

ADCINB[7:0]

ADCLO

ADCREFIN

ADCRESEXT

ADCREFP

ADCREFM

V

DD1A18

V

DD2A18

V

SS1AGND

V

SS2AGND

V

DDA2

V

SSA2

V

DDAIO

V

SSAIO

Analog�Input�0�V�to�3�V�with�respect�to ADCLO

Connect�to�analog�ground

Float�or�ground�if�internal�reference�is�used

2.2�µF

(A)

2.2�µF

(A)

22�K�

ADC Analog�Power�Pin�(1.8�V)

ADC Analog�Power�Pin�(1.8�V)

ADCREFP and ADCREFM

should�not�be�loaded�by

external�circuitry

ADC Analog�Ground�Pin

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�Ground�Pin

ADC Analog�Power�Pin�(3.3�V)

ADC Analog�I/O�Ground�Pin

ADC�16-Channel

Analog�Inputs

ADC�External�Current

Bias�Resistor

ADC�Reference�Positive�Output

ADC�Reference�Medium�Output

ADC�Power

ADC Analog�and

Reference�I/O�Power

3.1.2 Analog Input Signal Interface

Source

Signal

AC

R

8

ADCIN0

C

10�pF

p

R

1�k

on

�

C

1.64�pF

h

28x�DSP

Switch

www.ti.com

ADC Set-Up and Operation

Few external components are required for biasing of internal band gap reference and filtering noise on

reference voltage signals. Figure 2, reproduced from F280xx data sheets, shows these parts and their

connections.

Figure 2. ADC Pin Connections for TMS320F280xx

These pins must be connected as shown above. The F281x devices require different values for these

parts (Appendix A).

The next step is to design the hardware interface connecting the input analog signals to the ADCINxx

pins. Note that each input analog signal sees the load from the ADCIN pin as shown in Figure 3. C

h

is the

sample capacitor and R

on

is the ON resistance of the multiplexer path. C

p

is the parasitic capacitance

associated with the ADCIN pin.

Figure 3. Analog Input Impedance Model (F280xx)

SPRAAP6A– May 2008 An Overview of Designing Analog Interface With TMS320F28xx/28xxx DSCs 5

Submit Documentation Feedback

模数转换器需要的外部器件

为了偏置内部带宽间隔的参考和实现参考电压信号的滤波,需要添加一些外部器件。图

2

,显示了

F280xx

数

据手册中这一部分的连接和器件。

3.1.1

图

2. TMS320F280xx

芯片的

ADC

的引脚连接

这些引脚必须按照上面图来连接,对于

F281x

芯片需要不同的值,在附件

A

中可以看到。

模拟信号输入接口

这一步是设计输入模拟信号和

ADCINxx

引脚连接的硬件接口,需要注意的是,每一个输入的模拟信号都被看

作是

ADCIN

引脚的负载,如图

3

所示,

C

h

是

采样

电容,

R

on

是多路复用的导通电阻,

C

p

是和

ADCIN

引脚连接的

寄生电容。

3.1.2

图

3.

模拟输入阻抗模型

(F280xx)

模数转换器的准备和运行

已收录资源合集

已收录资源合集