时钟信号设计:布局与布线策略

需积分: 9 45 浏览量

更新于2024-09-07

收藏 160KB PDF 举报

"时钟信号设计是电子设计中的关键环节,包括布局和布线策略,对系统的稳定性和性能有着重要影响。本文主要介绍了时钟设计的一些基本原则和注意事项,旨在帮助新手理解和实施有效的时钟信号设计。

时钟布局设计应当遵循以下原则:

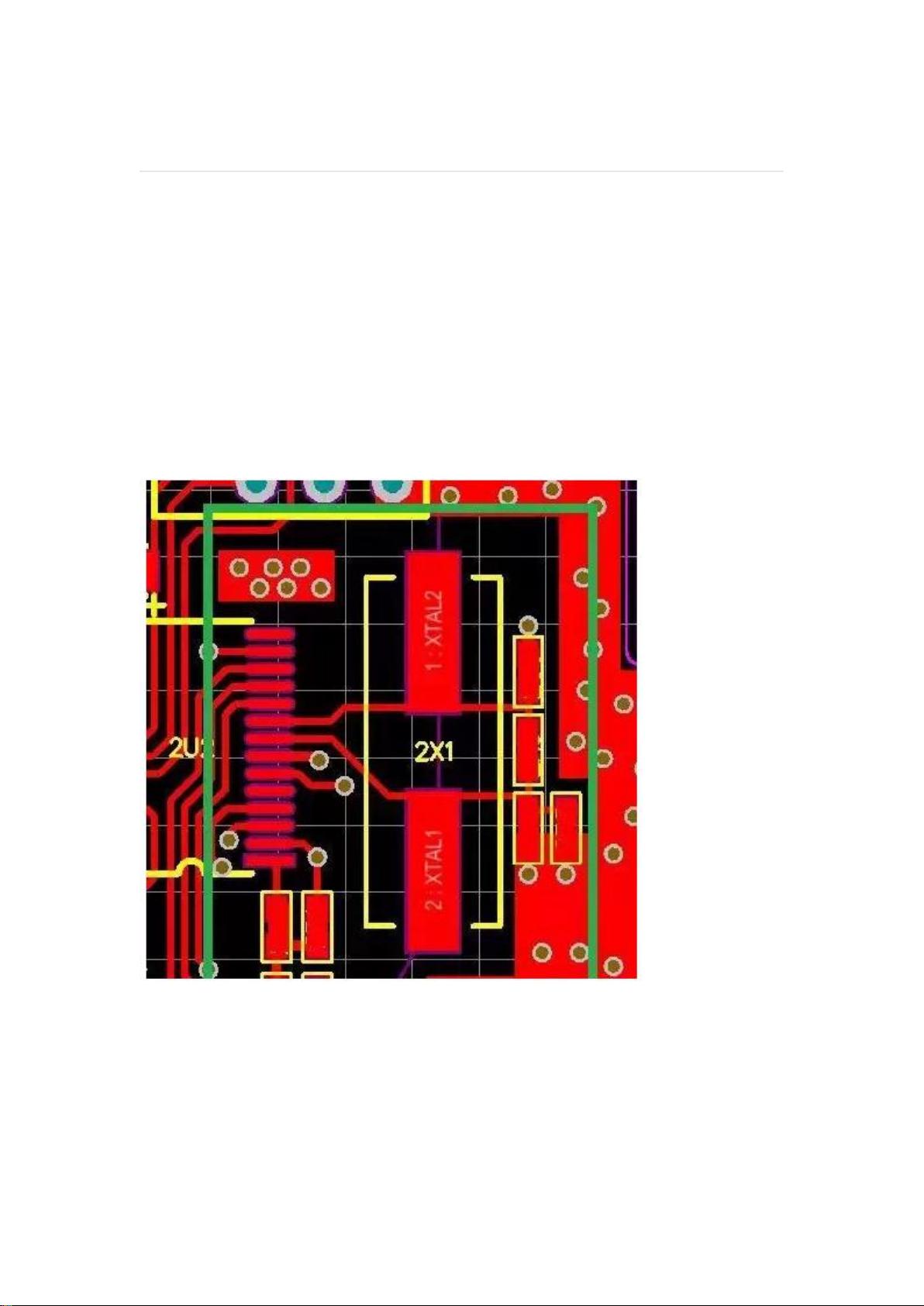

1. 时钟晶体及其相关电路应位于PCB的中心位置,周围应有良好的接地层,以减少干扰。不应将时钟电路设计在子卡或子板上,而是应置于主时钟板或承载板上。

2. 在时钟电路区域,仅布设与时钟相关的器件,避免混合其他电路。晶体附近和下方不应有其他信号线穿过,以保持地平面的连续性,防止地环路的形成,减少高频干扰。

3. 对于时钟晶体和时钟电路,可采取屏蔽措施,如使用金属外壳,以减少射频辐射。

4. 如果晶体外壳为金属,应在晶体下方铺铜并与地平面建立良好电气连接,通过多孔接地,以利于射频电流的释放和散热。

时钟晶体下铺地的重要性在于:

- 它可以作为射频电流的辐射耦合路径,减少射频辐射。

- 提供一个映像平面,降低共模电流,从而降低射频辐射。

- 地平面还能吸收差模射频电流,确保低阻抗连接,增强整个系统的抗干扰能力。

对于时钟布线,需要注意以下几点:

1. 快速上升沿的时钟信号应采用辐射状拓扑结构,避免单个公共驱动源的串联,以减少信号质量损失。每个走线应根据特性阻抗进行端接。

2. 时钟走线应尽可能短,并且在其附近安排完整的映像平面层,以控制阻抗,减少信号失真。

3. 避免错误的跨层走线和阻抗不匹配,这可能导致映像回路的不完整,电压浪涌,以及由于信号变化引起的地平面噪声。

正确的PCB分层对于时钟传输线至关重要,以减少信号的衰减和反射,确保信号的完整传输。设计时应特别关注过孔和跳转的影响,因为它们可能破坏地平面的连续性,增加噪声和信号质量下降。

时钟信号设计是一个复杂的过程,涉及到布局、布线、屏蔽和阻抗匹配等多个方面。理解并遵循这些原则,可以有效提高系统性能,降低噪声,防止射频辐射,确保电路的稳定运行。对于新手来说,掌握这些基本规则是成功设计的关键步骤。"

2022-09-24 上传

2019-08-25 上传

2020-08-30 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

OpenFPGA

- 粉丝: 8660

- 资源: 55

最新资源

- 探索AVL树算法:以Faculdade Senac Porto Alegre实践为例

- 小学语文教学新工具:创新黑板设计解析

- Minecraft服务器管理新插件ServerForms发布

- MATLAB基因网络模型代码实现及开源分享

- 全方位技术项目源码合集:***报名系统

- Phalcon框架实战案例分析

- MATLAB与Python结合实现短期电力负荷预测的DAT300项目解析

- 市场营销教学专用查询装置设计方案

- 随身WiFi高通210 MS8909设备的Root引导文件破解攻略

- 实现服务器端级联:modella与leveldb适配器的应用

- Oracle Linux安装必备依赖包清单与步骤

- Shyer项目:寻找喜欢的聊天伙伴

- MEAN堆栈入门项目: postings-app

- 在线WPS办公功能全接触及应用示例

- 新型带储订盒订书机设计文档

- VB多媒体教学演示系统源代码及技术项目资源大全