基于CPLD与51单片机的高精度数字频率计设计

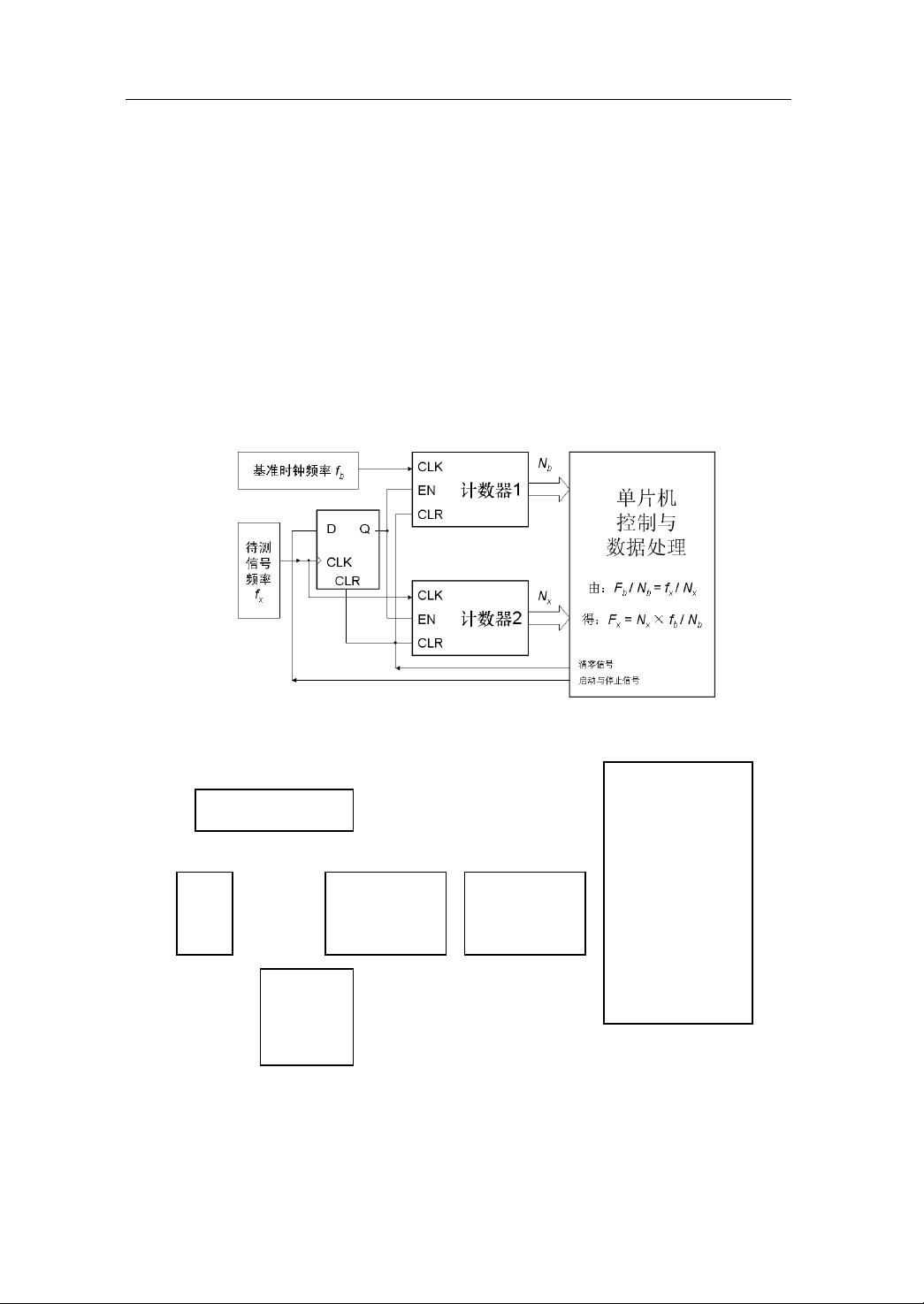

本文主要探讨了基于单片机(如51系列)和复杂可编程逻辑器件(CPLD,如ATF1504)的等精度数字频率计的设计。作者在物理与电子科学学院完成的这项研究,着重于解决现代信号分析与处理领域对高精度频率测量的需求。设计的核心思想是将CPLD用于复杂的计数和逻辑功能,而51单片机则负责数据处理和系统控制,确保测量结果的精确性。

首先,文章在前言部分阐述了设计的背景和目的,强调了高精度频率测量在实际应用中的重要性。接着,第二章深入解析了等精度频率测量的基本原理,包括如何通过同步采样和处理来消除误差,以及可能影响精度的因素。

第三章详细描述了系统设计方案。作者首先比较了几种可能的解决方案,并最终选择了结合单片机和CPLD的方案。单片机与CPLD的连接方案是设计的关键环节,涉及接口设计和通信协议的选择。单片机负责设定时任务,比如通过定时器进行周期性采样,同时处理数据并控制整个系统的工作流程。CPLD则承担着计数和复杂的逻辑运算,确保每个测量周期的准确计数。

在第四章,作者具体介绍了CPLD和单片机的设计实现。CPLD部分着重于ATF1504的功能配置和编程,确保能够高效执行计数任务。单片机设计方面,展示了如何利用其丰富的寄存器和指令集进行精确的数据处理。此外,关键源代码分析部分揭示了设计中的核心算法和技术细节。

第五章是设计的验证阶段,通过仿真分析来评估系统的性能,包括频率响应、稳定性等方面。测试结果与分析部分展示了实际应用中的测量精度,以及如何根据测试数据优化系统设计。

最后,文章以致谢和参考文献结束,致谢部分感谢了指导教师和其他相关人员的帮助,而参考文献则列出了设计过程中参考的相关学术资料和技术文档。

本文提供了一个实用且理论结合实践的设计案例,展示了如何通过单片机和CPLD的协同工作,实现高精度的数字频率计,对于从事信号处理和电子工程的学生和工程师具有很高的参考价值。

2023-07-08 上传

2010-12-18 上传

2023-07-06 上传

2020-10-24 上传

2020-10-25 上传

2023-07-09 上传

2023-07-01 上传

姜宽

- 粉丝: 0

- 资源: 4

最新资源

- 程序靠边自动隐藏窗口-易语言

- Pipo:用于从Firebase提取数据并显示的Android项目

- school_project

- flutter_google_ml_vision:适用于Google ML Kit Vision的Flutter插件

- codeandsewn.github.io

- CheckHealth.github.io

- 林森塔

- Happy-Holi

- Prog2_Reseau:Prog2 Java LP SIL的小型项目Vianey Benjamin-Bodet Cindy

- c# 锁屏系统

- hackgt21-whispermom:HackGT'21的临时仓库

- 网址:霓虹灯线

- Webpack_PW_Anul_2

- 能否上网-易语言

- nonogram:基于遗传算法的非图求解器

- 控制