没有合适的资源?快使用搜索试试~ 我知道了~

首页Apple MacBook Pro 13 A1278 (K24, 820-2530):图纸概述

Apple MacBook Pro 13 A1278 (K24, 820-2530):图纸概述

需积分: 5 1 下载量 160 浏览量

更新于2024-06-18

收藏 1.36MB PDF 举报

本文档是关于Apple Macbook Pro 13 A1278(型号K24,820-2530)的图纸资料。该文档包含了一系列电子元器件的技术规格和设计细节,旨在确保设备的精确制造和性能。以下是部分内容解析:

1. **频率与振荡器值**: 表格中的所有晶体和振荡器的频率值都以赫兹(Hz)为单位给出,这是电子设备中常见的频率单位,用于描述电路元件的工作速度。

2. **电阻值与功率**: 所有电阻值是以欧姆(Ω)表示,且精度为±5%,表明这些电阻在电路中的规格和容许误差范围。

3. **保密条款**: 文档强调了保密性和非公开性,禁止全文或部分透露,同时声明保留所有权利,要求接收者在持有和处理此图纸时保持机密,并不得进行复制。

4. **版权信息**: 文档标明为Apple Computer, Inc. 的专有财产,强调了知识产权的重要性。

5. **图纸详细信息**: 包括修订号、分支、绘图编号、修订版本、尺寸等,这些都是图纸管理中的关键元素,确保图纸的一致性和更新。

6. **元器件规格**: 提供了电容值,以微法拉德(μF)为单位,电容器的容量对电路的存储能力和响应特性至关重要。

7. **页码与目录**: 图表中可能包含一个详细的内容目录,列出各章节或表格的位置,方便查找特定信息。

8. **日期与版权声明**: 显示了图纸的创建或最近修订日期,以及版权和使用条件的通知。

9. **修订描述**: 可能包含了本次修订的目的、所做的更改以及可能的影响,这对于追踪产品的演变历史至关重要。

这份图纸是Apple Macbook Pro 13 A1278笔记本电脑内部电子组件设计的关键文档,它包含了工程师、制造商和维修人员在组装、测试和维护过程中所需的所有技术参数和规格。理解并遵循其中的规定对于确保产品的质量和保密性至关重要。

0A

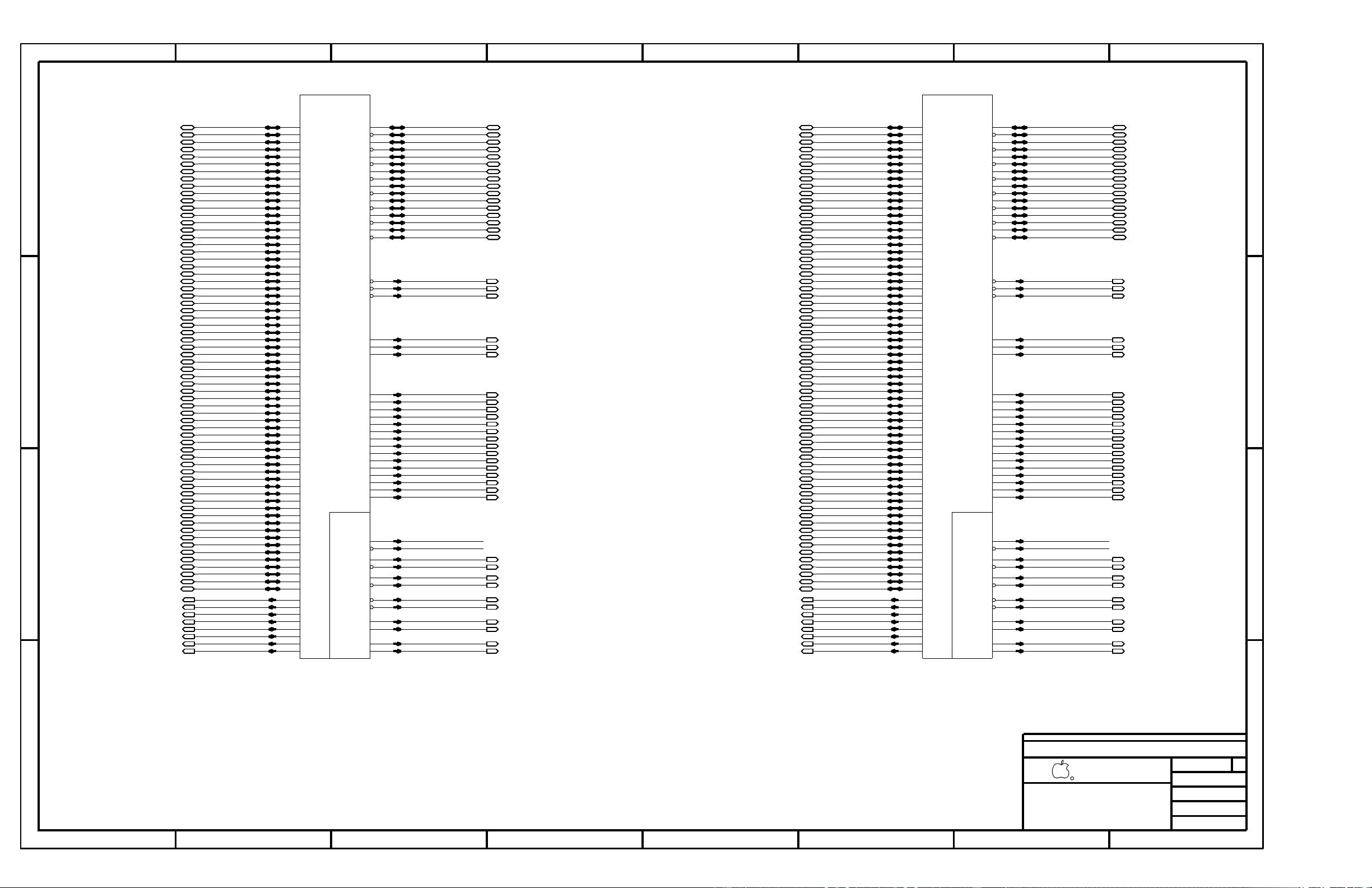

MEMORY

MEMORY PARTITION 0

CONTROL

MCKE0A_1

MCKE0A_0

MODT0A_1

MODT0A_0

MCS0A_0#

MCS0A_1#

MCLK0A_0_N

MCLK0A_0_P

MCLK0A_1_N

MCLK0A_2_N

MCLK0A_1_P

MCLK0A_2_P

MA0_0

MA0_1

MA0_2

MA0_3

MA0_4

MA0_5

MA0_6

MA0_8

MA0_7

MA0_9

MA0_10

MA0_11

MA0_13

MA0_12

MA0_14

MBA0_2

MBA0_0

MBA0_1

MWE0#

MCAS0#

MRAS0#

MDQS0_0_P

MDQS0_0_N

MDQS0_1_P

MDQS0_2_N

MDQS0_1_N

MDQS0_2_P

MDQS0_3_N

MDQS0_4_P

MDQS0_3_P

MDQS0_4_N

MDQS0_5_N

MDQS0_5_P

MDQS0_6_N

MDQS0_6_P

MDQS0_7_N

MDQS0_7_P

MDQM0_2

MDQM0_1

MDQM0_0

MDQM0_3

MDQM0_4

MDQ0_0

MDQM0_7

MDQM0_5

MDQM0_6

MDQ0_1

MDQ0_4

MDQ0_3

MDQ0_2

MDQ0_5

MDQ0_6

MDQ0_9

MDQ0_8

MDQ0_7

MDQ0_10

MDQ0_11

MDQ0_15

MDQ0_14

MDQ0_13

MDQ0_12

MDQ0_16

MDQ0_21

MDQ0_20

MDQ0_18

MDQ0_19

MDQ0_17

MDQ0_25

MDQ0_24

MDQ0_23

MDQ0_22

MDQ0_26

MDQ0_29

MDQ0_28

MDQ0_27

MDQ0_30

MDQ0_31

MDQ0_35

MDQ0_34

MDQ0_32

MDQ0_36

MDQ0_33

MDQ0_41

MDQ0_37

MDQ0_38

MDQ0_40

MDQ0_39

MDQ0_42

MDQ0_47

MDQ0_46

MDQ0_43

MDQ0_45

MDQ0_44

MDQ0_51

MDQ0_50

MDQ0_49

MDQ0_52

MDQ0_48

MDQ0_55

MDQ0_54

MDQ0_53

MDQ0_56

MDQ0_57

MDQ0_61

MDQ0_60

MDQ0_58

MDQ0_59

MDQ0_62

MDQ0_63

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

MEMORY

CONTROL

1A

MEMORY PARTITION 1

MDQ1_63

MDQ1_60

MDQ1_59

MDQ1_62

MDQ1_58

MDQ1_61

MDQ1_57

MDQ1_53

MDQ1_56

MDQ1_55

MDQ1_54

MDQ1_52

MDQ1_49

MDQ1_51

MDQ1_50

MDQ1_48

MDQ1_47

MDQ1_46

MDQ1_43

MDQ1_44

MDQ1_45

MDQ1_42

MDQ1_41

MDQ1_37

MDQ1_38

MDQ1_39

MDQ1_36

MDQ1_35

MDQ1_32

MDQ1_33

MDQ1_34

MDQ1_31

MDQ1_30

MDQ1_27

MDQ1_28

MDQ1_29

MDQ1_22

MDQ1_26

MDQ1_25

MDQ1_24

MDQ1_23

MDQ1_17

MDQ1_19

MDQ1_20

MDQ1_18

MDQ1_21

MDQ1_16

MDQ1_12

MDQ1_13

MDQ1_14

MDQ1_15

MDQ1_11

MDQ1_10

MDQ1_7

MDQ1_8

MDQ1_9

MDQ1_3

MDQ1_6

MDQ1_2

MDQ1_4

MDQ1_5

MDQ1_1

MDQM1_6

MDQM1_5

MDQ1_0

MDQM1_7

MDQM1_4

MDQM1_3

MDQM1_0

MDQM1_1

MDQM1_2

MDQ1_40

MDQS1_7_P

MDQS1_6_N

MDQS1_6_P

MDQS1_7_N

MDQS1_5_N

MDQS1_5_P

MDQS1_4_P

MDQS1_3_P

MDQS1_4_N

MDQS1_2_P

MDQS1_3_N

MDQS1_1_P

MDQS1_2_N

MDQS1_1_N

MDQS1_0_P

MDQS1_0_N

MRAS1#

MCAS1#

MWE1#

MBA1_2

MBA1_1

MBA1_0

MA1_14

MA1_13

MA1_12

MA1_11

MA1_10

MA1_9

MA1_8

MA1_7

MA1_6

MA1_5

MA1_4

MA1_3

MA1_2

MA1_1

MA1_0

MCLK1A_2_P

MCLK1A_1_P

MCLK1A_2_N

MCLK1A_0_P

MCLK1A_1_N

MCS1A_1#

MCS1A_0#

MCLK1A_0_N

MODT1A_1

MODT1A_0

MCKE1A_0

MCKE1A_1

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

BI

OUT

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

15 OF 109

051-7898

C.0.0

<CURRENT_DESIGN_SHEET> OF <TOTAL_DESIGN_SHEETS>

MEM_A_A<5>

MEM_A_DQS_P<7>

MEM_A_DQS_N<7>

MEM_A_DQS_P<6>

MEM_A_DQS_N<6>

MEM_A_DQS_P<5>

MEM_A_DQS_N<5>

MEM_A_DQS_P<4>

MEM_A_DQS_N<4>

MEM_A_DQS_P<3>

MEM_A_DQS_N<3>

MEM_A_DQS_P<2>

MEM_A_DQS_N<2>

MEM_A_DQS_P<1>

MEM_A_DQS_N<1>

MEM_A_DQS_P<0>

MEM_A_DQS_N<0>

MEM_A_RAS_L

MEM_A_CAS_L

MEM_A_WE_L

MEM_A_BA<2>

MEM_A_BA<1>

MEM_A_BA<0>

MEM_A_A<14>

MEM_A_A<13>

MEM_A_A<12>

MEM_A_A<11>

MEM_A_A<10>

MEM_A_A<9>

MEM_A_A<8>

MEM_A_A<7>

MEM_A_A<6>

MEM_A_A<4>

MEM_A_A<3>

MEM_A_A<2>

MEM_A_A<1>

MEM_A_A<0>

TP_MEM_A_CLK2P

TP_MEM_A_CLK2N

MEM_A_CLK_P<1>

MEM_A_CLK_N<1>

MEM_A_CLK_P<0>

MEM_A_CLK_N<0>

MEM_A_CS_L<1>

MEM_A_CS_L<0>

MEM_A_ODT<1>

MEM_A_ODT<0>

MEM_A_CKE<1>

MEM_A_CKE<0>

MEM_B_DQS_P<7>

MEM_B_DQS_N<7>

MEM_B_DQS_P<6>

MEM_B_DQS_N<6>

MEM_B_DQS_P<5>

MEM_B_DQS_N<5>

MEM_B_DQS_P<4>

MEM_B_DQS_N<4>

MEM_B_DQS_P<3>

MEM_B_DQS_N<3>

MEM_B_DQS_P<2>

MEM_B_DQS_N<2>

MEM_B_DQS_P<1>

MEM_B_DQS_N<1>

MEM_B_DQS_P<0>

MEM_B_DQS_N<0>

MEM_B_RAS_L

MEM_B_CAS_L

MEM_B_WE_L

MEM_B_BA<2>

MEM_B_BA<1>

MEM_B_BA<0>

MEM_B_A<14>

MEM_B_A<13>

MEM_B_A<12>

MEM_B_A<11>

MEM_B_A<10>

MEM_B_A<9>

MEM_B_A<8>

MEM_B_A<7>

MEM_B_A<6>

MEM_B_A<5>

MEM_B_A<4>

MEM_B_A<3>

MEM_B_A<2>

MEM_B_A<1>

MEM_B_A<0>

TP_MEM_B_CLK2P

TP_MEM_B_CLK2N

MEM_B_CLK_P<1>

MEM_B_CLK_N<1>

MEM_B_CLK_P<0>

MEM_B_CLK_N<0>

MEM_B_CS_L<1>

MEM_B_CS_L<0>

MEM_B_ODT<1>

MEM_B_ODT<0>

MEM_B_CKE<1>

MEM_B_CKE<0>

MEM_A_DQ<63>

MEM_A_DQ<62>

MEM_A_DQ<61>

MEM_A_DQ<60>

MEM_A_DQ<59>

MEM_A_DQ<58>

MEM_A_DQ<57>

MEM_A_DQ<56>

MEM_A_DQ<55>

MEM_A_DQ<54>

MEM_A_DQ<53>

MEM_A_DQ<52>

MEM_A_DQ<51>

MEM_A_DQ<50>

MEM_A_DQ<49>

MEM_A_DQ<48>

MEM_A_DQ<47>

MEM_A_DQ<46>

MEM_A_DQ<45>

MEM_A_DQ<44>

MEM_A_DQ<43>

MEM_A_DQ<42>

MEM_A_DQ<41>

MEM_A_DQ<40>

MEM_A_DQ<39>

MEM_A_DQ<38>

MEM_A_DQ<37>

MEM_A_DQ<36>

MEM_A_DQ<35>

MEM_A_DQ<34>

MEM_A_DQ<33>

MEM_A_DQ<32>

MEM_A_DQ<31>

MEM_A_DQ<30>

MEM_A_DQ<29>

MEM_A_DQ<28>

MEM_A_DQ<27>

MEM_A_DQ<26>

MEM_A_DQ<25>

MEM_A_DQ<24>

MEM_A_DQ<23>

MEM_A_DQ<22>

MEM_A_DQ<21>

MEM_A_DQ<20>

MEM_A_DQ<19>

MEM_A_DQ<18>

MEM_A_DQ<17>

MEM_A_DQ<16>

MEM_A_DQ<15>

MEM_A_DQ<14>

MEM_A_DQ<13>

MEM_A_DQ<12>

MEM_A_DQ<11>

MEM_A_DQ<10>

MEM_A_DQ<9>

MEM_A_DQ<8>

MEM_A_DQ<7>

MEM_A_DQ<6>

MEM_A_DQ<5>

MEM_A_DQ<4>

MEM_A_DQ<3>

MEM_A_DQ<2>

MEM_A_DQ<1>

MEM_A_DQ<0>

MEM_A_DM<7>

MEM_A_DM<6>

MEM_A_DM<5>

MEM_A_DM<4>

MEM_A_DM<3>

MEM_A_DM<2>

MEM_A_DM<1>

MEM_A_DM<0>

MEM_B_DQ<63>

MEM_B_DQ<62>

MEM_B_DQ<61>

MEM_B_DQ<60>

MEM_B_DQ<59>

MEM_B_DQ<58>

MEM_B_DQ<57>

MEM_B_DQ<56>

MEM_B_DQ<55>

MEM_B_DQ<54>

MEM_B_DQ<53>

MEM_B_DQ<52>

MEM_B_DQ<51>

MEM_B_DQ<50>

MEM_B_DQ<49>

MEM_B_DQ<48>

MEM_B_DQ<47>

MEM_B_DQ<46>

MEM_B_DQ<45>

MEM_B_DQ<44>

MEM_B_DQ<43>

MEM_B_DQ<42>

MEM_B_DQ<41>

MEM_B_DQ<40>

MEM_B_DQ<39>

MEM_B_DQ<38>

MEM_B_DQ<37>

MEM_B_DQ<36>

MEM_B_DQ<35>

MEM_B_DQ<34>

MEM_B_DQ<33>

MEM_B_DQ<32>

MEM_B_DQ<31>

MEM_B_DQ<30>

MEM_B_DQ<29>

MEM_B_DQ<28>

MEM_B_DQ<27>

MEM_B_DQ<26>

MEM_B_DQ<25>

MEM_B_DQ<24>

MEM_B_DQ<23>

MEM_B_DQ<22>

MEM_B_DQ<21>

MEM_B_DQ<20>

MEM_B_DQ<19>

MEM_B_DQ<18>

MEM_B_DQ<17>

MEM_B_DQ<16>

MEM_B_DQ<15>

MEM_B_DQ<14>

MEM_B_DQ<13>

MEM_B_DQ<12>

MEM_B_DQ<11>

MEM_B_DQ<10>

MEM_B_DQ<9>

MEM_B_DQ<8>

MEM_B_DQ<7>

MEM_B_DQ<6>

MEM_B_DQ<5>

MEM_B_DQ<4>

MEM_B_DQ<3>

MEM_B_DQ<2>

MEM_B_DQ<1>

MEM_B_DQ<0>

MEM_B_DM<7>

MEM_B_DM<6>

MEM_B_DM<5>

MEM_B_DM<4>

MEM_B_DM<3>

MEM_B_DM<2>

MEM_B_DM<1>

MEM_B_DM<0>

MCP Memory Interface

SYNC_DATE=04/04/2008

SYNC_MASTER=T18_MLB

27C4 74B3

27C2 74B3

27C2 74B3

27B4 74B3

27B5 74B3

27B7 74B3

27B5 74B3

27D4 74B3

27A7 74B3

27C2 74B3

27D4 74B3

27C4 74B3

27D2 74B3

27D2 74B3

27C4 74B3

27C2 74B3

27C2 74B3

27C4 74B3

27C2 74B3

27C2 74B3

27C2 74B3

27C4 74B3

27C4 74B3

27C4 74B3

27C2 74B3

27C4 74B3

27C2 74B3

27C4 74B3

27C4 74B3

27C2 74B3

27C4 74B3

27C2 74B3

27C2 74B3

27C4 74B3

27B4 74B3

27B2 74B3

27C4 74B3

27C2 74B3

27B2 74B3

27B4 74B3

27B5 74B3

27B7 74B3

27B5 74B3

27B7 74B3

27C5 74B3

27B5 74B3

27C7 74B3

27B7 74B3

27B5 74B3

27B7 74B3

27B5 74B3

27B5 74B3

27B5 74B3

27B7 74B3

27B7 74B3

BA16

AW16

BB13

AY15

AT2

AT1

AY2

AY1

BB6

BA6

BA10

AY11

BB33

BA33

BB37

BA37

BA43

AY42

AT42

AT43

AT5

BA2

AY7

BA11

BB34

BB38

AY43

AR42

AW42

AW41

AT40

AT4

AT3

AV2

AV3

AT41

AR4

AR3

AU2

AU3

AY4

AY3

BB3

BC3

AW4

AW3

AP41

BA3

BB2

BB5

BA5

BA8

BC8

BB4

BC4

BA7

AY8

AN40

BA9

BB10

BB12

AW12

BB8

BB9

AY12

BA12

BC32

AW32

AU40

BA35

AY36

BA32

BB32

BA34

AY35

BC36

AW36

BA39

AY40

AU41

BA36

BB36

BA38

AY39

BB40

AW40

AV42

AV41

BA40

BC40

AR41

AP42

BB14

BB16

BA42

BB42

BB22

BA22

BA19

AY19

AY31

BB30

BA15

BB29

BB18

BB17

BB28

AY28

BA28

AY27

BA27

BA26

BB26

BA25

BA29

BA14

AW28

BC28

BA17

BB25

BA18

U1400

(3 OF 11)

OMIT

MCP79-TOPO-B

BGA

27D7 74B3

27D5 74B3

27C5 74B3

27C5 74B3

27C5 74B3

27C7 74B3

27C7 74C3

27C7 74C3

27C5 74C3

27C5 74C3

27C5 74B3

27C7 74B3

27C5 74B3

27C7 74B3

27C5 74B3

27C7 74B3

27C5 74B3

27C5 74B3

27C7 74B3

27C7 74B3

27C7 74B3

27C5 74B3

27C7 74B3

27C7 74B3

27C5 74B3

27C7 74B3

27C5 74B3

27C7 74B3

27C7 74B3

27C7 74B3

27C5 74B3

27B5 74B3

27B7 74B3

27B7 74B3

27B5 74B3

27B5 74B3

27B5 74B3

27B7 74B3

27B7 74B3

27B7 74B3

27B7 74B3

27A5 74B3

27A7 74B3

27B5 74B3

27A7 74B3

27A7 74B3

27A5 74B3

27B5 74B3

27D2 74A3

27C2 74A3

27C4 74A3

27C4 74A3

27C4 74A3

27C4 74A3

27C2 74A3

27B7 74A3

27B2 74A3

27B7 74A3

27B5 74A3

27B5 74A3

27B7 74A3

27B7 74A3

27A5 74A3

27A5 74A3

26C2 74C3

26D2 74C3

26C4 74C3

26C4 74C3

26B2 74C3

26C2 74C3

26C4 74C3

26C4 74C3

26B7 74C3

26B7 74C3

26B5 74C3

26B5 74C3

26B7 74C3

26B7 74C3

26A5 74C3

26A5 74C3

26D7 74D3

26D5 74D3

26C5 74D3

26C5 74D3

26C5 74D3

26C7 74D3

26C7 74D3

26C7 74D3

26C5 74D3

26C5 74D3

26C7 74D3

26C7 74D3

26C5 74D3

26C7 74D3

26C7 74D3

26C5 74D3

26C5 74D3

26C5 74D3

26C7 74D3

26C7 74D3

26C5 74D3

26C7 74D3

26C5 74D3

26C7 74D3

26C5 74D3

26C7 74D3

26C5 74D3

26C7 74D3

26C7 74D3

26C7 74D3

26C5 74D3

26D4 74D3

26C2 74D3

26C2 74D3

26D2 74D3

26D2 74D3

26C4 74D3

26C4 74D3

26C4 74D3

26C2 74D3

26C4 74D3

26C2 74D3

26C4 74D3

26C2 74D3

26C2 74D3

26C4 74D3

26B4 74D3

26C2 74D3

26C2 74D3

26B2 74D3

26C4 74D3

26C4 74D3

26B2 74D3

26B4 74D3

26C4 74D3

26C4 74D3

26C4 74D3

26C2 74D3

26C2 74D3

26C2 74D3

26C4 74D3

26C2 74D3

26C7 74D3

26B7 74D3

26B7 74D3

26B5 74D3

26B5 74D3

26C5 74D3

26B7 74D3

26B5 74D3

26B5 74D3

26B5 74D3

26B5 74D3

26B5 74D3

26B7 74D3

26B7 74D3

26B7 74D3

26B7 74D3

26B5 74D3

26B7 74D3

26B5 74D3

26B7 74D3

26B7 74D3

26B5 74D3

26B7 74D3

26B5 74D3

26B5 74D3

26B5 74D3

26A7 74D3

26A7 74D3

26A7 74D3

26B7 74D3

26A5 74D3

26A5 74D3

26D4 74D3

26C4 74D3

26C2 74C3

26B4 74C3

26C2 74C3

26B5 74C3

26B7 74C3

26A7 74C3

26B5 74C3

AR17

AV17

AP15

AV15

AL10

AL11

AR8

AR9

AW7

AW8

AP13

AR13

AV25

AW25

AU30

AU29

AT35

AU35

AU39

AT39

AN5

AU5

AR10

AN13

AN27

AW29

AV35

AR34

AT37

AU37

AW39

AL8

AL9

AP9

AN9

AV39

AL6

AL7

AN6

AN7

AR6

AR7

AV6

AW5

AN10

AR5

AR37

AU6

AV5

AU7

AU8

AW9

AP11

AW6

AY5

AU9

AV9

AR38

AU11

AV11

AV13

AW13

AR11

AT11

AR14

AU13

AR26

AU25

AV38

AT27

AU27

AP25

AR25

AP27

AR27

AP29

AR29

AP31

AR31

AW38

AV27

AN29

AV29

AN31

AU31

AR33

AV37

AW37

AT31

AV31

AR35

AP35

AT15

AR18

AW33

AV33

BA24

AY24

BB20

BC20

AU23

AT23

AP17

AP23

AP19

AW17

AV21

AR22

AU21

AP21

AR21

AN21

AV19

AU19

AR23

AU15

AN23

AW21

AN19

AT19

AR19

U1400

(2 OF 11)

OMIT

MCP79-TOPO-B

BGA

MCLK1B_2_P

MCLK1B_1_N

MCLK1B_0_P

MCLK1B_1_P

MCLK1B_2_N

MCS1B_1#

MCS1B_0#

MCLK1B_0_N

MODT1B_0

MCKE1B_1

MCKE1B_0

MODT1B_1

MRESET0#

GND55

GND56

GND57

GND58

GND60

GND59

GND61

GND62

GND63

GND64

GND52

GND53

GND54

GND51

GND49

GND50

GND48

GND47

GND46

GND44

GND45

GND43

GND42

GND41

GND39

GND40

GND38

GND37

GND36

GND35

GND33

GND34

GND32

GND31

GND30

GND28

GND29

GND27

GND26

GND25

GND24

GND18

GND19

GND17

GND16

GND15

GND13

GND14

GND10

GND12

GND11

GND8

GND9

GND7

GND6

GND5

GND2

GND3

GND4

GND1

MEM_COMP_VDD

MEM_COMP_GND

MODT0B_0

MODT0B_1

MCKE0B_1

MCKE0B_0

MCLK0B_0_N

MCS0B_0#

MCS0B_1#

MCLK0B_2_N

MCLK0B_1_P

MCLK0B_0_P

MCLK0B_1_N

MCLK0B_2_P

+V_PLL_XREF_XS

+V_PLL_CORE

+V_VPLL

+VDD_MEM1

+VDD_MEM2

+VDD_MEM3

+VDD_MEM4

+VDD_MEM5

+VDD_MEM6

+VDD_MEM7

+VDD_MEM8

+VDD_MEM9

+VDD_MEM10

+VDD_MEM11

+VDD_MEM14

+VDD_MEM15

+VDD_MEM16

+VDD_MEM17

+VDD_MEM18

+VDD_MEM19

+VDD_MEM20

+VDD_MEM22

+VDD_MEM21

+VDD_MEM23

+VDD_MEM24

+VDD_MEM25

+VDD_MEM26

+VDD_MEM30

+VDD_MEM27

+VDD_MEM29

+VDD_MEM31

+VDD_MEM32

+VDD_MEM33

+VDD_MEM34

+VDD_MEM38

+VDD_MEM39

+VDD_MEM40

+VDD_MEM41

+VDD_MEM43

+VDD_MEM44

+VDD_MEM45

+VDD_MEM42

+V_PLL_DP

+VDD_MEM13

+VDD_MEM12

+VDD_MEM28

+VDD_MEM37

+VDD_MEM36

+VDD_MEM35

GND21

GND20

GND22

GND23

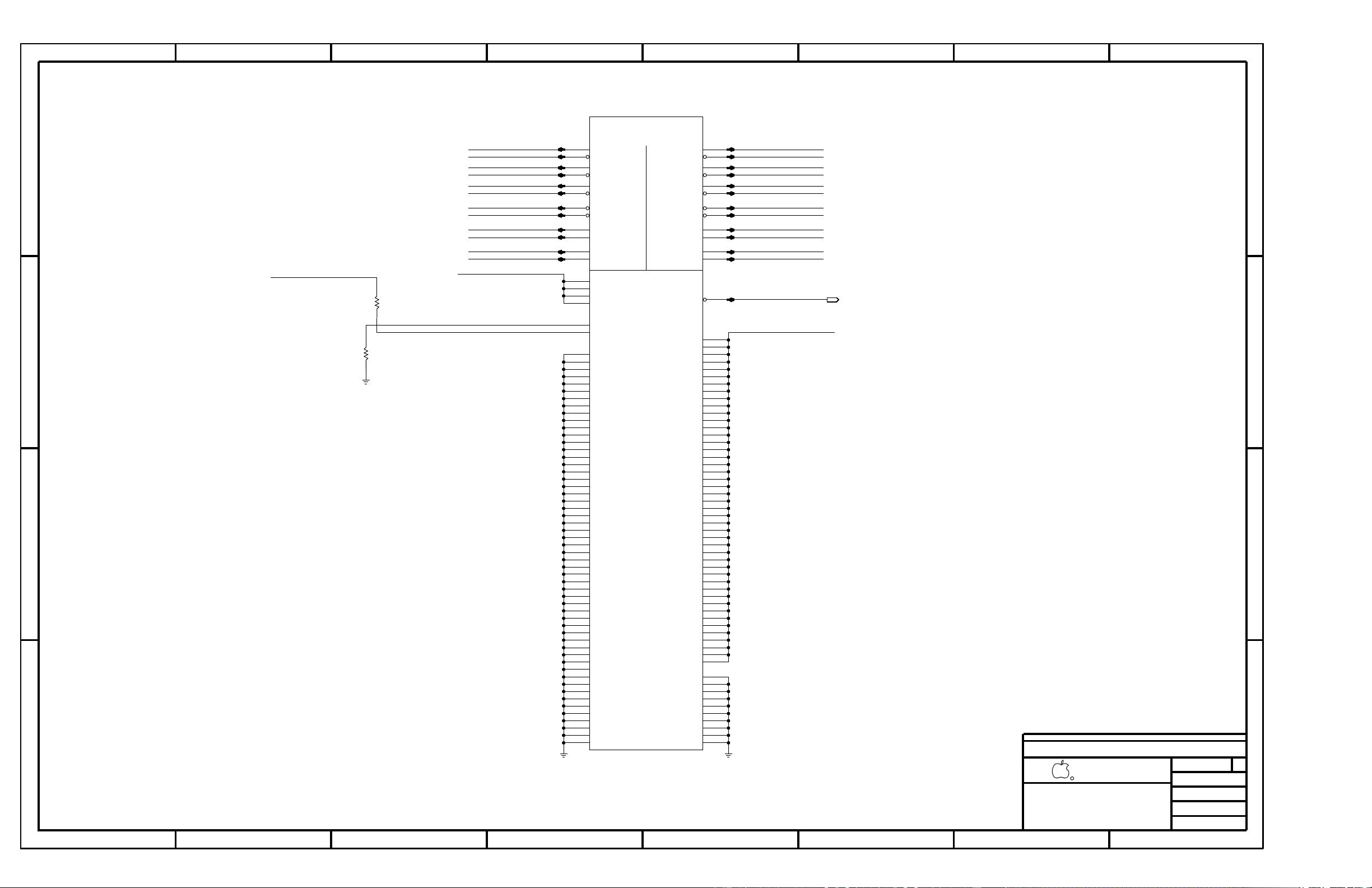

MEMORY CONTROL 0B

MEMORY CONTROL 1B

OUT

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

4771 mA (A01, DDR3)

17 mA

12 mA

Current numbers from email Poonacha Kongetira provided 11/30/2007 4:04pm (no official document number).

19 mA

TP or NC for DDR2.

39 mA

87 mA (A01)

16 OF 109

051-7898

C.0.0

<CURRENT_DESIGN_SHEET> OF <TOTAL_DESIGN_SHEETS>

MCP_MEM_COMP_VDD

=PP1V8R1V5_S0_MCP_MEM

TP_MEM_B_ODT<3>

TP_MEM_B_ODT<2>

TP_MEM_B_CS_L<3>

TP_MEM_B_CLK3N

TP_MEM_B_CLK3P

TP_MEM_B_CLK4N

TP_MEM_B_CLK4P

TP_MEM_B_CLK5N

TP_MEM_B_CLK5P

PP1V05_S0_MCP_PLL_CORE

TP_MEM_A_CS_L<3>

TP_MEM_A_CS_L<2>

TP_MEM_A_CLK3N

TP_MEM_A_CLK4P

TP_MEM_A_CLK5N

TP_MEM_A_CLK5P

TP_MEM_A_CKE<3>

TP_MEM_A_CKE<2>

TP_MEM_A_ODT<3>

TP_MEM_A_ODT<2>

TP_MEM_A_CLK3P

TP_MEM_A_CLK4N

MCP_MEM_COMP_GND

=PP1V8R1V5_S0_MCP_MEM

MCP_MEM_RESET_L

TP_MEM_B_CS_L<2>

TP_MEM_B_CKE<2>

TP_MEM_B_CKE<3>

SYNC_MASTER=T18_MLB

SYNC_DATE=04/04/2008

MCP Memory Misc

28C6

BC29

AN16

AM29

AM27

AM25

AM31

AL30

BC25

AW24

AW19

AY26

AM23

AY25

AU18

AM15

AY18

AY17

AV20

BC17

AW27

AU22

AU20

AM21

AV24

AY29

AT21

AU24

AN18

AU16

AP18

AP22

AW15

AR24

AM19

AR20

AR16

AV16

AP24

AP20

AN22

AP16

AT17

AN24

AN20

AM17

T28

T27

U28

U27

AY32

BC13

AY16

AN15

AN17

AN41

AM41

BA13

BC16

AR15

AU17

BA41

BB41

AY23

BA23

BA20

AY20

AU33

AU34

BB24

BC24

BA21

BB21

BA31

BA30

AN25

AV23

W5

V34

V10

U22

U20

U18

T9

T7

T6

T38

T37

T35

T34

T33

T26

T24

AK11

T20

T18

T10

R5

R43

R40

R36

P7

P40

P4

P37

P34

P33

P10

N8

N39

M9

M7

M6

M5

M38

K7

H31

G32

G30

F24

D34

BC9

AY9

BC21

F28

AU10

AR36

AP30

AT25

AP12

AM28

AK7

AH35

AG24

AF24

AE20

AD22

AB7

AB22

AA39

AA22

U1400

BGA

OMIT

MCP79-TOPO-B

(4 OF 11)

2

1

R1611

40.2

1/16W

1%

402

MF-LF

2

1

R1610

MF-LF

402

1/16W

40.2

1%

74A3

7B6 15C3 22C8

22B2

74A3

7B6 15C7 22C8

PE0_RX0_P

PE0_RX2_N

+AVDD0_PEX11

+AVDD0_PEX7

+AVDD0_PEX8

+AVDD1_PEX3

+AVDD1_PEX2

+AVDD1_PEX1

+AVDD0_PEX13

+AVDD0_PEX12

+AVDD0_PEX10

+AVDD0_PEX9

+AVDD0_PEX6

+AVDD0_PEX5

+AVDD0_PEX4

+AVDD0_PEX3

+AVDD0_PEX2

+AVDD0_PEX1

+V_PLL_PEX

+DVDD1_PEX2

+DVDD1_PEX1

+DVDD0_PEX8

+DVDD0_PEX7

+DVDD0_PEX6

+DVDD0_PEX5

+DVDD0_PEX4

+DVDD0_PEX3

+DVDD0_PEX2

+DVDD0_PEX1

PE0_RX0_N

PE0_RX2_P

PE0_RX4_P

PE0_RX6_P

PEB_PRSNT#

PE1_TX3_N

PE1_TX3_P

PE1_TX2_N

PE1_TX1_N

PE1_TX2_P

PE1_TX0_N

PE1_TX1_P

PE6_REFCLK_N

PEX_RST0#

PE1_TX0_P

PE5_REFCLK_N

PE5_REFCLK_P

PE6_REFCLK_P

PE4_REFCLK_N

PE4_REFCLK_P

PE3_REFCLK_N

PE2_REFCLK_N

PE1_REFCLK_N

PE2_REFCLK_P

PE0_REFCLK_N

PE0_REFCLK_P

PE1_REFCLK_P

PE0_TX15_N

PE0_TX14_N

PE0_TX15_P

PE0_TX13_N

PE0_TX14_P

PE0_TX12_N

PE0_TX12_P

PE0_TX13_P

PE0_TX11_N

PE0_TX11_P

PE0_TX10_N

PE0_TX9_N

PE0_TX10_P

PE0_TX8_N

PE0_TX8_P

PE0_TX9_P

PE0_TX7_N

PE0_TX7_P

PE0_TX6_N

PE0_TX5_N

PE0_TX6_P

PE0_TX4_N

PE0_TX5_P

PE0_TX3_N

PE0_TX3_P

PE0_TX4_P

PE0_TX2_N

PE0_TX2_P

PE0_TX0_N

PE0_TX1_N

PE0_TX1_P

PE0_TX0_P

PEX_CLK_COMP

PE1_RX3_N

PE1_RX3_P

PE1_RX2_N

PE1_RX0_N

PE1_RX1_P

PE1_RX2_P

PE1_RX1_N

PE_WAKE#

PE1_RX0_P

PE0_PRSNT_16#

PE0_RX13_N

PE0_RX14_P

PE0_RX15_P

PE0_RX14_N

PE0_RX15_N

PE0_RX12_P

PE0_RX11_P

PE0_RX13_P

PE0_RX11_N

PE0_RX12_N

PE0_RX10_N

PE0_RX8_P

PE0_RX9_P

PE0_RX10_P

PE0_RX8_N

PE0_RX9_N

PE0_RX5_N

PE0_RX7_P

PE0_RX6_N

PE0_RX7_N

PE0_RX3_P

PE0_RX5_P

PE0_RX3_N

PE0_RX4_N

PE0_RX1_P

PE0_RX1_N

PEC_PRSNT#

PEC_CLKREQ#/GPIO_50

PE3_REFCLK_P

PED_CLKREQ#/GPIO_51

PED_PRSNT#

PEB_CLKREQ#/GPIO_49

PEE_CLKREQ#/GPIO_16

PEE_PRSNT#/GPIO_46

PEF_CLKREQ#/GPIO_17

PEF_PRSNT#/GPIO_47

PEG_CLKREQ#/GPIO_18

PEG_PRSNT#/GPIO_48

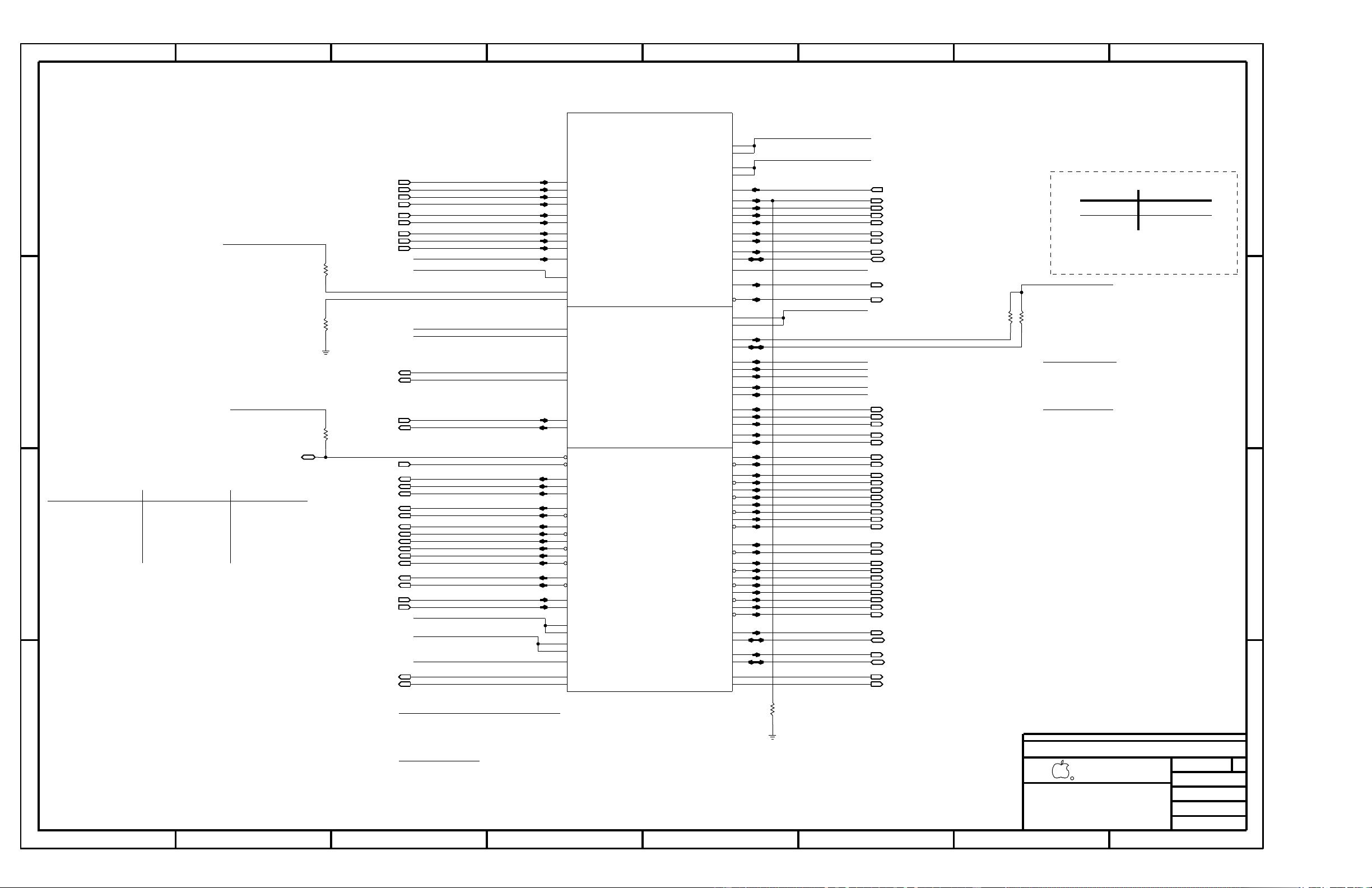

PCI EXPRESS

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

IN

OUT

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

Int PU (S5)

If PE1 interface is not used, ground DVDD1_PEX and AVDD1_PEX.

If PE0 interface is not used, ground DVDD0_PEX and AVDD0_PEX.

206 mA (A01, AVDD0 & 1)

Int PU

84 mA (A01)

Int PU

Int PU

Int PU

Int PU

Int PU

Int PU

Int PU

Int PU

Int PU

Int PU

Int PU

Int PU

57 mA (A01, DVDD0 & 1)

Current numbers from email Poonacha Kongetira provided 11/30/2007 4:04pm (no official document number).

17 OF 109

051-7898

C.0.0

<CURRENT_DESIGN_SHEET> OF <TOTAL_DESIGN_SHEETS>

=PEG_R2D_C_P<11>

=PEG_R2D_C_N<11>

=PEG_R2D_C_N<9>

=PEG_R2D_C_P<8>

=PEG_R2D_C_P<13>

PCIE_EXCARD_PRSNT_L

MINI_CLKREQ_L

=PP1V05_S0_MCP_PEX_AVDD1

=PP1V05_S0_MCP_PEX_AVDD0

=PP1V05_S0_MCP_PEX_DVDD1

=PEG_D2R_P<0>

=PEG_D2R_N<2>

PP1V05_S0_MCP_PLL_PEX

=PEG_D2R_N<0>

=PEG_D2R_P<2>

=PEG_D2R_P<4>

=PEG_D2R_P<6>

TP_PCIE_PE4_R2D_CN

TP_PCIE_PE4_R2D_CP

PCIE_EXCARD_R2D_C_N

PCIE_FW_R2D_C_N

PCIE_EXCARD_R2D_C_P

PCIE_MINI_R2D_C_N

PCIE_FW_R2D_C_P

TP_PCIE_CLK100M_PE6N

PCIE_RESET_L

PCIE_MINI_R2D_C_P

TP_PCIE_CLK100M_PE5N

TP_PCIE_CLK100M_PE5P

TP_PCIE_CLK100M_PE6P

TP_PCIE_CLK100M_PE4N

TP_PCIE_CLK100M_PE4P

PCIE_CLK100M_EXCARD_N

PCIE_CLK100M_FW_N

PCIE_CLK100M_MINI_N

PCIE_CLK100M_FW_P

PEG_CLK100M_N

PEG_CLK100M_P

PCIE_CLK100M_MINI_P

=PEG_R2D_C_N<15>

=PEG_R2D_C_N<14>

=PEG_R2D_C_P<15>

=PEG_R2D_C_N<13>

=PEG_R2D_C_P<14>

=PEG_R2D_C_N<12>

=PEG_R2D_C_P<12>

=PEG_R2D_C_N<10>

=PEG_R2D_C_P<10>

=PEG_R2D_C_N<8>

=PEG_R2D_C_P<9>

=PEG_R2D_C_N<7>

=PEG_R2D_C_P<7>

=PEG_R2D_C_N<6>

=PEG_R2D_C_N<5>

=PEG_R2D_C_P<6>

=PEG_R2D_C_N<4>

=PEG_R2D_C_P<5>

=PEG_R2D_C_N<3>

=PEG_R2D_C_P<3>

=PEG_R2D_C_P<4>

=PEG_R2D_C_N<2>

=PEG_R2D_C_P<2>

=PEG_R2D_C_N<0>

=PEG_R2D_C_N<1>

=PEG_R2D_C_P<1>

=PEG_R2D_C_P<0>

MCP_PEX_CLK_COMP

PEG_PRSNT_L

=PEG_D2R_N<13>

=PEG_D2R_P<14>

=PEG_D2R_P<15>

=PEG_D2R_N<14>

=PEG_D2R_N<15>

=PEG_D2R_P<12>

=PEG_D2R_P<11>

=PEG_D2R_P<13>

=PEG_D2R_N<11>

=PEG_D2R_N<12>

=PEG_D2R_N<10>

=PEG_D2R_P<8>

=PEG_D2R_P<9>

=PEG_D2R_P<10>

=PEG_D2R_N<8>

=PEG_D2R_N<9>

=PEG_D2R_N<5>

=PEG_D2R_P<7>

=PEG_D2R_N<6>

=PEG_D2R_N<7>

=PEG_D2R_P<3>

=PEG_D2R_P<5>

=PEG_D2R_N<3>

=PEG_D2R_N<4>

=PEG_D2R_P<1>

=PEG_D2R_N<1>

PCIE_CLK100M_EXCARD_P

EXCARD_CLKREQ_L

AUD_IP_PERIPHERAL_DET

GMUX_JTAG_TCK_L

=PP1V05_S0_MCP_PEX_DVDD0

PCIE_EXCARD_D2R_N

PCIE_EXCARD_D2R_P

TP_PCIE_PE4_D2RN

TP_PCIE_PE4_D2RP

PCIE_FW_D2R_N

PCIE_FW_D2R_P

PCIE_MINI_D2R_N

PCIE_MINI_D2R_P

PCIE_WAKE_L

GMUX_JTAG_TDO

CARDREADER_RESET

PCIE_FW_PRSNT_L

TP_PE4_PRSNT_L

TP_PE4_CLKREQ_L

FW_CLKREQ_L

PCIE_MINI_PRSNT_L

SYNC_DATE=04/04/2008

MCP PCIe Interfaces

SYNC_MASTER=T18_MLB

30B7

8C4

8C4

24C4

2

1

R1710

PLACEMENT_NOTE=Place within 12.7mm of U1400

NO STUFF

1/16W

1%

MF-LF

402

2.37K

8D6

8D6

8D6

29C5 75D3

29C5 75D3

8C6

8D6

34C2

34C2

34C1 75D3

34C1 75D3

29C5 75D3

29C5 75D3

8D6

8D6

29D7

29D7

8D6

8D6

34C1 75D3

34C1 75D3

6D5 29C7

35D3

8C6 35D3

6D5 29C7 75D3

6D5 29C7 75D3

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

8D6

K11

A11

M19

M17

M18

M16

L16

B10

M15

C10

E8

D9

D5

F17

N14

M14

L14

K14

J13

H13

G13

F13

J11

J10

B6

C6

A7

B7

B8

A8

D8

C8

H7

G7

F9

E9

H9

G9

K9

J9

G11

F11

H3

H2

G3

H4

F3

F4

E2

F2

D2

E1

C1

D1

B3

B2

A4

A3

C4

B4

M2

M1

M4

M3

L4

L3

K2

K3

J2

J3

H1

J1

C5

D4

L11

L10

J5

J4

J7

J6

G5

H5

C3

D3

E4

E3

E5

F5

E6

F6

D7

C7

N5

N4

N7

N6

N9

P9

N11

N10

L7

L6

L9

L8

F7

E7

E11

D11

C9

T16

U19

T19

U16

W18

W17

W16

V19

U17

W19

T17

P13

N13

M13

U12

T12

R12

P12

M12

AB12

AA12

W12

V12

AD12

AC12

Y12

U1400

BGA

OMIT

(5 OF 11)

MCP79-TOPO-B

N12

L18

7A6

7A6

7A6

22C2

75C3

57A4

7A6

IN

BI

OUT

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

OUT

IN

IN

IN

GPIO_7/NFERR*/IGPU_GPIO_7

+V_DUAL_MACPLL

+VDD_HDMI

+V_PLL_HDMI

+V_PLL_IFPAB

+VDD_IFPB

+VDD_IFPA

+V_TV_DAC

+V_RGB_DAC

+V_DUAL_RMGT2

MII_COMP_GND

MII_COMP_VDD

LCD_PANEL_PWR/GPIO_58

LCD_BKL_ON/GPIO_59

LCD_BKL_CTL/GPIO_57

XTALOUT_TV

GPIO_6/FERR*/IGPU_GPIO_6

HDMI_TXC_P/ML0_LANE3_P

HDMI_TXC_N/ML0_LANE3_N

HDMI_TXD0_P/ML0_LANE2_P

HDMI_TXD0_N/ML0_LANE2_N

HDMI_TXD1_P/ML0_LANE1_P

HDMI_TXD1_N/ML0_LANE1_N

HDMI_TXD2_P/ML0_LANE0_P

HDMI_TXD2_N/ML0_LANE0_N

HPLUG_DET2/GPIO_22

IFPA_TXC_N

XTALIN_TV

DDC_DATA2/GPIO_24

DDC_CLK2/GPIO_23

RGB_DAC_RSET

RGB_DAC_VREF

TV_DAC_VREF

DP_AUX_CH0_P

DP_AUX_CH0_N

HPLUG_DET3

HDMI_RSET

HDMI_VPROBE

RGMII_MDIO

BUF_25MHZ

DDC_DATA0

DDC_CLK0

RGB_DAC_RED

RGB_DAC_GREEN

RGB_DAC_BLUE

RGB_DAC_HSYNC

RGB_DAC_VSYNC

TV_DAC_RED

TV_DAC_GREEN

IFPA_TXC_P

IFPA_TXD0_P

IFPA_TXD0_N

IFPA_TXD2_P

IFPA_TXD1_P

IFPA_TXD1_N

IFPA_TXD3_P

IFPA_TXD2_N

IFPB_TXC_P

IFPB_TXC_N

IFPB_TXD5_P

IFPB_TXD4_P

IFPB_TXD4_N

IFPB_TXD6_P

IFPB_TXD5_N

IFPB_TXD6_N

IFPB_TXD7_P

IFPB_TXD7_N

DDC_DATA3

DDC_CLK3

IFPAB_RSET

IFPAB_VPROBE

TV_DAC_RSET

RGMII_RXD0

RGMII_INTR/GPIO_35

RGMII_RXD3

RGMII_RXCTL/MII_RXDV

RGMII_RXC/MII_RXCLK

RGMII_RXD2

RGMII_RXD1

MII_RESET#

RGMII_MDC

RGMII_PWRDWN/GPIO_37

MII_RXER/GPIO_36

MII_COL/GPIO_20/MSMB_DATA

MII_CRS/GPIO_21/MSMB_CLK

TV_DAC_BLUE

TV_DAC_HSYNC/GPIO_44

TV_DAC_VSYNC/GPIO_45

+V_DUAL_RMGT1

MII_VREF

RGMII_TXCTL/MII_TXEN

RGMII_TXC/MII_TXCLK

RGMII_TXD3

RGMII_TXD2

RGMII_TXD1

RGMII_TXD0

+3.3V_DUAL_RMGT1

+3.3V_DUAL_RMGT2

IFPA_TXD3_N

LAN

DACS

FLAT PANEL

BI

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

BI

OUT

BI

OUT

OUT

OUT

OUT

OUT

OUT

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

THE INFORMATION CONTAINED HEREIN IS THE

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PROPRIETARY PROPERTY OF APPLE COMPUTER, INC.

Apple Inc.

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

In MCP79 these pins have undocumented internal

GPIOs 57-59 (if LCD panel is used):

by default, pull-downs (1K or stronger) must be used.

pull-ups (~10K to 3.3V S0). To ensure pins are low

Alias to GMUX_INT for systems with GMUX.

Alias to HPLUG_DET2 for other systems.

Pull-down (20k) required in all cases.

=DVI_HPD_GMUX_INT:

Alias to DVI_HPD for systems using IFP for DVI.

(See below)

(See below)

NOTE: 1K pull-down required on DP_IG_AUX_CH_N if DP is used.

NOTE: 20K pull-down required on DP_HPD_DET.

level-shifters.

NOTE: HDMI port requires level-shifting. IFP interface can

be used to provide HDMI or dual-channel TMDS without

Interface Mode

DP_IG_ML_P/N<0>

DP_IG_DDC_DATA

DP_IG_HPD

DP_IG_AUX_CH_P/N

NOTE: 1M pull-down required on DP_IG_CA_DET if DP not used.

Dual-channel TMDS: Power +VDD_IFPx at 3.3V

131 mA (A01)

83 mA (A01)

MII, RGMII products will enable

WF: IFP is capable of LVDS (1.8V) or TMDS (3.3V), need aliases

RGB DAC Disable:

TV / Component

Current numbers from email Poonacha Kongetira provided 11/30/2007 4:04pm (no official document number).

LVDS: Power +VDD_IFPx at 1.8V

95 mA (A01)

16 mA (A01)

8 mA

8 mA

DP_IG_AUX_CH_P/N

=MCP_HDMI_HPD

TMDS_IG_HPD

=MCP_HDMI_DDC_DATA

=MCP_HDMI_TXD_P/N<2>

=MCP_HDMI_TXD_P/N<1>

=MCP_HDMI_DDC_CLK

MCP Signal

=MCP_HDMI_TXD_P/N<0>

=MCP_HDMI_TXC_P/N

TMDS/HDMI

TMDS_IG_TXC_P/N

TMDS_IG_TXD_P/N<0>

TMDS_IG_DDC_CLK

TMDS_IG_TXD_P/N<1>

TMDS_IG_TXD_P/N<2>

TMDS_IG_DDC_DATA

TP_DP_IG_AUX_CHP/N

DP_IG_DDC_CLK

DP_IG_ML_P/N<2>

DP_IG_ML_P/N<1>

DP_IG_ML_P/N<3>

DisplayPort

5 mA (A01)

RGB ONLY

avoids a leakage issue since

feature via software. This

NOTE: All Apple products set strap to

Network Interface Select

Interface

RGMII

MII 0

1

ENET_TXD<0>

DDC_CLK0/DDC_DATA0 pull-ups still required.

Okay to float all TV_DAC signals.

TV DAC Disable:

Y / Y

DDC_CLK0/DDC_DATA0 pull-ups still required.

Okay to float all RGB_DAC signals.

Okay to float XTALIN_TV and XTALOUT_TV.

103 mA

103 mA

206 mA (A01)

Comp / Pb

MCP79 requires a S5 pull-up.

C / Pr

190 mA (A01, 1.8V)

18 OF 109

051-7898

C.0.0

<CURRENT_DESIGN_SHEET> OF <TOTAL_DESIGN_SHEETS>

=MCP_HDMI_TXD_N<0>

=MCP_HDMI_TXC_N

=MCP_HDMI_TXD_P<0>

=MCP_HDMI_TXD_P<1>

=MCP_HDMI_TXD_N<1>

=MCP_HDMI_TXD_P<2>

LVDS_IG_A_CLK_N

LVDS_IG_A_DATA_N<3>

MCP_HDMI_RSET

MCP_HDMI_VPROBE

DP_IG_CA_DET

PP1V05_ENET_MCP_PLL_MAC

=PP1V05_S0_MCP_HDMI_VDD

PP3V3_S0_MCP_VPLL

=PP3V3R1V8_S0_MCP_IFP_VDD

PP3V3_S0_MCP_DAC

MCP_MII_COMP_GND

MCP_MII_COMP_VDD

LVDS_IG_PANEL_PWR

LVDS_IG_BKL_ON

=MCP_HDMI_TXC_P

=MCP_HDMI_TXD_N<2>

MCP_CLK27M_XTALIN

LVDS_IG_DDC_DATA

LVDS_IG_DDC_CLK

MCP_TV_DAC_VREF

DP_IG_AUX_CH_P

DP_IG_AUX_CH_N

=MCP_HDMI_HPD

ENET_MDIO

MCP_CLK25M_BUF0_R

MCP_DDC_DATA0

MCP_DDC_CLK0

TP_MCP_RGB_RED

TP_MCP_RGB_GREEN

TP_MCP_RGB_BLUE

TP_MCP_RGB_HSYNC

TP_MCP_RGB_VSYNC

CRT_IG_R_C_PR

CRT_IG_G_Y_Y

LVDS_IG_A_CLK_P

LVDS_IG_A_DATA_P<0>

LVDS_IG_A_DATA_N<0>

LVDS_IG_A_DATA_P<2>

LVDS_IG_A_DATA_P<1>

LVDS_IG_A_DATA_N<1>

LVDS_IG_A_DATA_P<3>

LVDS_IG_A_DATA_N<2>

LVDS_IG_B_CLK_P

LVDS_IG_B_CLK_N

LVDS_IG_B_DATA_P<1>

LVDS_IG_B_DATA_P<0>

LVDS_IG_B_DATA_N<0>

LVDS_IG_B_DATA_P<2>

LVDS_IG_B_DATA_N<1>

LVDS_IG_B_DATA_N<2>

LVDS_IG_B_DATA_P<3>

LVDS_IG_B_DATA_N<3>

=MCP_HDMI_DDC_DATA

=MCP_HDMI_DDC_CLK

MCP_IFPAB_RSET

MCP_IFPAB_VPROBE

MCP_TV_DAC_RSET

ENET_RXD<0>

TP_ENET_INTR_L

ENET_RXD<3>

ENET_RX_CTRL

ENET_CLK125M_RXCLK

ENET_RXD<2>

ENET_RXD<1>

ENET_RESET_L

ENET_MDC

TP_ENET_PWRDWN_L

=MCP_MII_RXER

=MCP_MII_COL

=MCP_MII_CRS

CRT_IG_B_COMP_PB

CRT_IG_HSYNC

CRT_IG_VSYNC

MCP_MII_VREF

ENET_TX_CTRL

ENET_CLK125M_TXCLK

ENET_TXD<3>

ENET_TXD<2>

ENET_TXD<1>

ENET_TXD<0>

=PP3V3_ENET_MCP_RMGT

=PP3V3_S0_MCP_GPIO

=PP3V3_ENET_MCP_RMGT

=PP3V3_S5_MCP_GPIO

=PP1V05_ENET_MCP_RMGT

LPCPLUS_GPIO

TP_MCP_RGB_DAC_VREF

TP_MCP_RGB_DAC_RSET

MCP_CLK27M_XTALOUT

LVDS_IG_BKL_PWM

=DVI_HPD_GMUX_INT

MCP Ethernet & Graphics

SYNC_MASTER=T18_MLB

SYNC_DATE=04/04/2008

31B6 77D3

31B6 77C3

31C8 77D3

23C6 75B3

31C6 77D3

23C6 75B3

69D3

69D3

6C7 68C5

6C7 68C5

8C4

8C4

8C4

8C4

8C4

31C6 77D3

8C4

8C4

8C4

8D4

8D4

8D4

8D4

6C7 68C2 75B3

6C7 68C2 75B3

6C7 68C2 75B3

31C6 77D3

6C7 68C2 75B3

6C7 68C2 75B3

6C7 68C2 75B3

68B3 75B3

68B3 75B3

31C6 77D3

2

1

R1820

1/16W

MF-LF

402

47K

5%

42C3

2

1

R1860

100K

1/16W

5%

MF-LF

402

2

1

R1861

MF-LF

1/16W

100K

5%

402

2

1

R1850

MF-LF

5%

1/16W

402

10K

D38

C38

C37

A35

E36

A36

D36

B36

C36

D25

C25

C24

B24

C26

D24

A24

E24

B23

C23

C22

A23

G23

C21

D21

J22

A41

B38

C39

B39

A40

A39

B40

M26

M27

T25

K32

J32

M28

M29

V23

U23

T23

K24

J24

E28

F23

J23

B22

C27

B27

B26

F40

E37

G39

N30

M30

L30

K30

L29

K29

J29

H29

L31

K31

G31

E32

B34

C34

D33

C33

D32

C32

B32

A32

B35

C35

F31

C31

J30

J33

H33

F33

G33

G35

F35

D35

E35

J31

B15

E16

D43

C43

E31

B30

A31

D31

C30

B31

E23

U1400

OMIT

MCP79-TOPO-B

BGA

(6 OF 11)

8C4

8C4

8C4

8D4

8D4

69A5

2

1

R1811

1%

402

49.9

MF-LF

1/16W

2

1

R1810

49.9

402

MF-LF

1/16W

1%

8D4

8D4

8D4

8D4

8D4

23C7 75B3

23C7 75B3

69D3

8B4

69C7 75B3

69C7 75B3

69D3

69D3

69D3

69D3

69D3

69D3

69D3

69D3

72B7 72C8

68C8

71A7 72B7

8D4

8D4

31B7 77C3

31B1 77D3

31C1 77D3

31C1 77D3

31C1 77D3

31C1 77D3

31C1 77D3

32A5 77D3

31B6 77D3

22A4

22A6

7D7 23D7

23C5

7B6 23D7

23D2

77D3

77D3

7B5 17D7 22A5 22B6

7C5 18D1 20A4

7B5 17D3 22A5 22B6

7A3 19C1

7A5 22D6

剩余80页未读,继续阅读

点击了解资源详情

点击了解资源详情

点击了解资源详情

2010-01-20 上传

2020-03-31 上传

2022-11-15 上传

2023-09-24 上传

2019-06-26 上传

JOZECN

- 粉丝: 760

- 资源: 3421

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功