华为VHDL同步设计:避免常见问题与资源优化

需积分: 9 173 浏览量

更新于2024-07-31

收藏 427KB PPT 举报

华为的VHDL设计风格和实现是一个针对复杂电子系统设计的关键技术,特别是在高速和实时应用中。VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,它允许工程师以软件编程的方式来描述数字电路的行为,适用于像FPGA(Field-Programmable Gate Array)这样的可编程逻辑器件。

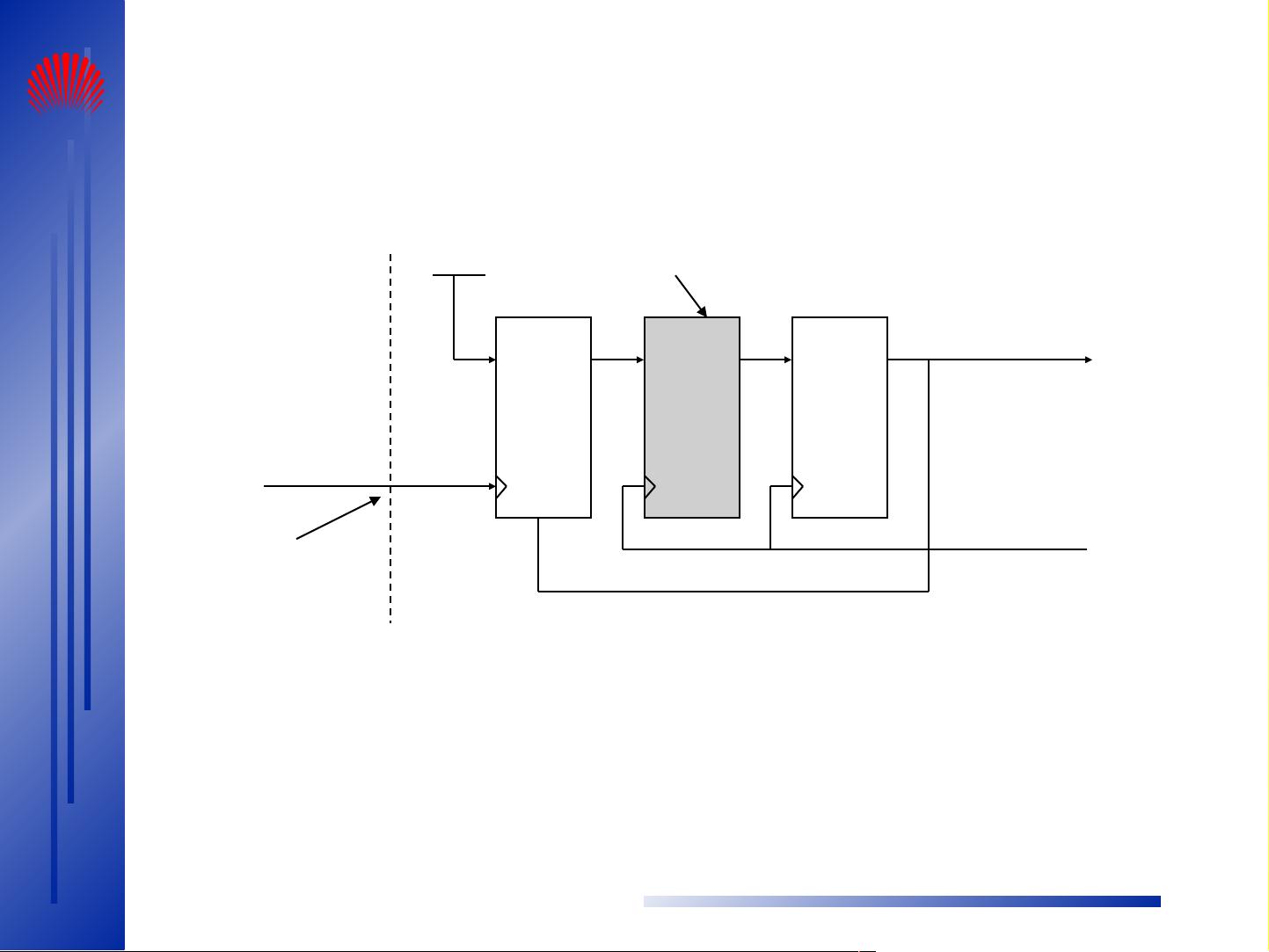

本文档首先强调了同步设计的重要性。同步设计是指在系统中,数据通过时钟信号进行精确的传输,只要时序满足要求,就能确保下游逻辑单元准确地接收和处理上游数据。相比之下,异步设计存在不确定性,可能导致数据传递错误,因为它依赖于上游数据变化的不确定时刻。

文章列举了一些案例,解释了为什么在实际应用中倾向于选择同步设计。例如,如果设计在两年后不能工作,可能是因为异步设计对时序的敏感性导致了不可控的故障。同样,即使在设计初期可以工作,布线改动也可能影响异步设计的稳定性,而同步设计则更易于控制。时间仿真虽然在某些情况下有用,但对于异步设计来说,它并不能保证实际硬件行为的正确性。

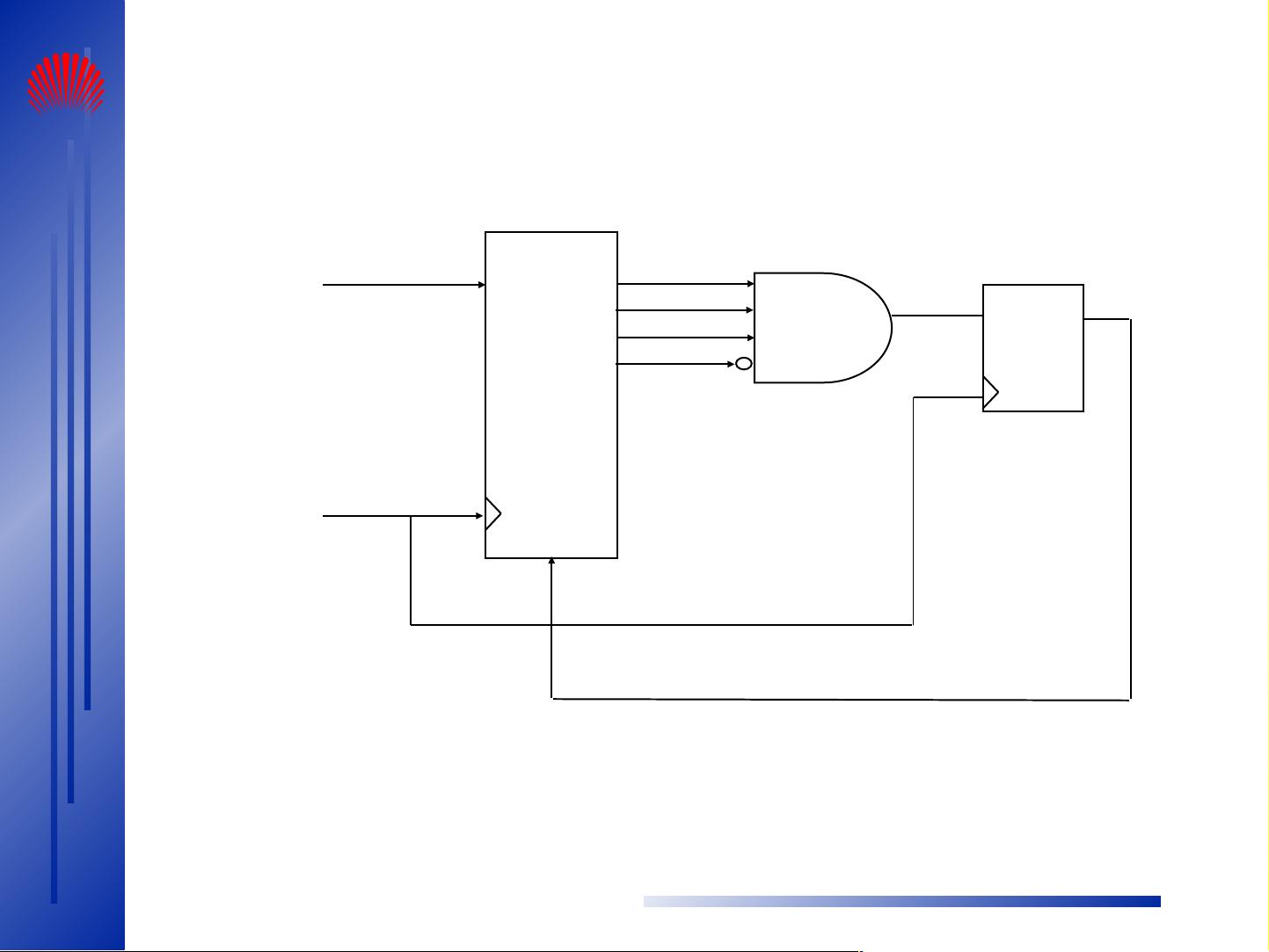

作者特别提醒设计师要注意时钟信号和异步复位信号的质量,因为在快速FPGA中,微小的毛刺信号可能导致意外的触发器响应,这在异步设计中是一个难以克服的问题。为了避免这些问题,设计者应遵循原则,避免组合逻辑产生的信号用于作为时钟或异步控制信号。

文中还给出了一个具体的例子,展示了一个计数器设计中的问题。由于MSB(Most Significant Bit)线路较短,当计数达到终点时,会产生毛刺。由于与门的电平敏感特性,这种毛刺可能导致寄存器误操作,因此在编写VHDL代码时,应避免使用计数器终点信号作为时钟,以确保设计的正确性和稳定性。

总结起来,华为的VHDL设计风格和实现着重于同步设计的规范和优势,以及如何避免异步设计中常见的问题,包括毛刺引发的寄生行为。这对于保证FPGA和类似硬件系统的可靠性和性能至关重要。理解并遵循这些原则可以帮助设计师提高设计质量和可维护性。

2020-07-14 上传

2010-01-26 上传

2018-07-31 上传

181 浏览量

101 浏览量

187 浏览量

347 浏览量

159 浏览量

wyf200913866

- 粉丝: 1

- 资源: 42

最新资源

- Gooper1 Data Pack:新的 G1DP 存储库。 去贡献!-开源

- iOS Apprentice v7.0 (iOS12 & Swift4.2 & Xc.zip

- PersonalPage:我的NextJS个人开发人员页面

- CS300P07

- AppAuth-JS:JavaScript客户端SDK,用于与OAuth 2.0和OpenID Connect提供程序进行通信

- js和CSS3炫酷圆形导航菜单插件

- 裂纹检测:使用计算机视觉工具箱进行裂纹检测-matlab开发

- 开源软路由OPENWRT2020.9.8原版VMWARE固件

- Onboard-SDK:DJI Onboard SDK官方资料库

- projetoFinal-ips-2-ano

- chips_thermal_face_dataset:芯片热敏面数据集是一个大规模的热敏面数据集(来自3个不同大洲的1200幅男性和女性图像,年龄在18-23岁之间)。 该数据集将可供全世界的研究人员使用最新的深度学习方法创建准确的热面部分类和热面部识别系统

- pamansayurdev.github.io:网站paman sayur

- MO_Ring_PSO_SCD:它是用于多模态多目标优化的多目标 PSO-matlab开发

- resynthesizer:用于纹理合成的gimp插件套件

- NavigationDrawer:这是一个示例项目,用于演示如何制作导航抽屉。此外,在这个项目中,我添加了材料设计,因此对于想要实现材料设计、工具栏等的人也有帮助

- hacker-news-clone