5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

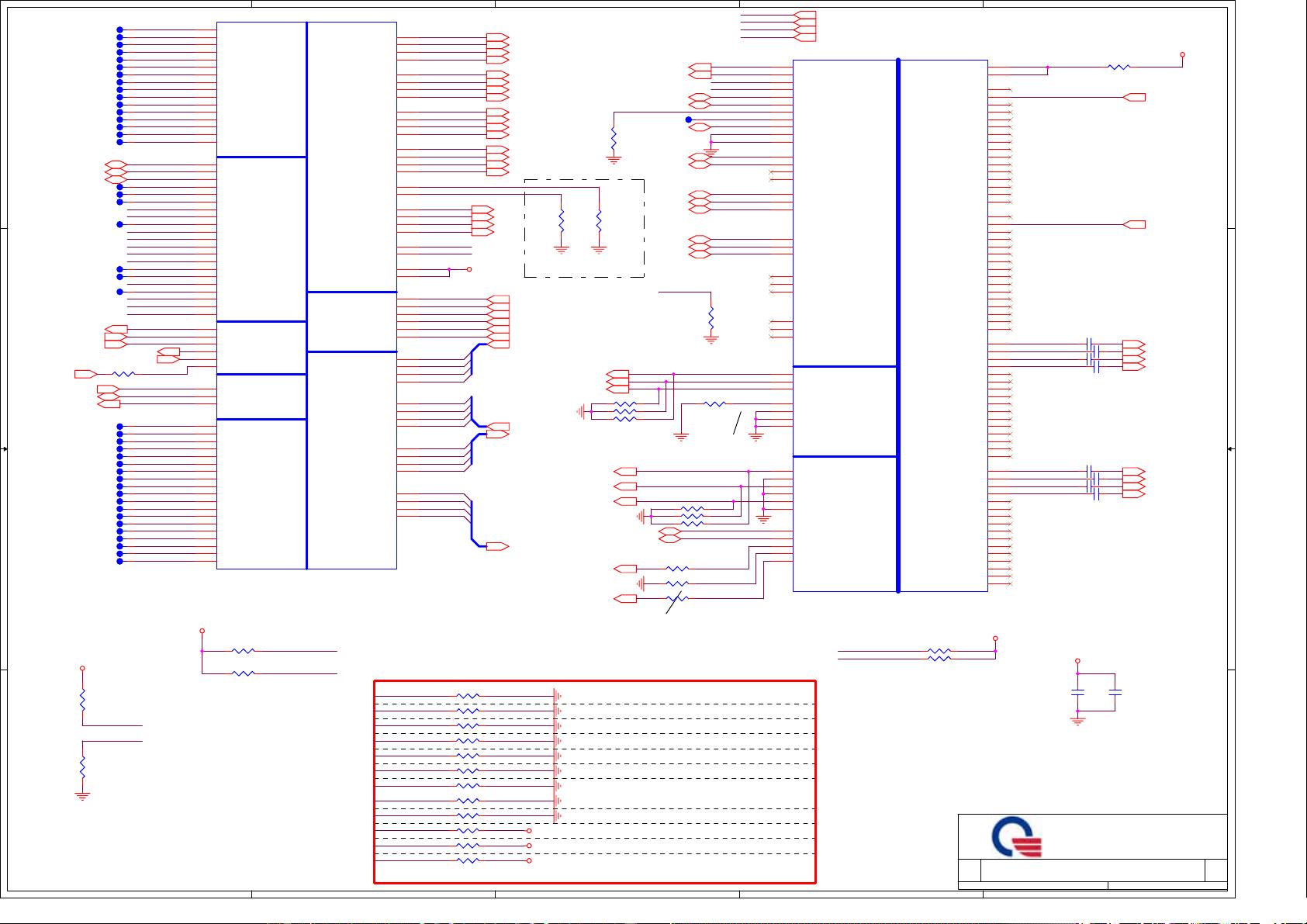

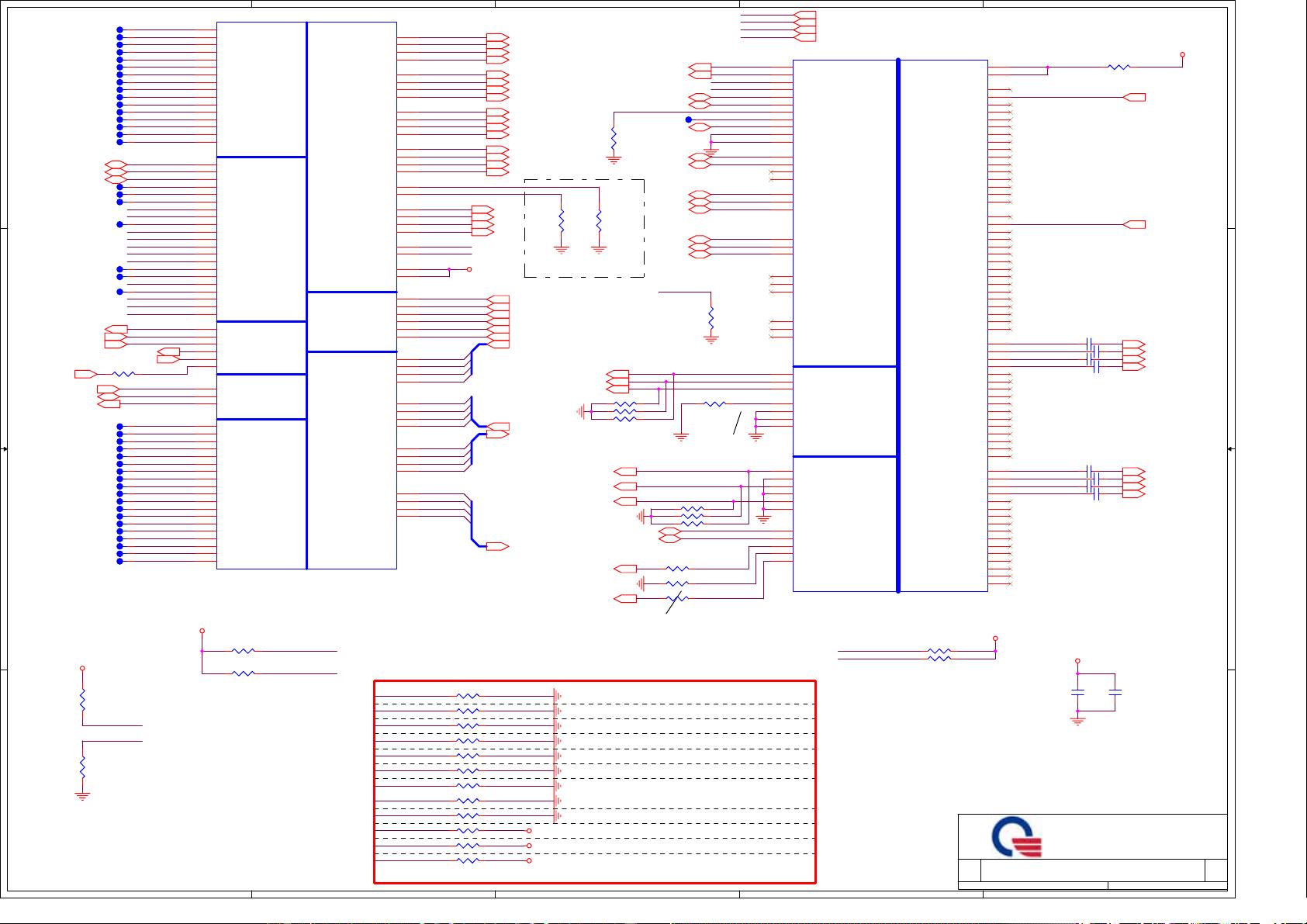

Layout as short as passable

NC from WW45

< 0.1" . 15mils/15mils space

< 0.1" . 15mils/15mils space

use 1% R

15mils/10mils

15mils/15mils

GMCH Strap pin need to check

7.MCH_CFG_16 FSB Dynmic ODT: Low=Dynamic ODT Disabled,

High=Dynamic ODT Enabled.

6.MCH_CFG_11: Low=Calistoga, High=Reserved

5.MCH_CFG_10 Host PLL VCC Select: Low=Reserved, High=Mobility

4.MCH_CFG_9 PCI Exp Graphics Lane: Low =Reserved,High=Mobility

3.MCH_CFG_7 CPU Strap Low=RSVD, High=Mobile CPU

2.MCH_CFG_6 DDR : Low =Moby Dick, High= Calistoga (Default)

1.MCH_CFG_5 Low = DMI X2, High=DMIX4

8.MCH_CFG_19 DMI LANE Reversal:Low=Normal,

High=LANES Reversed.

9.MCH_CFG_18 VCC Select: LOW=1.05V, High=1.5V

10.MCH_CFG_20 PCIE Backward interpoerability mode: Low= only

SDVO or PCIE x1 is operational (defaults) ,High=SDVO and PCIE x1

are operation simultaneously via the PEG port.

Place within 500 mils of GMCH

00 = Partial CLK gating disable 01 = XOR mode enabled

10 = All Z mode enabled 11 = Normal operation (Default)

Place close ball AK1/AK41

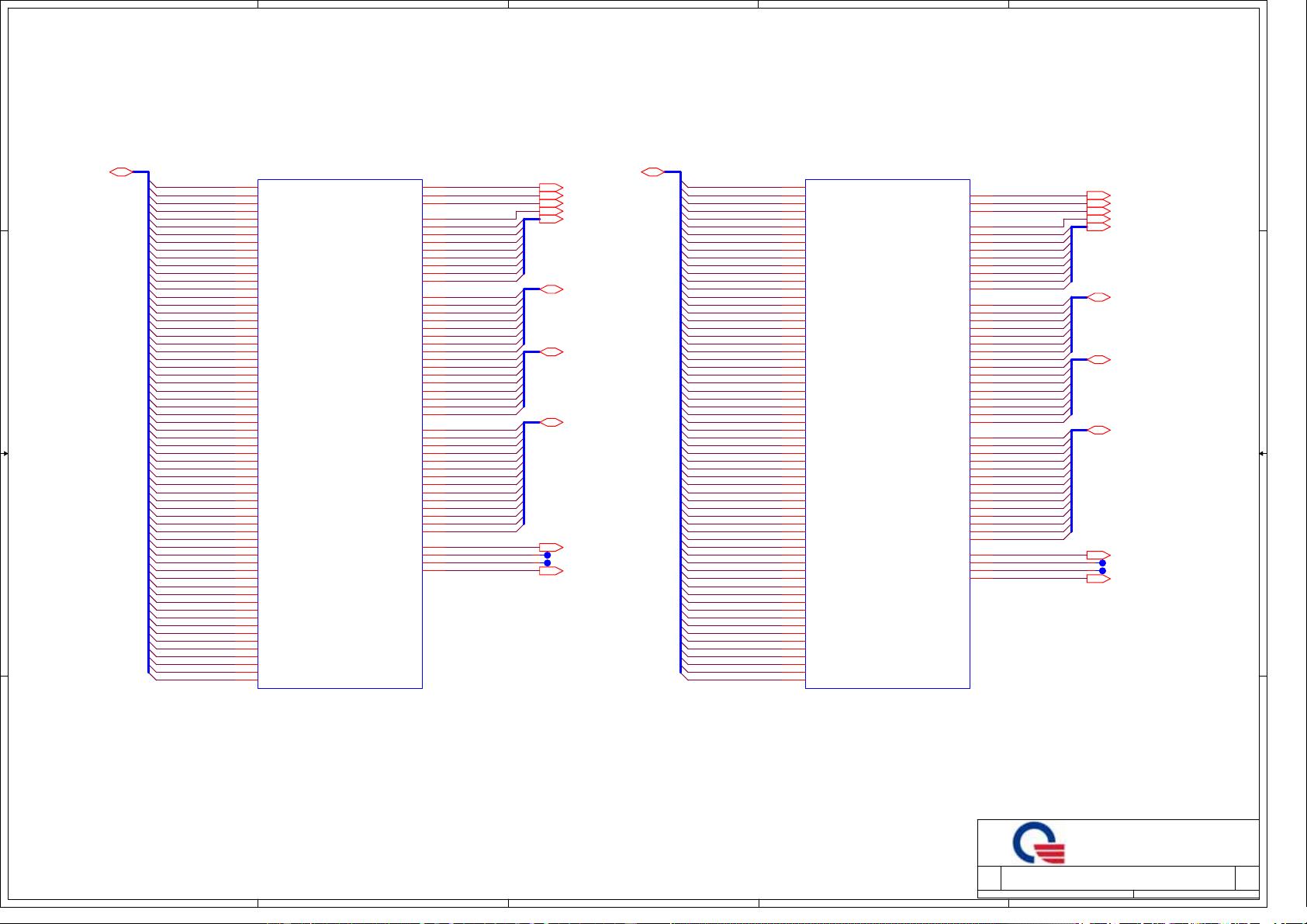

GMCH DMI VEDIO(3 OF 6)

1ACustom

942Tuesday, November 29, 2005

Size Document Number Rev

Date: Sheet

of

Quanta Computer Inc.

PROJECT : DW1

MCH_RSVD_5

MCH_RSVD_6

MCH_RSVD_7

MCH_RSVD_8

TV_DCONSEL0

TV_DCONSEL1

MCH_RSVD_11

MCH_RSVD_12

MCH_RSVD_13

MCH_RSVD_14

MCH_RSVD_15

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

PM_BMBUSY#

PM_EXTTS#0

PM_EXTTS#1

SDVO_CtrlClk

MCH_ICH_SYNC

TP_MCH_NC0

TP_MCH_NC1

TP_MCH_NC2

TP_MCH_NC3

TP_MCH_NC4

TP_MCH_NC5

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC8

TP_MCH_NC9

TP_MCH_NC10

TP_MCH_NC11

TP_MCH_NC12

TP_MCH_NC13

TP_MCH_NC14

TP_MCH_NC15

TP_MCH_NC16

TP_MCH_NC17

TP_MCH_NC18

RST IN# MCH

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR#0

M_CLK_DDR#1

M_CKE0

M_CKE1

M_CS#0

M_CS#1

M_ODT0

M_ODT1

M_OCDCOMP_1

M_OCDCOMP_0

M_RCOMP

M_RCOMP#

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

DMI_TXN2

DMI_TXN3

DMI_RXP3

DMI_RXP2

DMI_RXP1

DMI_RXP0

DPST_PWM

L_CLKCTLA

L_CLKCTLB

EDIDCLK

EDIDDATA

L_IBG

L_VBG

DISP_ON

L_VREFH

L_VREFL

TXLCLKOUT-

TXLCLKOUT+

TXLOUT0-

TXLOUT1-

TXLOUT2-

TXLOUT0+

TXLOUT1+

TXLOUT2+

S-CD

TVIREF

EXP_A_COMPX

VSYNC1

HSYNC1

CRTIREF

PM_EXTTS#0

PM_EXTTS#1

M_RCOMP#

M_RCOMP

CLK_MCH_OE#

MCH_RSVD_1

MCH_RSVD_2

MCH_RSVD_3

MCH_RSVD_4

CRT_R

S-CVBS

LCD_BLON

MCH_CFG_3

MCH_CFG_4

DMI_TXN0

DMI_TXN1

S-YD

CRT_G

SDVO_CtrlData

DMI_TXP0

DMI_RXN0

DMI_TXP1

DMI_RXN1

DMI_TXP2

DMI_RXN2

DMI_TXP3

DMI_RXN3 CRT_B

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_RXN2

EXP_RXP2

MCH_CFG_6

MCH_CFG_7

MCH_CFG_9

MCH_CFG_16

MCH_CFG_19

MCH_CFG_5

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_20

MCH_CFG_18

M_CLK_DDR2

M_CLK_DDR3

M_CLK_DDR#2

M_CLK_DDR#3

M_CKE2

M_CKE3

M_CS#2

M_CS#3

SMDDR_VREF

1.8VSUS

+3V

+V1.5_PCIE

L_CLKCTLB

L_CLKCTLA

LCD_BLON

M_ODT3

M_ODT2

1.8VSUS

+3V

SMDDR_VREF

+V1.5_PCIE

+3V

+3V

+3V

SMDDR_VREF

+3V

T5

T167

T29

C28 *0.1U

R108 *2.2K

T188

T41

R95 *2.2K

T162

R397 *10K/F

T163

T4

T45

R77 *2.2K

R406 150/F

R409 150/F

T7

R414 75/F

T8

T159

C26 *0.1U

T186

C33 *0.1U

T2

T44

C25 *0.1U

R399 10K/F

R103 *2.2K

T1

R105 *2.2K

R400

100/F

T184

T166

C32 *0.1U

T189

R59 *1K

C190

0.1U

R15 24.9/F

T160

T40

T183

R396 *1K/F

T182

R27 10K/F

R25

100K

R71

*40.2/F

R106

80.6/F

R34 39/F

T49

T179

T168

T157

R411 150/F

R17 *2.2K

T165

T14

T178

R109 *2.2K

T28

T52

R41 *1K/F

C35 *0.1U

T185

R68 4.99K/F

R75 *2.2K

T3

C34 *0.1U

T181

R107

80.6/F

T161

PM

MISC

NC

DDR MUXINGCLKDMI

CFGRSVD

U27B

Calistoga

D1

C41

C1

BA41

BA40

BA39

BA3

BA2

BA1

B41

B2

AY41

AY1

AW41

AW1

A40

A4

A39

A3

H28

H27

AY35

AR1

AW7

AW40

AW35

AT1

AY7

AY40

AU20

AT20

BA29

AY29

AW13

AW12

AY21

AW21

AL20

AF10

BA13

BA12

AY20

AU21

AV9

AT9

AK1

AK41

J25

K27

J26

K16

K18

J18

F18

E15

F15

E18

D19

D16

G16

E16

D15

G15

K15

C15

H16

G18

H15

G28

F25

H26

G6

AH33

AH34

A27

A26

C40

D41

AE35

AF39

AG35

AH39

AC35

AE39

AF35

AG39

AE37

AF41

AG37

AH41

AC37

AE41

AF37

AG41

AF33

AG33

T32

R32

AG11

AF11

K28

J19

H32

F3

F7

H7

K30

J29

A41

A35

A34

D28

D27

NC0

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC14

NC15

NC16

NC17

NC18

SDVO_CTRLCLK

SDVO_CTRLDATA

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMP#

SM_RCOMP

SM_VREF_0

SM_VREF_1

CFG_18

CFG_19

CFG_20

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

PM_THRMTRIP#

PWROK

RSTIN#

D_REFCLKIN#

D_REFCLKIN

D_REFSSCLKIN#

D_REFSSCLKIN

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

G_CLKIN#

G_CLKIN

RSVD_1

RSVD_2

RSVD_5

RSVD_6

LT_RESET#

RSVD_8

RSVD_0

RSVD_3

RSVD_4

RSVD_7

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_14

RSVD_15

T35

R104

*40.2/F

R82 *2.2K

LVDS

PCI-EXPRESS GRAPHICS

TV

VGA

U27C

Calistoga

D40

D38

F34

G38

H34

J38

L34

M38

N34

P38

R34

T38

V34

W38

Y34

AA38

AB34

AC38

D34

F38

G34

H38

J34

L38

M34

N38

P34

R38

T34

V38

W34

Y38

AA34

AB38

F36

G40

H36

J40

L36

M40

N36

P40

R36

T40

V36

W40

Y36

AA40

AB36

AC40

D36

F40

G36

H40

J36

L40

M36

N40

P36

R40

T36

V40

W36

Y40

AA36

AB40

J30

H30

H29

G26

G25

B38

C35

F32

C33

C32

A33

A32

C37

B35

A37

B37

B34

A36

E27

E26

G30

D30

F29

F30

D29

F28

D32

A16

C18

A19

J20

B16

B18

B19

E23

D23

C26

C25

C22

B22

G23

J22

A21

B21

H23

EXP_A_COMPI

EXP_A_COMPO

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXN_2

EXP_A_RXN_3

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

EXP_A_RXN_13

EXP_A_RXN_14

EXP_A_RXN_15

EXP_A_RXP_0

EXP_A_RXP_1

EXP_A_RXP_2

EXP_A_RXP_3

EXP_A_RXP_4

EXP_A_RXP_5

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

EXP_A_RXP_9

EXP_A_RXP_10

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_TXN_0

EXP_A_TXN_1

EXP_A_TXN_2

EXP_A_TXN_3

EXP_A_TXN_4

EXP_A_TXN_5

EXP_A_TXN_6

EXP_A_TXN_7

EXP_A_TXN_8

EXP_A_TXN_9

EXP_A_TXN_10

EXP_A_TXN_11

EXP_A_TXN_12

EXP_A_TXN_13

EXP_A_TXN_14

EXP_A_TXN_15

EXP_A_TXP_0

EXP_A_TXP_1

EXP_A_TXP_2

EXP_A_TXP_3

EXP_A_TXP_4

EXP_A_TXP_5

EXP_A_TXP_6

EXP_A_TXP_7

EXP_A_TXP_8

EXP_A_TXP_9

EXP_A_TXP_10

EXP_A_TXP_11

EXP_A_TXP_12

EXP_A_TXP_13

EXP_A_TXP_14

EXP_A_TXP_15

L_BKLTEN

L_CLKCTLA

L_CLKCTLB

L_DDC_CLK

L_DDC_DATA

L_IBG

L_VBG

L_VDDEN

L_VREFH

L_VREFL

LA_CLK#

LA_CLK

LA_DATA#_0

LA_DATA#_1

LA_DATA#_2

LA_DATA_0

LA_DATA_1

LA_DATA_2

LB_CLK#

LB_CLK

LB_DATA#_0

LB_DATA#_1

LB_DATA#_2

LB_DATA_0

LB_DATA_1

LB_DATA_2

L_BKLTCTL

TV_DACA_OUT

TV_DACB_OUT

TV_DACC_OUT

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

CRT_BLUE

CRT_BLUE#

CRT_DDC_CLK

CRT_DDC_DATA

CRT_GREEN

CRT_GREEN#

CRT_HSYNC

CRT_IREF

CRT_RED

CRT_RED#

CRT_VSYNC

T180

T36

R412 150/F

T37

C38

2.2U

T25

R64 255/F

R33 39/F

C27 *0.1U

T158

T164

R408 150/F

R26 10K/F

R398

1.5K/F

MCH_BSEL04

MCH_BSEL14

MCH_BSEL24

MCH_ICH_SYNC17

PM_BMBUSY#18

PM_THRMTRIP#5,16

PM_EXTTS#014,15

PM_EXTTS#114,18

DELAY_VR_PWRGOOD18,41

PLT_RST-R#17

M_CLK_DDR0 15

M_CLK_DDR1 15

M_CLK_DDR#0 15

M_CLK_DDR#1 15

M_CKE1 14,15

M_CKE0 14,15

M_CS#0 14,15

M_CS#1 14,15

M_ODT1 14,15

M_ODT0 14,15

CLK_PCIE_3GPLL# 4

CLK_PCIE_3GPLL 4

DREFCLK# 4

DREFCLK 4

DREFSSCLK# 4

DREFSSCLK 4

EDIDDATA20

DISP_ON20

HSYNC32

VSYNC32

CRT_B32

CRT_G32

CRT_R32

DMI_RXP[3:0] 17

S-CVBS

S-YD35

S-CD35

DMI_TXP[3:0] 17

LCD_BLON20

EDIDCLK20

DMI_TXN[3:0] 17

DDCCLK32

DDCDAT32

DPST_PWM20

DMI_RXN[3:0] 17

SDVOB_GREEN- 13

SDVOB_BLUE- 13

SDVOB_CLK- 13

SDVOB_RED- 13

SDVOB_GREEN+ 13

SDVOB_BLUE+ 13

SDVOB_CLK+ 13

SDVOB_RED+ 13

EXP_RXN2 13

EXP_RXP2 13

SDVO_CtrlClk13

SDVO_CtrlData13

M_CLK_DDR2 15

M_CLK_DDR3 15

M_CLK_DDR#2 15

M_CLK_DDR#3 15

M_CKE3 14,15

M_CKE2 14,15

M_CS#2 14,15

M_CS#3 14,15

TXLOUT1+20

TXLOUT1-20

TXLCLKOUT+20

TXLCLKOUT-20

TXLOUT0-20

TXLOUT0+20

TXLOUT2-20

TXLOUT2+20

SMDDR_VREF 15,40

+V1.5_PCIE 11

1.8VSUS 10,15,36,40

+3V 4,5,11,13,14,15,16,17,18,19,20,24,29,30,31,32,33,34,35,36,38

M_ODT3 14,15

M_ODT2 14,15