"N4-DDR FPGA 开发板上的MIPS五段流水CPU设计实验指南"

需积分: 0 132 浏览量

更新于2023-12-22

收藏 1.93MB PDF 举报

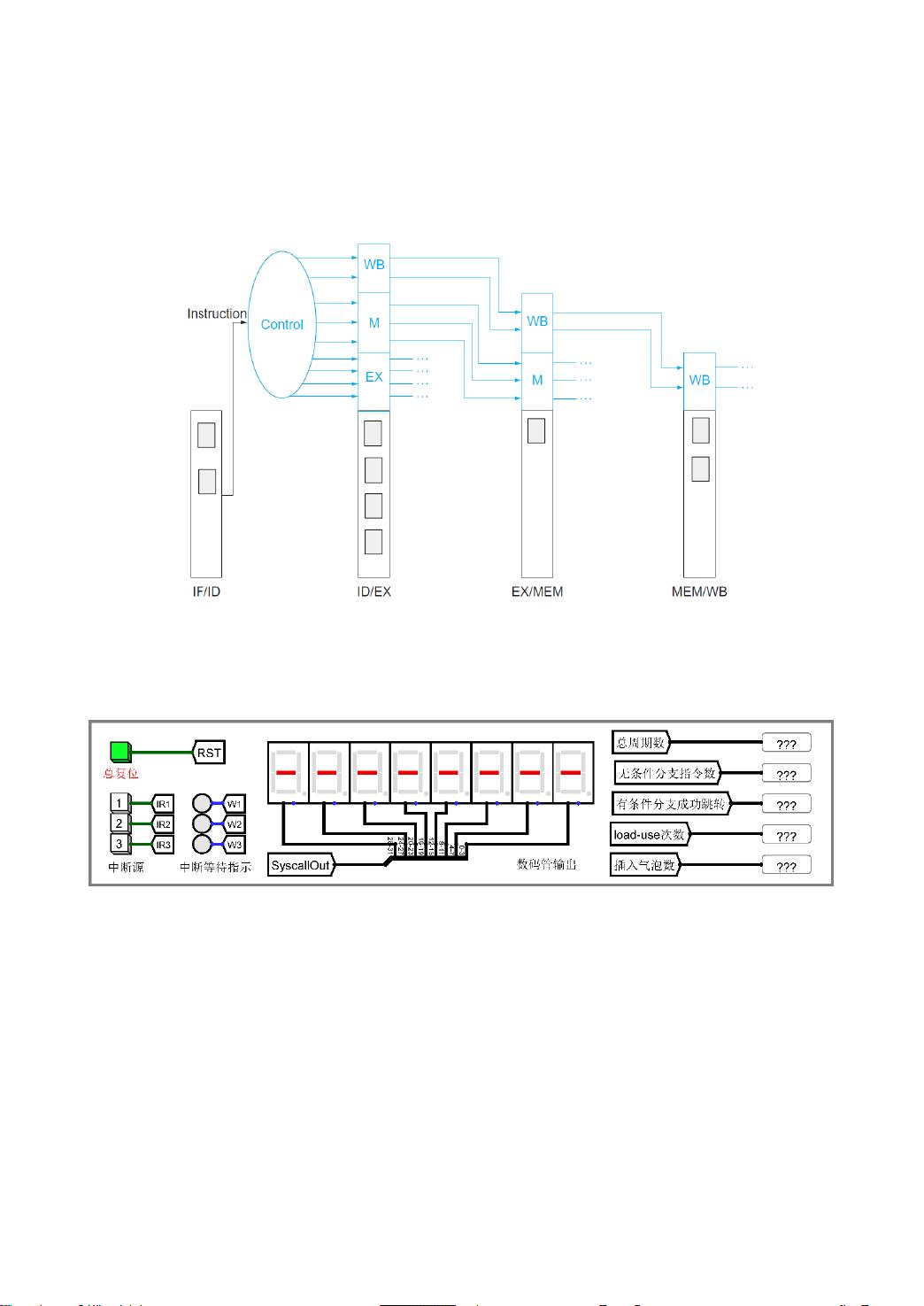

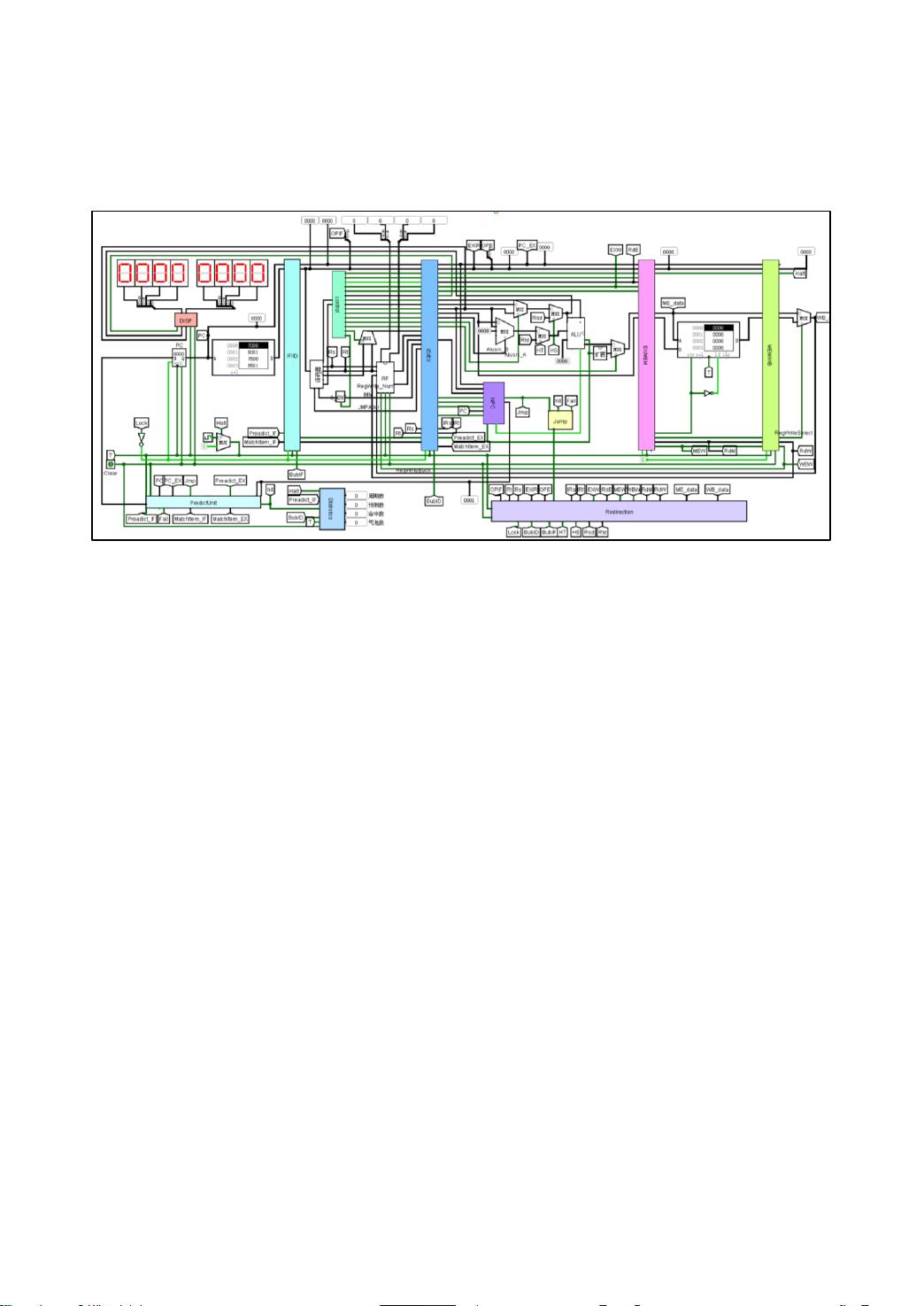

课程设计指南V1.81的第一章介绍了MIPS五段流水CPU设计实验1.1.1的实验目的和内容。实验目的是让学生掌握N4-DDR FPGA开发板的使用,能够将课程实验中设计完成的单周期CPU在该平台上具体实现,并且能够正确运行标准测试程序。实验内容包括在Logisim平台中构建一个32位MIPS CPU单周期处理器,该处理器支持20余条基础指令,以及2条C类运算指令、1条M类存储指令、1条B类分支指令。要求采用团队合作的形式将Logisim平台中完成的单周期CPU移植到N4-DDR FPGA开发板进行具体实现,最终能在开发板上正确运行标准测试程序。

实验要求包括支持显示功能切换,能够在FPGA开发板上利用8个八段数码管进行正确的显示输出,并且可以通过拨码开关实现显示功能的切换。这些显示功能包括正常数据输出显示、不同内存地址内存值的观察、PC值观察、时钟周期数观察以及其他运行状态观察。

整个实验的目的是让学生通过实际操作掌握FPGA开发板的使用方法,同时将课程中学到的单周期CPU设计知识应用到实际中,使学生在实践中能够加深对课程知识的理解和掌握。通过团队合作的方式,也培养了学生的团队合作能力和解决问题的能力。

这个实验对学生来说是具有挑战性的,因为它要求学生不仅要掌握单周期CPU设计的基础知识,还要学会使用FPGA开发板进行具体实现。这需要学生具备一定的逻辑设计能力和对FPGA开发板的熟练操作能力。

在实验过程中,学生需要对Logisim平台中完成的单周期CPU进行移植,并且要能在N4-DDR FPGA开发板上正确运行标准测试程序。这一过程需要学生具备一定的动手能力和分析解决问题的能力,因为移植的过程中难免会遇到一些问题需要学生去解决。

总的来说,这个实验对学生来说是一个很好的综合应用实践,它不仅培养了学生的动手能力和解决问题能力,还锻炼了学生的团队合作能力和实践能力。通过完成这个实验,学生将更加深入地理解课程中所学到的知识,并且为将来的工程实践奠定了坚实的基础。

2022-08-08 上传

2022-08-03 上传

2024-10-20 上传

2005-08-14 上传

110 浏览量

2009-11-29 上传

2019-11-01 上传

吹狗螺的简柏承

- 粉丝: 21

最新资源

- C++实现的Excel与音频文件高效操作工具

- 掌握eq、get、find函数的实现技巧

- JSP个人博客案例分享与教程

- C++程序设计第二版教程与习题源码解析

- note-taker:Express.js 主力文件解析与应用

- DAEMON虚拟光驱软件介绍与应用

- 三维人脸识别在移动支付领域的应用研究

- Android触摸控制实现代码示例解析

- SSH框架系统源码与数据库设计开发完整指南

- 探索.NET ORM框架:实战教程与VS2010示例

- EditPlus v4.1.868 双语版简体汉化介绍

- 邱关源电子教案:考研电路复习资料详解

- PHP学习资源:精选源码供初学者参考

- 轻松实现Activity/Fragment/VGroup多种状态显示的PageStateLayout

- Unix网络编程卷1源码解析与学习

- 飞鱼在线编辑器后台管理功能与文件架构解析