PG逻辑新公式在全加器设计中的应用与等价证明

133 浏览量

更新于2024-08-31

收藏 252KB PDF 举报

"等价型PG逻辑及其在加法器设计中的应用"

等价型PG逻辑是一种在数字逻辑设计中用于优化加法器结构的方法,特别是在高速全加器的设计中,它能够显著提升运算速度和效率。PG逻辑,即Propagation(传播)和Generation(生成)逻辑,是分析和设计多位加法器的关键工具。本文主要探讨了如何通过现有的PG逻辑公式推导出新的逻辑公式,并证明了它们的等价性,以指导全加器的连线策略。

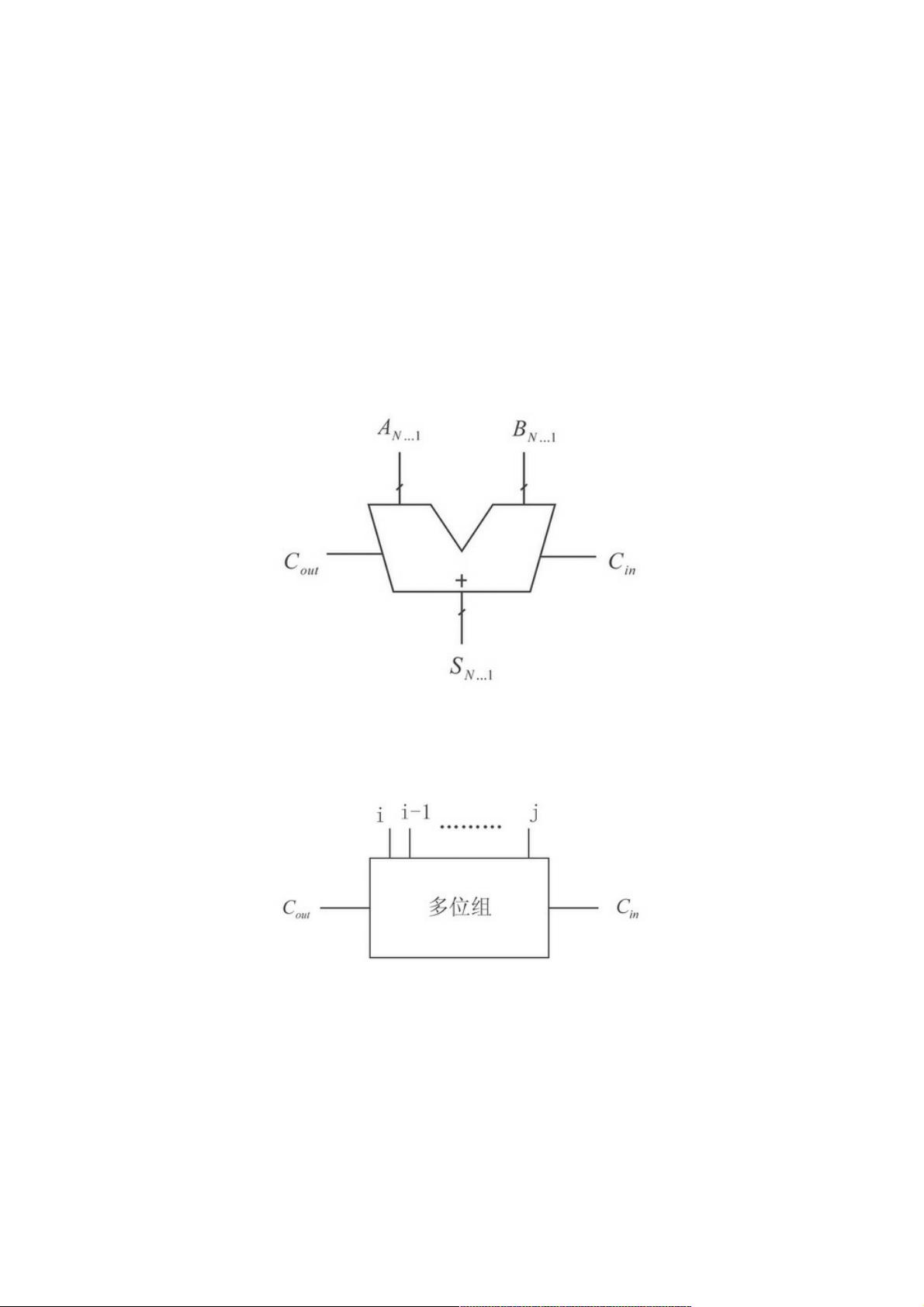

全加器是数字逻辑电路的基础组件,它不仅考虑两个输入位的加法,还处理前一位的进位。一个N位全加器接收N个输入位A和B,以及一个进位输入Cin,产生N个和位S和一个进位输出Cout。进位的传播和生成是全加器的核心功能,直接影响加法结果的计算。

在传统的行波进位全加器中,进位是逐位依次传递的,这导致了较大的延迟。为了提高速度,快速全加器采用PG逻辑,将加数和被加数的相同下标位分组,形成多位组。通过计算这些多位组的PG逻辑,可以预估每个组的进位输出是直接产生还是传播进位输入。

PG逻辑中,Gi:j表示多位组i到j的和逻辑,而Pi:j表示多位组i到j的进位生成逻辑。Gi:i等同于Gi,表示当前位的和,而Pi:i则表示当前位的进位生成。递归公式Gi:j=Gi:k+Pi:kGk-1:j和Pi:j=Pi:kPk-1:j用于计算这些值,其中G0:0=Cin,Pi:0=0。通过这些公式,可以计算出所有位的Si值,即和位,以及进位输出Ci,而无需逐位进行加法操作。

为了简化电路表示,全加器的结构可以抽象为黑色和白色单元。黑色单元代表递归表达式的电路实现,而白色单元则表示G逻辑产生电路,即用于计算Gi值的电路。通过不同的组合和优化,可以构建出不同结构的全加器,以平衡逻辑级数、扇出、布线通道数和延迟等关键性能指标。

在全加器设计中,等价型PG逻辑的新公式能够指导连线策略的调整,使得设计更为灵活,能够根据特定需求优化电路性能。例如,通过减少逻辑级数和改善布线布局,可以降低延迟并提高加法器的运算速度。此外,这种新公式还可能降低功耗,因为更有效的逻辑设计通常意味着更低的开关活动,从而减少能量消耗。

等价型PG逻辑为全加器设计提供了新的理论基础和实用工具,有助于在保持正确性的前提下,实现更高效、更优化的数字逻辑电路。这对于现代计算机系统、嵌入式设备和高性能计算平台来说至关重要,因为这些领域对计算速度、能效和面积效率有着极高的要求。

2020-12-01 上传

299 浏览量

点击了解资源详情

点击了解资源详情

2025-03-12 上传

weixin_38678773

- 粉丝: 4

最新资源

- 桌面玫瑰恶搞小程序,带给你不一样的开心惊喜

- Win7系统语言栏无法显示?一键修复解决方案

- 防止粘贴非支持HTML的Quill.js插件

- 深入解析:微软Visual C#基础教程

- 初学者必备:超级玛丽增强版源码解析

- Web天气预报JavaScript插件使用指南

- MATLAB图像处理:蚁群算法优化抗图像收缩技术

- Flash AS3.0打造趣味打地鼠游戏

- Claxed: 简化样式的React样式组件类

- Docker与Laravel整合:跨媒体泊坞窗的设置与配置

- 快速搭建SSM框架:Maven模板工程指南

- 网众nxd远程连接工具:高效便捷的远程操作解决方案

- MySQL高效使用技巧全解析

- PIC单片机序列号编程烧录工具:自动校验与.num文件生成

- Next.js实现React博客教程:日语示例项目解析

- 医院官网构建与信息管理解决方案