RTL低功耗设计的关键技术与策略

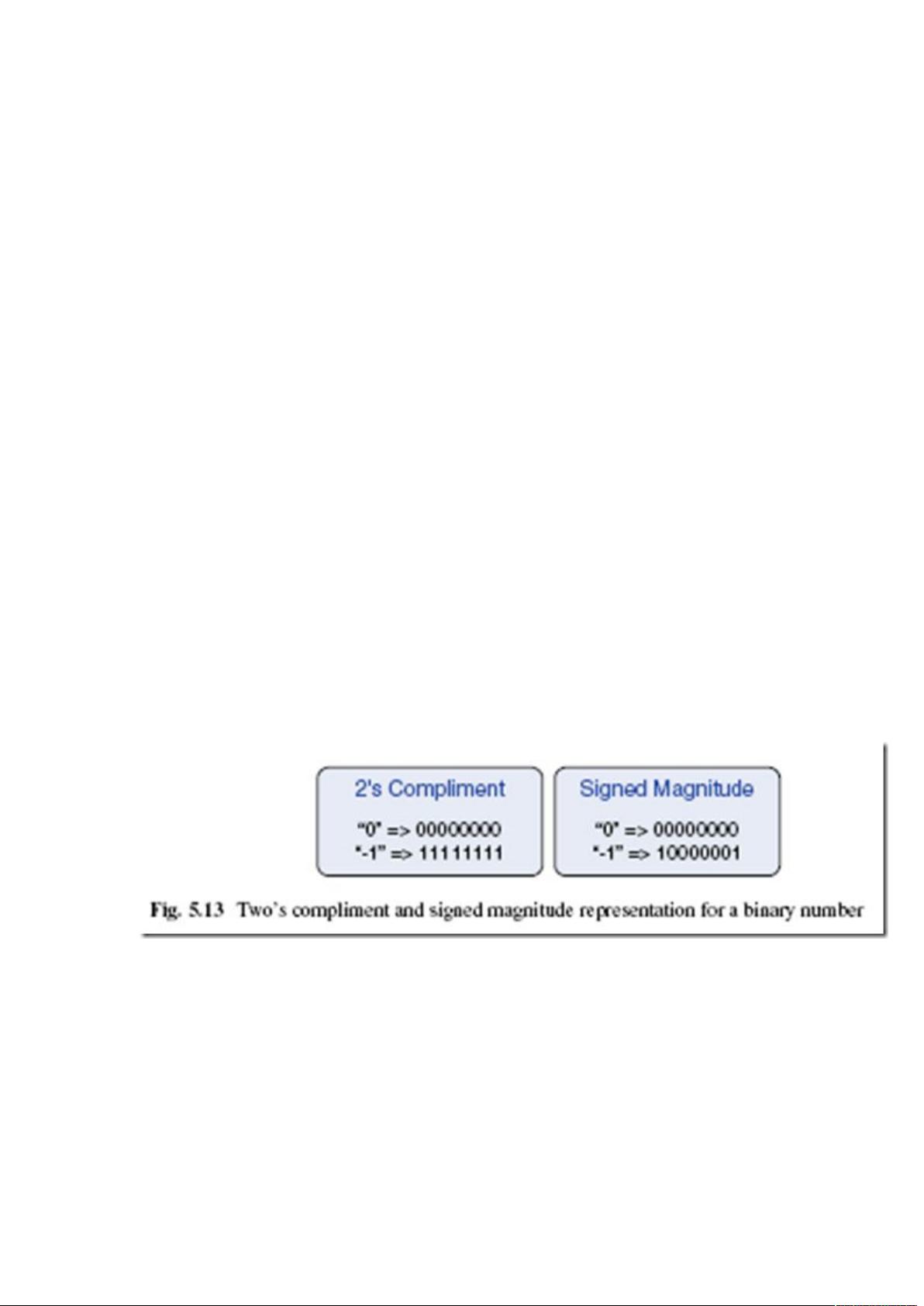

"RTL低功耗设计是芯片设计中的关键环节,大约80%的ASIC(Application Specific Integrated Circuit)在RTL阶段完成后,其功耗已经基本确定。因此,RTL级的低功耗设计对于整体芯片的能效至关重要。本文将探讨如何在RTL阶段通过不同的方法来实现有效的功耗降低。 低功耗设计主要关注动态功耗和静态功耗两个方面。动态功耗源于电路中晶体管的开关活动,而静态功耗主要来自漏电流。RTL编码风格和微架构设计对这两类功耗都有显著影响。因此,在合成前的RTL阶段就需要解决任何与功耗相关的问题。 一种常见的低功耗设计策略是状态机编码和分解。在各种状态机编码方式中,灰度编码(Grey Encoding)被认为是最适合低功耗设计的编码之一。与二进制编码相比,灰度编码降低了相邻状态之间的转换差异,从而减少了不必要的开关活动,进而减少动态功耗。如图5.12所示,二进制编码的状态机可能会有多于一个的 flip-flop 在状态转换时同时改变,而灰度编码则确保每次只有一个位变化,这样可以显著降低功耗。 除了状态机编码,还有其他技术可以在RTL阶段进行低功耗优化,例如: 1. **多电压域**(Multi-Voltage Domain):通过将芯片的不同部分分配到不同电压等级,可以针对不同功能块的功耗需求定制电源电压,从而降低功耗。 2. **电源门控**(Power Gating):在不需工作时,通过控制门控晶体管关闭特定电路的电源,以减少静态漏电流。 3. **时钟门控**(Clock Gating):仅在需要时才为特定逻辑路径提供时钟,避免无谓的时钟信号传播,降低动态功耗。 4. **功耗感知调度**(Power-Aware Scheduling):在设计过程中,考虑功耗影响,优化任务调度,减少不必要的计算。 5. **睡眠模式和唤醒机制**:通过设计睡眠模式,让芯片的部分或全部进入低功耗状态,然后在需要时快速唤醒,可以显著节省能量。 6. **自适应逻辑**(Adaptive Logic):根据工作负载和条件动态调整逻辑实现,以减少功耗。 7. **逻辑复用**(Logic Sharing):共享某些逻辑单元,减少重复的硬件资源,从而降低功耗。 在进行这些优化时,必须注意保持设计的可综合性和可验证性,确保低功耗设计不会引入新的功能错误或性能下降。此外,还需要利用专门的功耗分析工具进行实时功耗估计和优化,以便在设计早期就能捕捉到潜在的高功耗问题。 RTL级低功耗设计是现代芯片设计中不可或缺的一部分,通过采用适当的编码技术、电源管理策略以及功耗感知的设计方法,可以在不牺牲性能的前提下显著降低功耗,实现高效能、低功耗的集成电路。"

剩余14页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍

信息提交成功

信息提交成功