数字钟设计与仿真:同步电路方案解析

"简易数字钟设计,已完成仿真的通信工程与电子工程模电实验项目。"

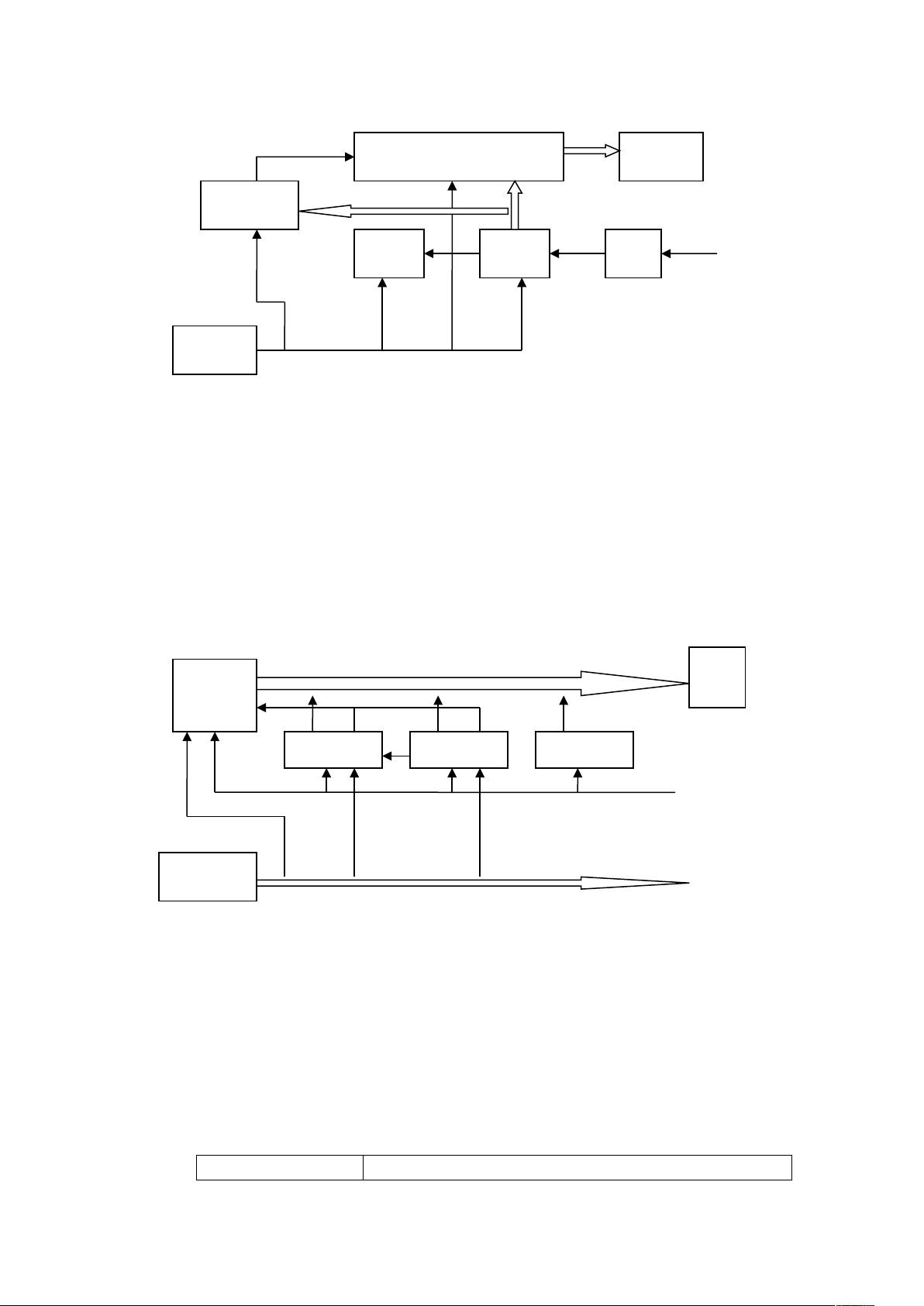

在数字钟的设计中,我们通常会面临多种设计方案的选择。在这个简易数字钟的设计案例中,作者陈晓炜从厦门大学通信工程系提出并比较了两种方案。首先,第一种方案是基于异步电路,通过数据选择器将时钟信号逐级传递给秒、分、时模块,进位信号在各级之间传递。虽然这个方案的模块内部结构相对简单,减少了额外的电路需求,但它的缺点在于系统结构不清晰,模块间关系复杂,外部需要更多的门电路,且因为是异步设计,存在计数溢出时即时进位的问题,这可能导致计时精度问题。

相比之下,第二种方案采用了同步电路和总线结构,时钟信号分别馈送给每个模块,使得各个模块保持相对独立,模块间连接简洁,便于未来功能的扩展。这种方案中,秒、分、时计数模块各自独立,进位信号通过总线传递,确保了系统的清晰性和稳定性。因此,作者选择了方案二作为最终设计。

设计过程中,秒和分计数器均以60进制工作,而时计数器则采用24进制。为了简化设计,秒和分计数使用了相同的计数单元。控制模块负责调整和显示切换,它由两部分组成:一部分处理时间的调整,另一部分处理不同时间显示的切换。

60进制模块(60count)是关键组件之一,它需要实现同步60进制计数,并具备可调整功能。该模块的接口包括电源输入(5V)、时钟信号输入(连接1Hz的信号源)以及进位输入。其他模块,如时钟信号分配、数据选择器、三态门用于控制数码管显示等,也是设计中不可或缺的部分,它们共同确保了数字钟的正常运行和功能实现。

在详细设计阶段,需要考虑所选芯片的特性,确保其满足设计需求。在EWB(Electronics Workbench)环境下进行仿真,验证设计的正确性。经过一系列的模块化设计、组合和调试,最终确保数字钟在仿真环境中能够准确计时、显示时间、调整时间,并实现整点报时和定时报闹等功能。

简易数字钟设计是一个综合运用模拟和数字电子技术的过程,涉及到电路设计、系统集成、时序逻辑等多个方面。通过对比分析和实际操作,可以提升工程师对电子系统设计的理解和实践能力。

252 浏览量

918 浏览量

点击了解资源详情

342 浏览量

1224 浏览量

918 浏览量

366 浏览量

1843 浏览量

650 浏览量

ywy6276339

- 粉丝: 0

- 资源: 11

最新资源

- SPI的定义.doc

- beginning-linux-programming.pdf

- C程序设计语言_第2版新版(清晰版)

- 基于DSP的AD频率变换的研究与实现

- 网络驱动程序设计指南

- 2007年Linux普及书籍从Windows转向Linux基础教程

- TOAD 快速入门 doc

- ATCOMMAND 命令大全

- Statspack-v3.0

- StartingStruts2online2.pdf

- Alfresco Enterprise Content Management Implementation.rar

- pb webservice

- 图书管理系统概要设计

- 教你制作widget

- 图书管理系统详细设计

- Java解惑-java初级知识分析