CD4046锁相环技术解析及应用

版权申诉

39 浏览量

更新于2024-08-03

收藏 357KB DOC 举报

"本文档介绍了倍频器的相关知识,特别是基于CD4046芯片的锁相环原理和应用。"

在电子技术中,倍频器是一种能够将输入信号频率成倍增加的设备,通常利用锁相环(Phase-Locked Loop, PLL)技术实现。锁相环的核心在于相位同步,它可以确保两个电信号在相位上保持一致。这种技术广泛应用于多个领域,如广播通信、频率合成、自动控制和时钟同步。

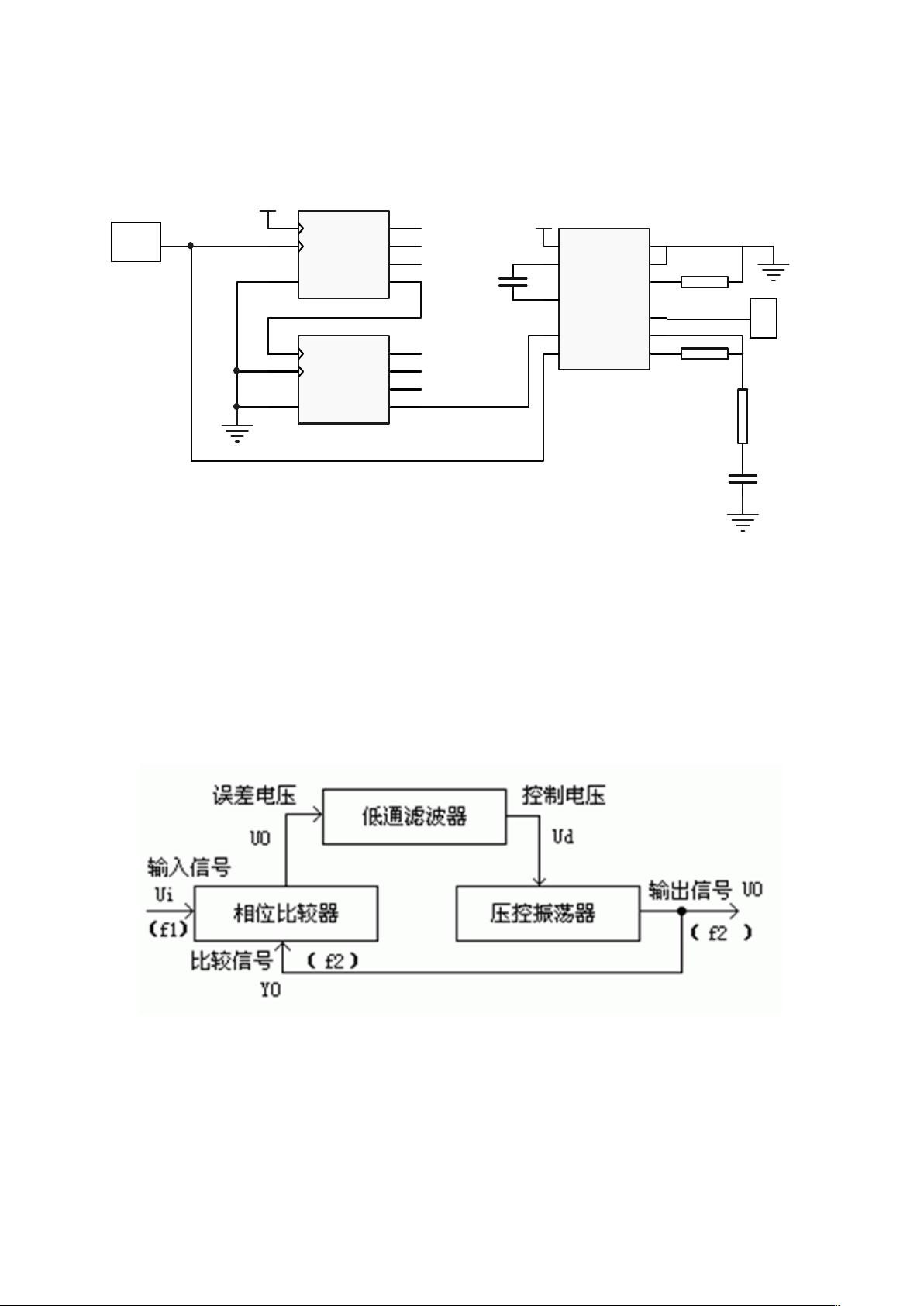

CD4046是一种通用的CMOS锁相环集成电路,设计特点是电源电压范围较宽(3V至18V),高输入阻抗(约100MΩ)以及低动态功耗。在10kHz的中心频率下,它的功耗只有600μW,因此被视为微功耗器件。CD4046芯片包含相位比较器、压控振荡器(VCO)和低通滤波器等基本组件,这些组件共同构成了锁相环的核心结构。

1. **相位比较器(PC)**:相位比较器接收来自VCO的输出信号Uo和外部输入信号Ui,比较两者之间的相位差。误差输出电压UΨ与这两个信号的相位差成正比。

2. **压控振荡器(VCO)**:VCO的输出频率受低通滤波器上建立的平均电压Ud控制。当Ud改变时,VCO的频率相应调整,目的是使VCO输出与输入信号的频率相匹配。

3. **低通滤波器**:低通滤波器的作用是滤除误差信号中的高频分量,仅保留平均值电压Ud。这个平均值电压引导VCO调整其输出频率,以实现相位锁定。

当锁相环进入锁定状态,即相位锁定时,VCO的频率会自动跟踪输入信号频率的变化。如果输入信号频率在锁相环的捕捉范围内变化,VCO能快速调整至新的频率,保持与输入信号同步。此外,通过外接运算器,可以进一步调整VCO输出与输入信号之间的关系,实现特定的频率比例或差值。

CD4046芯片有16个引脚,每个引脚都有特定的功能,例如:

- **相位输出端**(1脚):提供相位信息。

- **相位比较器输出端**(2脚和14脚):输出比较结果。

- **比较信号输入端**(3脚):连接外部输入信号。

- **压控振荡器输出端**(4脚):输出经过频率调节的信号。

- **禁止端**(5脚):高电平时禁用VCO,低电平时允许工作。

- **外接振荡电阻**(11脚和12脚):用于设置VCO的工作频率。

- **外接振荡电容**(6脚和7脚):调整VCO的频率特性。

- **信号输入端**(15脚):接收需要倍频的输入信号。

- **电源端**(8脚和16脚):提供电源电压。

了解CD4046芯片的工作原理和引脚功能,对于设计和调试基于锁相环的频率倍增系统至关重要。通过精确控制VCO的频率和调整环路参数,可以实现稳定且高效的频率倍增效果。

点击了解资源详情

124 浏览量

点击了解资源详情

2024-01-25 上传

2021-10-07 上传

264 浏览量

244 浏览量

153 浏览量

102 浏览量

cqtianxingkeji

- 粉丝: 3059

- 资源: 1630