FPGA设计高效技巧:乒乓操作、串并转换与流水线

需积分: 3 122 浏览量

更新于2024-12-22

收藏 208KB PDF 举报

"FPGA设计的四种常用思想与技巧"

在FPGA(Field-Programmable Gate Array)设计中,熟练掌握一些核心的思想与技巧能够极大地提高设计效率和系统的性能。本文将详细介绍乒乓操作、串并转换、流水线操作以及数据接口同步化这四种常用的设计方法。

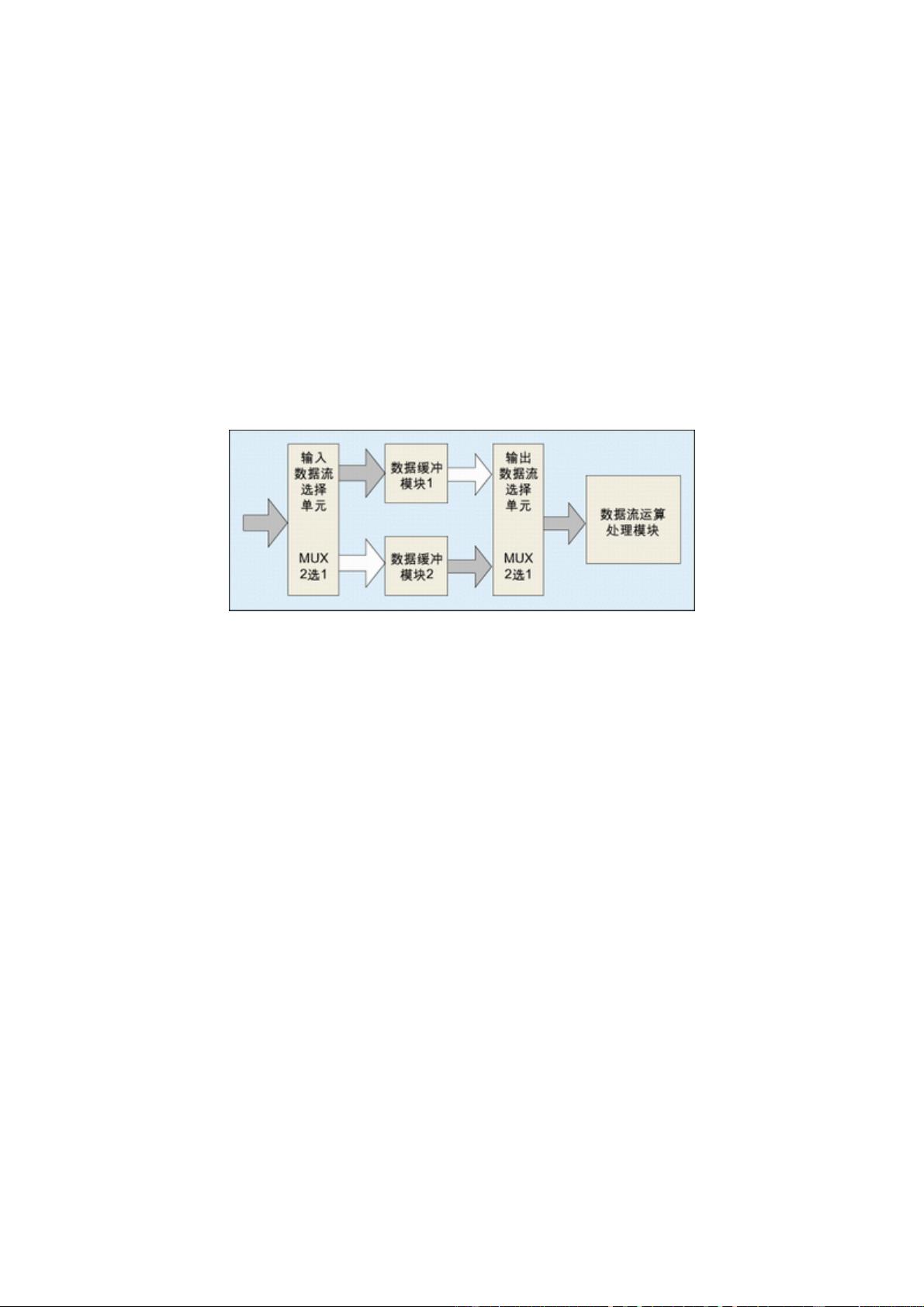

1. 乒乓操作:

乒乓操作是一种高效的数据处理策略,尤其适用于数据流控制。它通过两个交替使用的缓冲区(例如双口RAM或FIFO)来实现连续的数据流动。在一个缓冲周期,新的数据被写入一个缓冲区,而另一个缓冲区中的数据则被读出供处理。这种操作方式使得数据处理和新数据接收可以同时进行,提高了系统的吞吐率。乒乓操作在需要实时处理和连续数据流的应用中非常常见,例如在通信系统和视频处理中。

2. 串并转换:

串并转换(Serial-to-Parallel Conversion)是将连续的串行数据转换为并行数据流的过程,通常用于提升数据传输速度。在FPGA设计中,这可以通过串行接收器(Serial Receiver)和移位寄存器实现。当串行数据进入系统时,它可以被并行化以加速内部处理。反之,并行到串行转换(Parallel-to-Serial Conversion)则在输出数据时使用,以适应串行接口的需求。

3. 流水线操作:

流水线技术是FPGA设计中的重要优化手段,它通过将复杂的计算任务分解为多个阶段,每个阶段在独立的硬件模块中并行执行,从而提高系统性能。流水线操作可以显著减少延迟,因为每个阶段可以在上一阶段完成其任务的同时开始处理新的数据。在乒乓操作中,流水线处理尤为关键,因为它确保了数据的连续流动,避免了处理过程中的空闲时间。

4. 数据接口同步化:

在多模块系统中,数据接口同步化是保证系统稳定运行的关键。不同模块之间的数据交换需要遵循同一时钟域,以防止数据错乱和竞争条件。这通常通过使用锁相环(PLL)、分频器和同步器等时钟管理组件来实现。同步化设计可以确保数据在正确的时间到达正确的地点,从而避免错误和数据丢失。

这四种思想和技巧在FPGA设计中相辅相成,共同构建高效的数字系统。乒乓操作和流水线技术可以提高数据处理速度,串并转换优化数据传输,而同步化则确保整个系统的一致性和可靠性。理解和运用这些方法,设计师可以创建出满足高速、低延迟和复杂算法需求的FPGA解决方案。在实际设计中,还需要结合具体应用灵活运用这些技巧,以达到最佳的设计效果。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2009-01-14 上传

2023-02-26 上传

2012-07-04 上传

2023-02-26 上传

2021-09-18 上传

2023-02-27 上传

hcc041112

- 粉丝: 0

- 资源: 3

最新资源

- Java毕业设计项目:校园二手交易网站开发指南

- Blaseball Plus插件开发与构建教程

- Deno Express:模仿Node.js Express的Deno Web服务器解决方案

- coc-snippets: 强化coc.nvim代码片段体验

- Java面向对象编程语言特性解析与学生信息管理系统开发

- 掌握Java实现硬盘链接技术:LinkDisks深度解析

- 基于Springboot和Vue的Java网盘系统开发

- jMonkeyEngine3 SDK:Netbeans集成的3D应用开发利器

- Python家庭作业指南与实践技巧

- Java企业级Web项目实践指南

- Eureka注册中心与Go客户端使用指南

- TsinghuaNet客户端:跨平台校园网联网解决方案

- 掌握lazycsv:C++中高效解析CSV文件的单头库

- FSDAF遥感影像时空融合python实现教程

- Envato Markets分析工具扩展:监控销售与评论

- Kotlin实现NumPy绑定:提升数组数据处理性能