Verilog第四版EDA基础复习:FPGA与设计流程详解

需积分: 10 160 浏览量

更新于2024-07-27

1

收藏 3.18MB DOC 举报

本资源是一份针对《EDA技术实用教程-Verilog(第四版)》前两章的考试复习资料,主要涵盖以下几个核心知识点:

1. **EDA技术概论**:

- EDA技术是指电子设计自动化技术,它通过计算机辅助设计实现专用集成电路ASIC(如FPGA和CPLD)的设计和制造。FPGA和CPLD代表可编程专用集成电路,是EDA技术的重要应用,它们结合了软硬件设计、SoC(片上系统)和ASIC设计,支持自动设计和实现。

2. **EDA技术发展历史**:

- EDA技术经历了三个阶段:CAD(计算机辅助设计)、CAE(计算机辅助工程)和EDA阶段,分别对应70年代、80年代和90年代的技术进步。

3. **EDA技术目标与途径**:

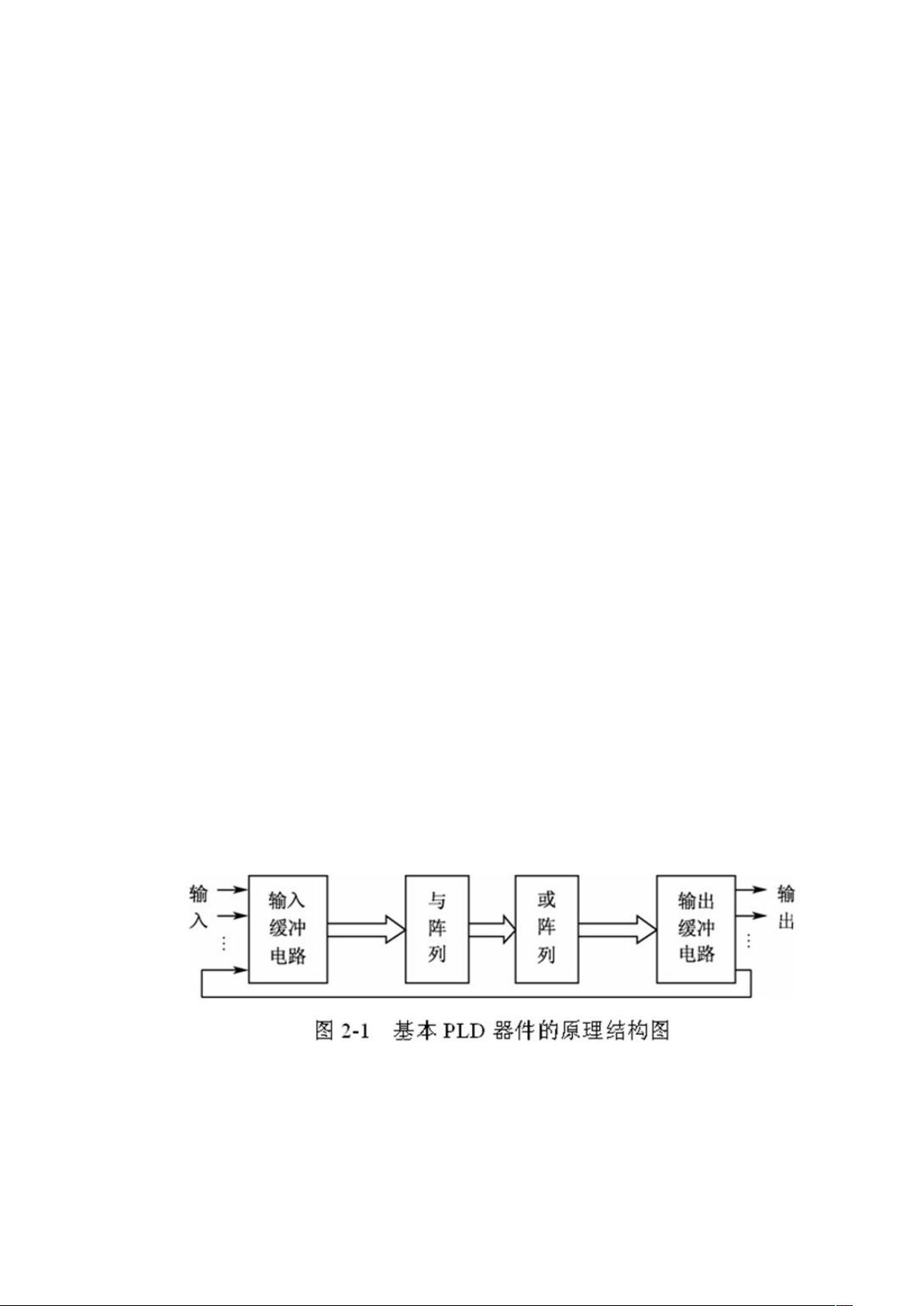

- 目标是设计并实现ASIC或PCB。通过可编程逻辑器件(如FPGA和CPLD)、半定制或全定制ASIC(如门阵列ASIC、标准单元ASIC和混合ASIC)来达到这个目标。

4. **硬件描述语言**:

- 主要提到了Verilog HDL,它是用于硬件设计的一种高级语言,由Gateway Design Automation公司于1983年创建,具有类似C语言的语法但区别明显,简洁易学且具有强大的电路描述和建模能力。

5. **Verilog HDL设计方法**:

- 介绍了Verilog HDL的设计流程,包括自顶向下和自底向上的设计方法,自顶向下的方法在效率和可靠性方面优于自底向上,成本较低。

6. **EDA设计流程**:

- 包括设计输入(图形输入和HDL文本输入)、综合、适配、时序与功能仿真以及最终的编程下载等步骤。

这份复习资料是针对学习者准备考试而编写的,详细解释了Verilog HDL的基础知识和EDA设计的基本概念,对于理解和掌握Verilog语言以及整个EDA设计过程非常有帮助。通过学习这部分内容,学生将能更好地应对考试,并理解如何在实际项目中运用这些技术。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2012-11-04 上传

282 浏览量

2019-06-08 上传

2022-06-20 上传

2021-11-09 上传

2021-10-10 上传

hxuhongming

- 粉丝: 5

- 资源: 7

最新资源

- redis-rb:Redis的Ruby客户端库

- odd-even-game:一个简单的游戏,用于在Angular中练习事件和组件

- 乐视网分析报告.rar

- puppeteer-next-github-actions:减少测试用例

- React-Amazon-Clone:具有React,Context Api,Firebase身份验证,PWA支持的Amazon Web App克隆

- secuboid-minecraft-plugin:Minecraft的土地,库存和悲伤保护插件

- ConnectJS-event-module:连接每个HTML元素的事件的简单方法

- ominfozone.ml

- smartwatch_transport:适用于公共交通的SmartWatch App

- CREATING-AND-HANDLING-A-DATABASE-IN-A-DEPARTMENT-STORE

- Python库 | django-metasettings-0.1.2.tar.gz

- Smite Loki Background Wallpaper New Tab-crx插件

- MorphoLibJ:ImageJ的数学形态学方法和插件的集合

- Apache OpenJPA 是 Jakarta Persistence API 3.0 规范的实现

- personal_site_of_deborah

- asp.net mvc学生选课成绩信息管理系统