四位超前进位加法器设计与优化

下载需积分: 19 | DOC格式 | 1.18MB |

更新于2024-09-12

| 169 浏览量 | 举报

"四位超进位加法器的设计报告,要求使用0.13um工艺,目的是训练学生的数字集成电路设计能力。设计内容包括四位加法器的原理图、HSPICE仿真、延迟计算以及器件尺寸优化。报告需包含设计过程、仿真结果分析、电路图、波形图和设计网表。使用的软件是HSPICE和COSMOS-SCOPE,参考书籍为阎石的《数字电子技术基础》。"

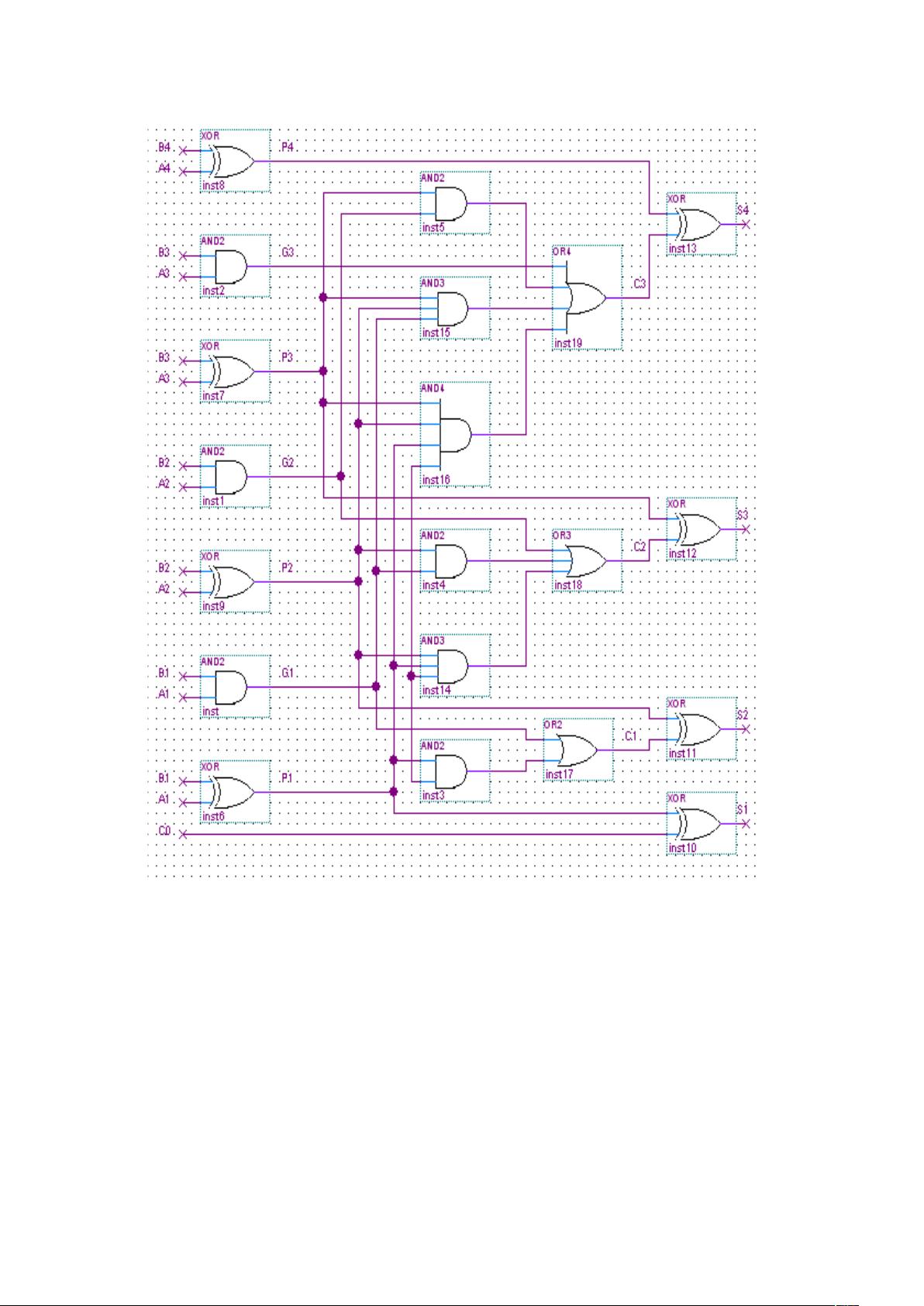

在数字集成电路领域,四位超进位加法器是一种用于实现二进制数字加法的电路。这种加法器能够处理四个二进制位的加法运算,并且具有超前进位功能,即在计算过程中提前生成进位信号,从而减少了输出延迟。超前进位加法器通常比传统的无超前进位加法器更快,因为它们可以在较低的层次上处理进位,提高整体计算速度。

课程设计的目标是让学生掌握并应用数字集成电路的基础知识,通过设计复杂的数字集成电路来提升实践技能。在这个项目中,学生需要设计一个四位超前进位加法器,使用0.13微米的半导体工艺,这是一种常见的微电子制造技术,可以实现高速、低功耗的电路。

设计过程中,学生需要按照指定格式书写报告,内容包括设计思路、HSPICE仿真网表、软件仿真的结果和分析、手动计算的延时等。此外,报告必须包含整体电路的原理图和仿真波形图,同时,对每个输入信号的波形和输出信号的测试结果进行说明。为了优化延时,学生需要手动计算确定晶体管尺寸,考虑输入端的电容Cinv和输出端的负载电容5000Cinv,选择一条路径进行优化。

全加器是超前进位加法器的基础,它不仅考虑本位的加法,还考虑了前一位的进位。在四位加法器中,每个全加器都会产生一个进位信号(Ci),这个信号将传递到下一个全加器作为输入。通过定义产生量Gi和传输变量Pi,可以简化逻辑表达式,构建出电路图。电路中包含不同类型的门电路,如2输入异或门、与门、或门,这些门电路用CMOS晶体管实现,包括PMOS和NMOS。

在HSPICE仿真中,学生需要提供设计的网表,确保仿真结果符合设计要求,并将仿真图形附在报告中。同时,报告的原创性也非常重要,重复的报告会被视为不及格。在整个过程中,阎石的《数字电子技术基础》提供了器件结构和参数的参考,而HSPICE和COSMOS-SCOPE是进行仿真和波形观察的必备工具。

通过这个课程设计,学生不仅学习了超前进位加法器的工作原理和设计方法,还掌握了数字集成电路的仿真和性能优化,这些都是成为专业电子工程师所必需的关键技能。

相关推荐

u011409031

- 粉丝: 0

最新资源

- Qt与QtWebkit打造简易浏览器应用 qt-webkit-kiosk项目介绍

- asp建站高效文件上传下载解决方案

- WebProject增量打包工具使用教程:配置Ant环境

- OpenGL实现三维物体自由旋转技术解析

- 局域网聊天应用:多用户功能与文件传输

- FiveM服务器加载屏:幻灯片过渡设计教程

- Unity 3D游戏开发教程:《泡泡龙》源码解析

- 在Vim中打造个性化状态栏:vim-crystalline插件介绍

- 测试驱动开发学习Emacs Lisp指南

- 安卓抽屉式菜单实现教程与效果展示

- VS环境下的SVN版本控制插件AnkhSvn实用介绍

- Java Struts在线考试系统实现与MySQL数据库集成

- 搭建离线地图服务器:Geoserver实践指南

- rufascube:开源3D魔方滑块拼图 - Ada编写的多平台益智游戏

- Macwire编译时依赖注入在Play Scala项目示例

- 手机仿海王星辰网上药店项目源代码完整分享